戦略的創造研究推進事業 CREST 研究領域「ディペンダブル VLSI システムの基盤技術」 研究課題「ロバストファブリックを用いたディペンダブル VLSI プラットフォーム」

研究終了報告書

研究期間 平成19年10月~平成26年3月

研究代表者:小野寺 秀俊 (京都大学大学院 情報学研究科、教授)

# §1 研究実施の概要

#### (1) 実施概要

微細化の限界に近づくにつれ、VLSIの製造性が急速に劣化するとともに、デバイス特性のばらつきが顕在化してきた。動作にともなう特性の劣化も深刻化している。回路中の電荷量の減少により雑音や宇宙線への耐性が低下している。これらの要因で発生する物理的、自然現象的フォールトはVLSIのディペンダビリティを毀損する深刻な原因である。ディペンダビリティ以外にも、VLSIシステムの持続的発展を阻害する要因として、マスクコストなどのNREコストの急騰が問題となっている。この問題を解決する有力候補が再構成可能VLSIである。同一のチップで、要求されるディペンダビリティの異なる多様なアプリケーションを効率よく実現することが、産業上強く求められている。

本研究では、素子寸法の極限的な微細化に伴って問題となってきたディジタル VLSI の製造性劣化や素子特性のばらつき、使用に伴う特性劣化、ならびに一過性雑音事象(ソフトエラー)によるディペンダビリティ低下を克服することを目的とし、回路技術からアーキテクチャまでの階層横断的取り組みにより搭載回路の再構成と特性の適応的調整が可能な VLSI プラットフォームを開発した。本プラットフォームは、再構成可能アレイとプロセッサで構成される。回路技術、再構成可能アーキテクチャ技術、設計自動化技術、プロセッサ構成技術の総合的取組により、要求されるレベルに応じたディペンダビリティを提供する組込みシステム用 VLSI プラットフォームを構築した。

「ロバストファブリック」グループでは、製造性劣化への対策と、特性ばらつきならびに特性劣化への対策に取り組んだ。レイヤー毎に必要とされる規則性を保ちつつプリミティブセル全体のレイアウト面積を最小化するセルレイアウト生成技術を開発した。特性ばらつきならびに特性劣化に対しては、ばらつきならびに劣化の正確な分析とモデル化を行うとともに、特性ばらつきの動的な補償を行う回路技術を開発した。

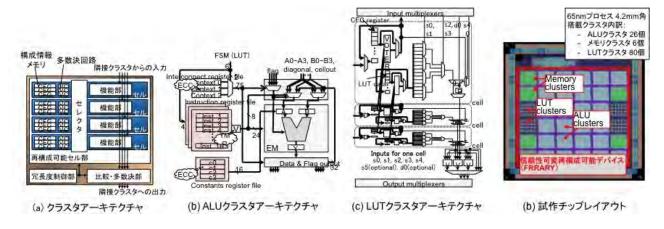

「再構成アーキテクチャ」グループは、構成要素毎に柔軟な冗長構成を実現することを可能とする粗粒度細粒度混合再構成可能アーキテクチャ FRRARY (Flexible Reliability Reconfigurable Array) を開発した。レジスタやメモリの実装、条件分岐やビット演算の実現方式について検討を進め、制御処理も含む実用的なアプリケーションが搭載可能である。FRRARY は、SRAM型 FPGA に対して構成情報量が少なくて済むため、SRAM型 FPGA では到底実現できない高いソフトエラー耐性が実現でき、耐放射線 FPGA であるアンチフューズ型 FPGA に対しては、FRRARY は先端 CMOS プロセスを用いて実装できるため、高い集積度を確保することができ、先進的なアプリケーションに利用できるという大きなアドバンテージを有する。

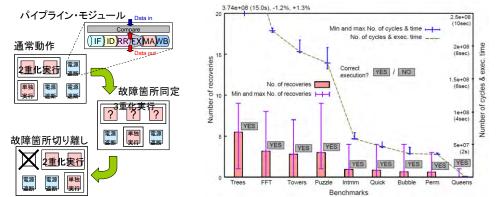

「再構成プロセッサ」グループは、高信頼化に必要なコストを削減するため、多重化度を動的に変更できる構造を考え、一時故障の発見/回復と永久故障の発見には2重化構成を、永久故障の回復には3重化構成を用いることで実行時の平均多重化度を削減するプロセッサ・アーキテクチャを開発した。回路レベルの高信頼化技術として、ソフトエラー耐性が数十倍高いフリップフロップを開発した。上記の二つの成果を適用した再構成プロセッサを試作し、アルファ線照射下においてもプロセッサが正常に動作することを確認した。

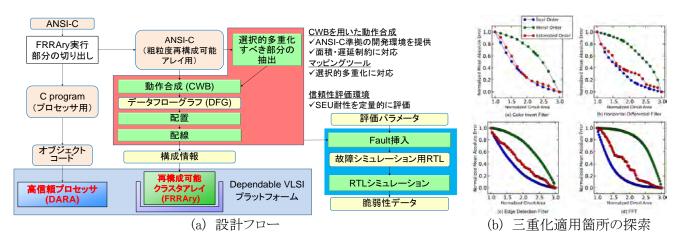

「マッピング技術」グループは、混合粒度再構成可能アーキテクチャと選択的三重化に注目し、与えられた 回路面積等の制約のもとで、ソフトエラー耐性を最大化すべく、三重化を適用する箇所を自動的に選択する 手法を開発した。データフローグラフの段階で適用可能な評価関数を開発し、これを用いることで最適な三 重化の適用箇所の探索を加速した。更に、粒度混合型 DFG マッピング機能を開発した。

「C 設計ツール技術」グループは、C 言語動作合成ツール CyberWorkBench を基盤ツールとして、FRRARY 向けの C 言語コンパイラを開発した。具体的には、マッピンググループが提示する空間的部分的多重化に加えて、ソフトエラー対策に有効な時間的多重化も実現した。

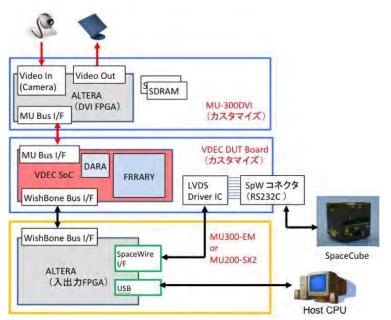

「アプリケーション展開のための評価・実用化検討」グループは、提案プラットフォームのチップ外部との入出力部分を設計した。SpaceWire を用いた高速シリアル通信方式の導入を検討し、再構成可能アレイとSpaceWire 通信の組み合わせで、リアルタイム画像処理や信号処理が実現できることを確認した。

これらの成果を踏まえ、全グループが協力してディペンダブル VLSI プラットフォームとして高信頼プロセッサも含めた SoC を開発した。並行して開発する評価ボードを用いて、提案粗粒度細粒度混合再構成可能アレイによるハードウェアアクセラレータとしての性能評価、高信頼度マッピングによる高いソフトエラー耐性の実現、ならびに柔軟な信頼性可変性を利用した小面積高信頼マッピングが実現できることを確認した。<u>本シリコン実装は、高い放射線耐性を有する混合粒度再構成可能デバイスの世界初の実証である。</u>

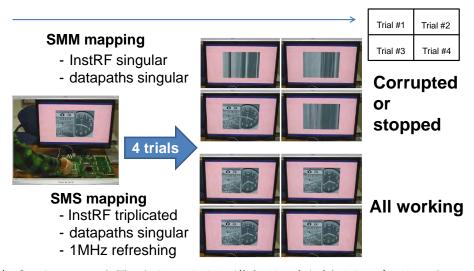

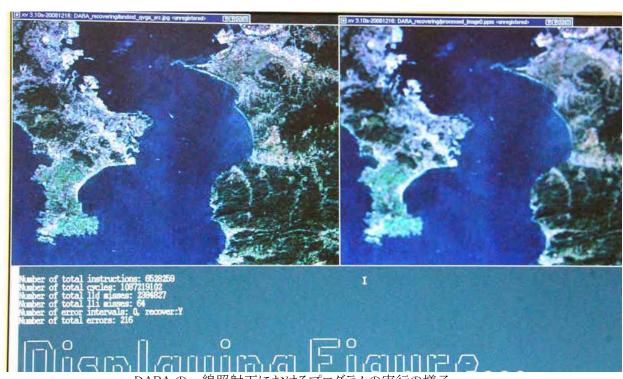

#### (2)顕著な成果

特に顕著な成果は、ディペンダブル VLSI プラットフォームとその評価環境の開発である。ディペンダブル VLSI プラットフォームのコンセプト実証回路として、信頼性可変再構成可能アーキテクチャ FRRARY と高信頼性プロセッサ DARAを65nm プロセスにて1チップ上に集積化した。また、動画像入出力インターフェイスを備えた評価環境を開発し、動画像アプリケーションに適用した場合の処理性能とディペンダビリティの評価を容易に行える評価ボードを開発した。本評価ボードを用いて、C言語で記述された画像処理やFFT などの各種アプリケーションが実行できる評価環境を整備した。これらを用いてリアルタイム画像処理をプラットフォーム上に実装し、高い放射線環境下で動作し続ける混合粒度再構成可能デバイスを世界で初めてシリコンで実証した(図1)。従来技術との比較において、本プラットフォームにより処理の高速化や圧倒的な高信頼化が達成できることや、ディペンダビリティを考慮した C言語からのコンパイルにより必要十分な信頼性を確保したハードウェアが実現できることを確認した。

図 1: 提案プラットフォームを用いたリアルタイム画像処理の実証例。同一デバイスにもかかわらず、高信頼マッピング(SMS; single modular with single context)では高い放射線下でも動作し続ける一方、通常マッピング(SMM; single modular with multicontext)では、直ちに回路故障が発生している。

## <優れた基礎研究としての成果>

1.

概要: (200 字程度)

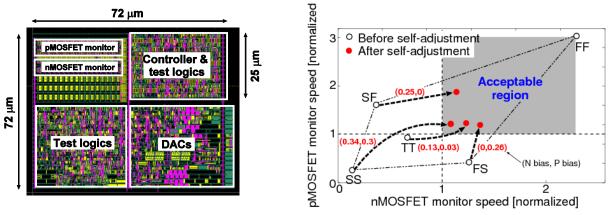

NMOSトランジスタとPMOSトランジスタの特性変動量を自己診断できる回路技術を開発した。診断回路を動的に再構成することで、チップ間ばらつき量と共にチップ内ばらつき量の診断も可能である.診断結果に基づいて基板バイアス電圧を調整することにより、変動したトランジスタ特性を所定の値に補正する回路技術も開発した。特性モニタや基板バイアス発生回路はセルベース設計で実装可能であり、補償対象回路中に埋め込むことができる。

2.

概要: (200 字程度)

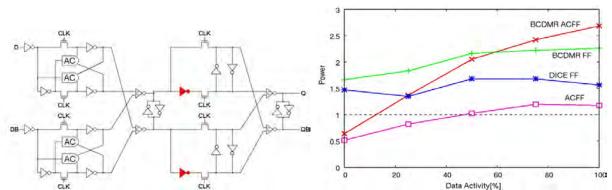

高い放射線耐性を有する BCDMR (Bistable Cross-coupled Dual-Modular Redundancy) FF の提案を行い、高いクロック周波数でも強靭なエラー耐性を持つことを、シミュレーションならびに実測(アルファ線、中性子線、重イオン照射加速試験)で実証した。さらに、電力低減を目的とした BCDMR ACFF (Adaptive Coupling FF)を開発し、その高い電力効率も実証した。

3.

概要: (200 字程度)

多重化度を動的に変更し、一時故障の発見/回復と永久故障の発見には 2 重化構成を、永久故障の

回復には 3 重化構成を用いることで平均多重化度を削減し、信頼性向上に要するコストを削減するプロセッサ・アーキテクチャ DARA(Dynamic Adaptive Redundancy Architecture)を開発した。従来は 3 重化構成が一般的であった永久故障についても 2 重化を基本とするため、電力コストを約 2/3 に削減した。

<科学技術イノベーションに大きく寄与する成果>

1.

概要: (200 字程度)

ディペンダブル VLSI プラットフォームのコンセプトを具現化したプロトタイプチップとその評価環境を構築した。高線量のα線をチップに照射した超過酷環境下での動画像処理デモンストレーションを通して、宇宙環境への適応性を実証した(先述図 1)。さらに、信頼性を考慮できる動作合成ツールと配置配線ツールを用いて、C 言語で記述された画像処理アプリケーションを異なる信頼性で実行できることを示した。本プラットフォームは宇宙機器開発の国産標準デバイスに最も近い位置にあり、今後の展開プロジェクトで産業応用への発展を目指している。

2.

概要: (200 字程度)

構成情報メモリと演算回路の冗長度を構成要素毎に自由に設定できる再構成可能アーキテクチャを提案し、そのプロトタイプチップを作成した。粗粒度構成要素と細粒度構成要素の混在アーキテクチャを採用することで、ハードウェアアクセラレーションだけでなく機器制御も可能となり、デバイスの応用分野を大きく拡大した。CMOS テクノロジによる揮発メモリ型再構成可能デバイスでありながら、高い耐放射線性能を有しており、フューズを用いたワンタイム再構成可能デバイスを、プロセス微細化による高集積化やコストの観点で圧倒している。

3.

概要: (200 字程度)

混合粒度再構成可能アーキテクチャと選択的三重化に注目し、与えられた回路面積等の制約のもとで、 ソフトエラー耐性を最大化すべく、三重化を適用する箇所を自動的に選択する手法を開発した。データ フローグラフの段階で適用可能な評価関数を開発し、これを用いることで最適な三重化の適用箇所の探索を加速した。また、選択的三重化により少ない面積オーバヘッドで効果的にソフトエラー耐性を高めることができる具体事例を例示した。

# § 2. 研究構想

- (1) 当初の研究構想、課題設定

- ①本研究の背景、社会や産業に存在する問題と本研究の課題設定

微細化の限界に近づくにつれ、VLSIの製造性が急速に劣化するとともに、デバイス特性のばらつきが顕在化してきた。動作にともなう特性の劣化も深刻化している。回路中の電荷量の減少により雑音や宇宙線への耐性が低下している。これらの要因で発生する物理的、自然現象的フォールトはVLSIのディペンダビリティを毀損する深刻な原因である。ITRS2009 ロードマップにおいても、設計部門(Design)における総合課題(合計 5項目)の2項目(製造容易化設計:design for manufacturability と信頼性:reliability)において、これらへの解決策探求の重要性が指摘されている。

ディペンダビリティ以外にも、VLSI システムの持続的発展を阻害する要因として、マスクコストなどの NRE コストの急騰が問題となっている。この問題を解決する有力候補が再構成可能 VLSI である。同一のチップで、要求されるディペンダビリティの異なる多様なアプリケーションを効率よく実現することが、産業上強く求められている。

本研究では、素子寸法の極限的な微細化に伴って問題となってきたディジタル VLSI の製造性劣化や素子特性のばらつき、使用に伴う特性劣化、ならびに一過性雑音事象(ソフトエラー)によるディペンダビリティ低下を克服することを目的とし、搭載回路の再構成と特性の適応的調整が可能な VLSI プラットフォームを開発す

る。

VLSI プラットフォームの開発にあたり、高信頼プロセッサと再構成可能アレイ部から構成される VLSI プラットフォームのハードウェアに加えて、C 言語で記載されたアプリケーションを開発 VLSI プラットフォーム上で実行させるためのソフトウェア環境を整備する。

#### ②本研究チームの達成目標

本研究の目標は、①で説明した微細化に伴う製造性の劣化、特性のばらつきと劣化、ソフトエラーといった物理的・自然現象的フォールトに対して高い耐性を有する再構成可能 VLSI プラットフォームを明らかにすることである。本プラットフォームでは、製造性を強化し特性ばらつきに対する靭性を高めたロバストファブリックを構成要素とすることにより製造性劣化や特性ばらつきに対応し、特性ばらつき量を等価的に半減することを目標とする。ソフトエラーや特性劣化に対しては、必要とされる信頼性に応じた冗長化構成やホットスワップが実現可能な粗粒度再構成可能アーキテクチャを開発し、宇宙空間においても 100FIT の故障率を達成することを目標とする。プラットフォームのハードウェアと共に、C 言語記載のアプリケーションが実行可能なソフトウェア環境を整備することにより、アプリケーション開発者自身がプラットフォームの評価を行うことが出来る環境を提供する。継続年度は、JAXA と密に連絡を取りながら、宇宙機向け国産次世代再構成可能アーキテクチャとその設計環境の開発に取り組する。

## ③本研究の特徴

本研究では、表 1 に示すディペンダビリティ阻害要因を対象として、回路技術からアーキテクチャまでの階層横断的取り組みにより各阻害要因を排除する技術を研究し、要求されるディペンダビリティに応じた回路を実現できる再構成可能 VLSI プラットフォームを開発する。本プラットフォームは、再構成可能アレイとプロセッサで構成する。回路技術、再構成可能アーキテクチャ技術、設計自動化技術、プロセッサ構成技術の総合的取組により、要求されるレベルに応じたディペンダビリティを提供する組込みシステム用 VLSI プラットフォームを構築する点に特徴がある。各要素技術についても、以下に示すように高い独自性と有用性を有している。ロバストファブリックの回路技術は、ばらつき耐性や放射線耐性の高いライブラリ構成技術そのものであり、一般的なセルベース設計に広く活用できる。再構成可能アーキテクチャは、様々な信頼性をハードウェアレベルで設定可能な世界初の再構成可能回路であり、通信回路や暗号処理などの様々なアプリケーションに適用できる。アプリケーションを再構成可能であり、通信回路や暗号処理などの様々なアプリケーションに適用できる。アプリケーションを再構成可能であり、通信回路や暗号処理などの様々なアプリケーションに適用できる。アプリケーションを再構成可能であり、通信回路や暗号処理などの様々なアプリケーションに適用できる。アプリケーションを再構成可能であり、通信回路や暗号処理などの様々なアプリケーションに適用できる。アプリケーションを再構成可能であり、通信回路や暗号処理などの様々なアプリケーションに適用できる。アプリケーションを再構成可能である。C 言語からプラットフォームへのマッピング手段を提供することにより、プラットフォームの実課題への適用可能性評価がユーザサイドで可能となる。プロセッサ構成技術についても、要求される信頼性に応じて、パイプラインステージ毎に誤り検出や訂正が実施可能な世界初のアーキテクチャを明らかにする。

| 表 1. ナイヘンダビリナイ阻害安区と、対心 9 合技術安全のよび阻害安区排除于法 |              |        |        |        |      |

|-------------------------------------------|--------------|--------|--------|--------|------|

| ディペン                                      | ンダビリティ阻害要因   | 製造性劣化  | 物理的揺らぎ | 一過性雑音  | 特性劣化 |

| 階層                                        | 技術要素         |        |        |        |      |

| ソフトウェア                                    | _            |        |        |        |      |

| アーキテクチャ                                   | 再構成可能アーキテクチャ |        |        | 0      | 0    |

| プロセッサ                                     | 再構成プロセッサ     |        |        | 0      | 0    |

| 設計自動化                                     | マッピング技術      |        |        | 0      | 0    |

| 回路技術                                      | ロバストファブリック   | 0      | 0      |        | 0    |

| デバイス技術                                    | _            |        |        |        |      |

| 阻                                         | 害要因排除手法      | 製造容易構造 | 自己調整   | 適応的冗長化 | 自己修復 |

表 1. ディペンダビリティ阻害要因と、対応する技術要素および阻害要因排除手法

### ④研究実施方法

1) 本研究チーム運営の方針、研究グループ間の分担・協力関係 本件チームは、表 1 に示す各要素技術を担当する「ロバストファブリック」「再構成アーキテクチャ」「再構成

プロセッサ」「マッピング技術」の各グループに加えて、H23 年の 6 月より加わった「C 設計ツール技術」と、本プラットフォームのアプリケーション展開に向けた「評価・実用化検討」グループで構成されている。各グループは担当課題の開発を主導するとともに、チーム全体としての階層横断的な取り組みによりディペンダブルVLSIプラットフォームの実現を目指す。すなわち、ロバストファブリックグループはディペンダブルVLSIプラットフォームを実現するためのライブラリを提供する。マッピング技術グループは、当該粗粒度再構成可能アーキテクチャを対象としたアプリケーションのマッピング技術を開発する。評価・実用化検討グループは、ディペンダブルVLSIプラットフォームの動作検証環境を整えると共に、具体的応用課題をプラットフォーム上に実現し、そのディペンダビリティを評価する。C設計ツール技術グループは、アプリケーションのC言語記述よりディペンダブルVLSIプラットフォームの機能・構造・動作記述を生成する。更に、DRP/STPといった動的再構成可能ハードウェア用のソフトウェア開発や多様なVLSIシステムの開発を通じて獲得した粗粒度再構成可能アーキテクチャに関する豊富な知見に基づき、再構成可能アレイのアーキテクチャやプロセッサとの連携方式などに関する検討に積極的に参加する。

継続のH25年度は「ロバストファブリック」「再構成アーキテクチャ」「マッピング技術」「C設計ツール技術」グループで研究を実施した。

# 2) 領域外部の企業等との連携

衛星搭載用組み込みシステム設計技術に関する情報交換を NEC 東芝スペースシステム社と実施し、宇宙用 FPGA の課題の明確化と宇宙用汎用 ASSP に必要とされる要件定義を実施した。東京大学の先端科学技術研究センターで開発されている地球観測用衛星が搭載しようとしている高度な情報処理能力を調査し、本研究の成果を発展させることで実現可能であることを明らかにした。宇宙衛星用組込みシステムに関する意見交換ならびにソフトエラー対策技術に関する技術討論を、JAXA の総合技術研究本部および宇宙科学研究本部の研究者と実施した。再構成アーキテクチャを次世代宇宙機向けのヘテロジニアスなネットワーク実現に応用する方法について検討を進めた。また、JAXA の総合技術研究本部の協力のもと、耐放射線フリップフロップのソフトエラー耐性を評価するための重イオンを用いた加速テストを実施した。再構成可能アーキテクチャを中心としたディペンダブル VLSI プラットフォームに関する情報交換を、ルネサスエレクトロニクス社と NEC 社で動的再構成デバイスの商品化開発を担当するグループと行った。再構成可能アーキテクチャならびにソフトエラー対策技術に関する情報交換を、日立製作所生産技術研究所において高信頼化技術を担当しているグループと実施した。

ソフトエラーに焦点を絞った技術討論会を 2011 年 9 月に京都工芸繊維大学で開催し、JAXA、日立製作所、富士通セミコンダクタ、ルネサスエレクトロニクスなどに所属する日本を代表するソフトエラー関係の研究者と情報交換するとともに、今後の連携可能性について協議した。2012 年 9 月には第 2 回の技術討論会を福岡システム LSI 総合開発センターにて開催、2013 年 8 月には第 3 回の技術討論会を広島市立大学にて開催した。今後も当該技術領域に特化した国内唯一の技術情報交換と連携の場として活動を継続する事を確認した。さらに SpaceWire ユーザ会に参加し、公開頂いた SpaceWire IP を用いたリアルタイム動画転送への適用を市販 FPGA ボードを用いて評価し、再構成可能 VLSI プラットフォームへの統合を進めた。本研究で得られた知見をもとに、SpaceWire ネットワークで生ずる Blocking の問題を解決すべく、JAXA の宇宙科学研究所と共同で Non-Bloking ルーターIP を開発した。

#### 3) 領域内他研究チームとの連携関係

平成 22 年度までは「VLSI ディペンダビリティの物理・デバイス・回路レベルテスト構造フォーラム」を開催し、特に TEG(Test Element Group)の設計や評価技術に関する情報交換を領域内の多くの研究チームの間で実施した。平成 23 年度からは、上記 2)で説明したソフトエラーに関する技術討論会を開催し、安浦チームや吉本チームなど領域内でソフトエラーに関する研究を行っているチームからの参加者も得て、ソフトエラーに関する技術討論と研究連携に関する議論を行った。

- (2)新たに追加・修正など変更した研究構想、発展テーマ

- ① 中間評価で受けた指摘や助言、それを踏まえて対応した結果について 中間評価会での指摘(一部):

- プログラムツールなどの開発環境が十分整備されるということを前提として。

- ・再構成プロセッサを現実に世の中で使わる状況に持っていく道を確立するためには、様々ツールチェーン 等含めた膨大な環境整備が必要になる面があります。変更内容:

- C 設計ツール技術グループの新設による C 言語の動作記述から粗粒度再構成可能アーキテクチャへの自動マッピング環境の構築

- ② 中間報告書§6. 今後の研究の進め方、および研究成果の見通しの記載事項に関し、研究を進めた結果について

当初計画になかった重要かつ新規な展開として、上記のC設計ツール技術グループの新設とともに、粗粒度再構成可能アーキテクチャ FRRARY の改良が挙げられる。当初計画では、FRRARY ではストリーミング処理の高速化を実現し、条件分岐などの制御処理は高信頼プロセッサで実現する方式を想定していた。しかしながら、DRP などの粗粒度動的再構成可能アレイの開発を主導したC設計ツール技術グループの新規加入に伴い、プロセッサと FRRARY の処理分担に関する精査を行った。その結果、制御構造をもたないデータ処理系部分のみを FRRARY にて処理するだけでは、高速化できるCプログラムが GPGPU のような SIMD 系プロセッサと同様の狭い範囲に限定されてしまうことが判明した。そこで、条件分岐などの制御構造を含むより大きなプログラムを FRRARY で実行できるように、アーキテクチャや設計環境を大幅に変更した。これにより、GPGPU では加速できないような判断を多く含む処理の高速化も可能となった。また、本変更により CPU との通信量を削減するような SW-HW (FRRARY)分割が可能となるため、更なる高速化が図れる。通信制御等に適用することも可能となった。

ビット処理や論理演算などの細粒度処理機能についても改良を施した。その結果、FPGA等の細粒度再構成可能アーキテクチャの利点(ビット処理や論理演算処理が高効率)と、STP等の粗粒度再構成可能アーキテクチャの利点(算術演算が高効率)の双方を両立させたアーキテクチャにすることができた。

FRRARY 用の C 言語コンパイラも、実績のある既存の動作合成ツール(CyberWorkBench)を改良する方向へ変更したため、当初計画と比べ格段に実用的な回路への適用が可能となった。FRRARY が大規模化した場合を想定して、非常に複雑な実用レベルの C プログラムを FRRARY で実行した場合の性能等も予測できるようになる。その過程の合成実験を通じ、動作合成と論理合成ツールの役割分担、アーキテクチャとの連携、デバッグ性、テスト容易性の議論等、実用的な利用方法に関する議論が進んだ。

これらの改良により、FRRARY の用途が格段に汎用化し、ディペンダビリティを担保しつつ高速高性能化を図るという方向性への端緒をひらくことができた。

- ③ 上記①②以外で生まれた新たな展開について

- ディペンダブル VLSI プラットフォーム SoC の動画像アプリケーション評価によって、以下の課題が明確化した。

- (1) 条件分岐などの制御構造を実装において粗粒度要素と細粒度要素の柔軟性およびハードウェアリソースが限られているため、実装できるアプリケーション規模に制約がある。また、設計ツールを用いたアプリケーション実装もツールへの熟練を要する。

- (2) 処理性能に関する検討が不足しているところがあり、粗粒度要素によるアクセラレーション性能を十分に活かすことができていない。

これらの課題を解消するため、対策案について再構成可能アーキテクチャグループ、マッピンググループ、C言語ツールグループ、アプリケーション展開グループで総合的に検討し、プロジェクト期間内でのアーキテクチャ改良と設計ツール改良を実施した。具体的内容を表 2(2013 年度版)に示す。回路動作の高速化を目指し MUX が少ないアーキテクチャへの改良、配線容易性とツール親和性のため配線構造の刷新、条件分岐処理のマッピング効率改善、実装可能状態数の向上を行うとともに、SpaceWire 等の宇宙機器向け要件の取り込みを行った。

表 2: 再構成可能アーキテクチャの進化

|                  | 初期版                             | 2012年版                                | 2013年版(現行)                                      |                                        |

|------------------|---------------------------------|---------------------------------------|-------------------------------------------------|----------------------------------------|

| 技術特徴             | 算術演算の並列実<br>行                   | 条件分岐等の制<br>御構造を含んだC<br>プログラムの並列<br>実行 | 信頼性レベルを維持<br>しながら、高速化と省<br>面積化を実現               | 算術、論理演算の逐次が<br>(複合演算)の高速化              |

| アーキテ<br>クチャ      | ALUアレイ(粗粒<br>度)                 | ALU+LUT(粗·細<br>粒度混載)                  | 配線構造、演算器・M<br>UX構造を大幅改良                         | ALUを、多入力、複合AL                          |

| 適用分野             | HWアクセラレータ<br>(CPUが苦手な処<br>理の加速) | クロックタイミング<br>を意識した設計、<br>制御系も対応       | 宇宙機など、<br>高い耐放射線性能が<br>求められる分野                  | 条件分岐等含んだ複雑<br>ルゴリズムを高周波数で<br>行         |

| アプリ<br>ケーショ<br>ン | フィルタ、FFT等                       | 左に加え、<br>ネットワーク系、<br>LCD等の機器制<br>御    | 左に加え、より高性能、<br>省面積な画像処理系<br>および制御系              | 顔照合、スーパーハイビンのCODEC等複雑なアルズムをより高性能に実行    |

| 特記事項             |                                 |                                       | 宇宙向け改良として、<br>大幅な性能改善、<br>ツール改良、<br>SpaceWire対応 | 衛星に必要な全機能を<br>チップで実行可能<br>(CPU機能の代替も含む |

# §3 研究実施体制

- (1)研究チームの体制について

- (1)「京都大学」グループ

- ①研究参加者

| 氏名                    | 所属         | 役職  | 参加時期         |

|-----------------------|------------|-----|--------------|

| 小野寺 秀俊                | 京都大学情報学研究科 | 教授  | H19.10~H26.3 |

| 佐藤 高史                 | 京都大学情報学研究科 | 教授  | H21.4~H25.3  |

| 越智 裕之                 | 京都大学情報学研究科 | 准教授 | H19.10~H25.3 |

| 土谷 亮                  | 京都大学情報学研究科 | 助教  | H19.10~H26.3 |

| 筒井 弘                  | 京都大学情報学研究科 | 助教  | H22.4~H25.3  |

| 松本 高士                 | 京都大学情報学研究科 | D3  | H21.4~H26.3  |

| Islam A.K.M. Mahfuzul | 京都大学情報学研究科 | D3  | H21.4~H26.3  |

| 古田 潤                  | 京都大学情報学研究科 | D3  | H21.4~H26.3  |

| 西澤 真一                 | 京都大学情報学研究科 | D3  | H21.4~H26.3  |

| 釜江 典裕                 | 京都大学情報学研究科 | D2  | H22.4~H26.3  |

| 金 信寧                  | 京都大学情報学研究科 | D3  | H24.4~H26.3  |

| 陳 世鵬                  | 京都大学情報学研究科 | M2  | H23.4~H25.3  |

| 三木 淳司                 | 京都大学情報学研究科 | M2  | H23.4~H25.3  |

| 小宮山 敦史                | 京都大学情報学研究科 | M2  | H24.4~H25.3  |

| 近藤 正大                 | 京都大学情報学研究科 | M2  | H24.4~H26.3  |

| 西村 彰平                 | 京都大学情報学研究科 | M2  | H24.4~H26.3  |

| 修 斉                  | 京都大学情報学研究科 | M2  | H24.4~H26.3  |

|----------------------|------------|-----|--------------|

| 竹下 俊宏                | 京都大学情報学研究科 | M1  | H25.4~H26.3  |

| 中西 晋一                | 京都大学情報学研究科 | M1  | H25.4~H26.3  |

| 三木 崇史                | 京都大学情報学研究科 | M2  | H21.4~H23.3  |

| 今川 隆司                | 京都大学情報学研究科 | D3  | H20.4~H25.3  |

| 川島 潤也                | 京都大学情報学研究科 | M2  | H23.4~H25.3  |

| 森下 拓海                | 京都大学情報学研究科 | M2  | H23.4~H25.3  |

| 池辺 卓                 | 京都大学情報学研究科 | M2  | H23.4~H25.3  |

| 粟野 皓光                | 京都大学情報学研究科 | M2  | H23.4~H25.3  |

| 李 志                  | 京都大学情報学研究科 | M1  | H23.10~H25.3 |

| 張 詩翼                 | 京都大学情報学研究科 | M1  | H23.10~H25.3 |

| 関 良平                 | 京都大学情報学研究科 | M2  | H19.10~H20.3 |

| 福岡 孝之                | 京都大学情報学研究科 | M2  | H19.10~H20.3 |

| 寺田 晴彦                | 京都大学情報学研究科 | M2  | H19.10~H21.3 |

| 久米 洋平                | 京都大学情報学研究科 | M2  | H20.4~H21.3  |

| 砂川 洋輝                | 京都大学情報学研究科 | M2  | H20.4~H22.3  |

| 牧野 紘明                | 京都大学情報学研究科 | M2  | H20.4~H22.3  |

| 伊東 恭佑                | 京都大学情報学研究科 | M2  | H21.4~H23.3  |

| 北島 和彦                | 京都大学情報学研究科 | M2  | H22.4~H24.3  |

| 藤本 秀一                | 京都大学情報学研究科 | M2  | H22.4~H24.3  |

| 神山 真一                | 京都大学情報学研究科 | D3  | H19.10~H20.3 |

| TRAN, Son Phu        | 京都大学情報学研究科 | M2  | H19.10~H20.3 |

| 山口 典昭                | 京都大学情報学研究科 | M2  | H19.10~H21.3 |

| 武智 翔吾                | 京都大学情報学研究科 | M2  | H19.10~H21.3 |

| RAKOSI, Zoltan Endre | 京都大学情報学研究科 | M2  | H20.4~H22.3  |

| 藤中勇成                 | 京都大学情報学研究科 | M2  | H20.4~H22.3  |

| 萩原 汐                 | 京都大学情報学研究科 | D3  | H21.4~H23.3  |

| 寺岡 秀人                | 京都大学情報学研究科 | M2  | H21.4~H23.3  |

| 大上 崇博                | 京都大学情報学研究科 | M2  | H21.4~H23.3  |

| 高橋 知之                | 京都大学情報学研究科 | M2  | H21.10~H22.3 |

| 小崎 忠道                | 京都大学情報学研究科 | M2  | H22.4~H24.3  |

| 湯浅 洋史                | 京都大学情報学研究科 | M2  | H22.4~H24.3  |

| 小林 和淑                | 京都大学情報学研究科 | 准教授 | H19.10~H21.3 |

| 嶋田 創                 | 京都大学情報学研究科 | 助教  | H19.10~H21.3 |

| 姚 駿                  | 京都大学情報学研究科 | 研究員 | H19.10~H21.3 |

| 廣本 正之                | 京都大学情報学研究科 | 研究員 | H19.10~H22.3 |

| 上薗 巧                 | 京都大学情報学研究科 | 研究員 | H21.4~H23.3  |

| Bishnu Prasad Das    | 京都大学情報学研究科 | 研究員 | H21.10~H24.5 |

# ②研究項目

- ・ロバストファブリック

- ・再構成可能ディペンダブル VLSI へのマッピング技術

# (2)阪大グループ

# ①研究参加者

| 氏名    | 所属          | 役職 | 参加時期         |

|-------|-------------|----|--------------|

| 尾上 孝雄 | 大阪大学情報科学研究科 | 教授 | H19.10~H26.3 |

| 橋本 昌宜           | 大阪大学情報科学研究科 | 准教授   | H19.10~H26.3 |

|-----------------|-------------|-------|--------------|

| 密山 幸男           | 大阪大学情報科学研究科 | 助教    | H19.10~H23.3 |

| 更田 裕司           | 大阪大学情報科学研究科 | D2    | H19.10~H22.3 |

| 高 永勲            | 大阪大学情報科学研究科 | M2    | H19.10~H21.3 |

| 濱本 浩一           | 大阪大学情報科学研究科 | M2    | H19.10~H21.3 |

| 天木 健彦           | 大阪大学情報科学研究科 | D1    | H20.4~H24.3  |

| 原田 諒            | 大阪大学情報科学研究科 | D3    | H21.4~H26.3  |

| 郡浦 宏明           | 大阪大学情報科学研究科 | D3    | H21.4~H26.3  |

| Dawood Alnajjar | 大阪大学情報科学研究科 | D3    | H20.4~H25.3  |

| 亀田 敏広           | 大阪大学情報科学研究科 | M1    | H22.4~H.24.3 |

| 楊贇              | 大阪大学情報科学研究科 | 特任研究員 | H23.2~H24.3  |

| 阿部 慎也           | 大阪大学情報科学研究科 | M2    | H19.10~H21.3 |

# ②研究項目

・ディペンダブル VLSI プラットフォーム用再構成可能 VLSI アーキテクチャ

# (3)京都高度技術研究所グループ

# ①研究参加者

| 氏名    | 所属           | 役職                    | 参加時期         |

|-------|--------------|-----------------------|--------------|

| 神原 弘之 | 京都高度技術研究所    | 主席研究員                 | H19.10~H26.3 |

| 奥畑 宏之 | 京都高度技術研究所    | 研究員((株)シンセ<br>シスより出向) | H20.12~H24.3 |

| 伊勢 正尚 | 京都高度技術研究所    | 研究員((株)シンセ<br>シスより出向) | H20.12~H22.3 |

| 大巻 裕治 | 京都高度技術研究所    | 研究員((株)シンセ<br>シスより出向) | H20.12~H24.3 |

| 渡邊 賢治 | 京都高度技術研究所    | 研究員((株)シンセ<br>シスより出向) | H21.4~H24.3  |

| 金城 良太 | 京都大学         | 研究補助員(M2)             | H20.2~H22.3  |

| 戸田 勇希 | 関西学院大学       | 研究補助員(M2)             | H20.2~H22.3  |

| 笹山 瑛由 | 京都大学         | 臨時雇用(M2)              | H20.4~H20.10 |

| 矢野 昭治 | 京都大学情報学研究科   | 研究補助員(M2)             | H20.4 ∼H26.3 |

| 田村 真平 | 関西学院大学理工学研究科 | 研究補助員(M1)             | H23.4~H26.3  |

| 山下 真司 | 関西学院大学理工学研究科 | 研究補助員(M1)             | H23.4~H26.3  |

| 高島 史明 | 関西学院大学理工学研究科 | 研究補助員(M1)             | H22.4~H24.3  |

| 織野 真琴 | 関西学院大学理工学研究科 | 研究補助員(M1)             | H22.4~H25.3  |

| 武田 晃一 | 関西学院大学       | 臨時雇用者(M1)             | H20.4~H21.3  |

| 杉原 有理 | 京都大学情報学研究科   | 臨時雇用者(M2)             | H20.2~H20.3  |

| 松崎 裕樹 | 立命館大学        | 臨時雇用者(M2)             | H20.2~H20.3  |

| 西村 啓成 | 関西学院大学       | 臨時雇用者(M2)             | H20.3~H20.3  |

| 廣本 正之 | 京都大学情報学研究科   | 臨時雇用者(D1)             | H20.3~H20.3  |

| 菅野 裕輝 | 京都大学情報学研究科   | 臨時雇用者(D1)             | H20.3~H20.3  |

# ②研究項目

・ディペンダブル VLSI プラットフォームのアプリケーション展開に向けた評価・実用化検討

# (4) 奈良先端大グループ

# ①研究参加者

| 氏名                   | 所属                       | 役職  | 参加時期          |

|----------------------|--------------------------|-----|---------------|

| 嶋田 創                 | 奈良先端科学技術大学院大学情<br>報科学研究科 | 准教授 | H21.4~H25.3   |

| 姚 駿                  | 奈良先端科学技術大学院大学情<br>報科学研究科 | 助教  | H21.4~H25.3   |

| 渡邊 良二                | 奈良先端科学技術大学院大学情<br>報科学研究科 | M2  | H21.9~H23.3   |

| 竹迫 晴之                | 奈良先端科学技術大学院大学情<br>報科学研究科 | M1  | H22.10~H22.11 |

| 狭間 良平                | 奈良先端科学技術大学院大学情<br>報科学研究科 | M2  | H22.10~H24.3  |

| Yuttakonkit Yuttakon | 奈良先端科学技術大学院大学情<br>報科学研究科 | M1  | H24.10~H25.3  |

# ②研究項目

再構成プロセッサ

# (5)京都工繊大グループ

# ①研究参加者

| 氏名      | 所属                               | 役職 | 参加時期        |

|---------|----------------------------------|----|-------------|

| 小林 和淑   | 京都工芸繊維大学大学院工芸科学研究科電子システム工学専攻     | 教授 | H21.4~H25.3 |

| 藪内 美智太郎 | 京都工芸繊維大学大学院工芸科 学研究科電子システム工学専攻    | D1 | H22.4~H25.3 |

| 濱中 力    | 京都工芸繊維大学大学院工芸科学研究科電子システム工学専攻     | M2 | H21.4~H23.3 |

| 山本 亮輔   | 京都工芸繊維大学大学院工芸科 学研究科電子システム工学専攻    | M2 | H22.4~H24.3 |

| 石井 翔平   | 京都工芸繊維大学大学院工芸科学研究科電子システム工学専攻     | M2 | H23.4~H25.3 |

| 岡田 翔伍   | 京都工芸繊維大学大学院工芸科 学研究科電子システム工学専攻    | M2 | H23.4~H25.3 |

| 久保田 勘人  | 京都工芸繊維大学大学院工芸科 学研究科電子システム工学専攻    | M2 | H23.4~H25.3 |

| 増田 政基   | 京都工芸繊維大学大学院工芸科学研究科電子システム工学専攻     | M2 | H23.4~H25.3 |

| 張 魁元    | 京都工芸繊維大学大学院工芸科 学研究科電子システム工学専攻    | M2 | H23.4~H25.3 |

| 万沢 勇貴   | 京都工芸繊維大学大学院工芸科<br>学研究科電子システム工学専攻 | M1 | H24.4~H25.3 |

| 谷弘 脩一   | 京都工芸繊維大学大学院工芸科<br>学研究科電子システム工学専攻 | M1 | H24.4~H25.3 |

# ②研究項目

・ディペンダブル VLSI プラットフォーム信頼性向上技術の検討

# (6)「高知工科大学」グループ

①研究参加者

| 氏名    | 所属             | 役職  | 参加時期        |

|-------|----------------|-----|-------------|

| 密山 幸男 | 高知工科大学システム工学群  | 准教授 | H23.4~H26.3 |

| 森岡 俊樹 | 高知工科大学大学院工学研究科 | M1  | H25.7~H26.3 |

| 原 浩彰  | 高知工科大学大学院工学研究科 | M1  | H25.7~H26.3 |

#### ②研究項目

・ディペンダブル VLSI プラットフォーム用高信頼性インタフェースの研究

#### (7)「NEC」グループ

### ①研究参加者

| 氏名    | 所属                    | 役職    | 参加時期        |

|-------|-----------------------|-------|-------------|

| 若林 一敏 | NEC グリーンプラットフォーム研究所   | 主幹研究員 | H23.7~H26.3 |

| 竹中 崇  | NEC グリーンプラットフォーム研究所   | 主任研究員 | H23.7~H26.3 |

| 貞方 毅  | NEC システムIPコア研究所       | 主任    | H23.7~H24.3 |

| 春田 泰睦 | NEC 組込みシステムソリューション事業部 | マネージャ | H23.7~H23.9 |

| 野田 真一 | NEC グリーンプラットフォーム研究所   | 主任    | H24.4~H25.3 |

| 中村 寿彦 | NEC 共通ソリューション開発本部     | 主任    | H24.4~H26.3 |

# ②研究項目

- ・ 再構成アレイ向け合成ツール

- •部分的多重化技術

- 全体コンサルティング

#### (7) 「立命館大学」グループ

## ①研究参加者

| 氏名    | 所属                      | 役職 | 参加時期        |

|-------|-------------------------|----|-------------|

| 越智 裕之 | 立命館大学情報理工学部情報<br>システム学科 | 教授 | H25.4~H26.3 |

### ②研究項目

・再構成可能ディペンダブル VLSI へのマッピング技術

### (2)国内外の研究者や産業界等との連携によるネットワーク形成の状況について

衛星搭載用組み込みシステム設計技術に関する情報交換を NEC 東芝スペースシステム社と実施し、宇宙用 FPGA の課題の明確化と宇宙用汎用 ASSP に必要とされる要件定義を実施した。東京大学の先端科学技術研究センターで開発されている地球観測用衛星が搭載しようとしている高度な情報処理能力を調査し、本研究の成果を発展させることで実現可能であることを明らかにした。宇宙衛星用組込みシステムに関する意見交換ならびにソフトエラー対策技術に関する技術討論を、JAXA の総合技術研究本部および宇宙科学研究本部の研究者と実施した。再構成アーキテクチャを次世代宇宙機向けのヘテロジニアスなネットワーク実現に応用する方法について検討を進めた。また、JAXA の総合技術研究本部の協力のもと、耐放射線フリップフロップのソフトエラー耐性を評価するための重イオンを用いた加速テストを実施した。再構成可能アーキテクチャを中心としたディペンダブル VLSI プラットフォームに関する情報交換を、ルネサスエレクトロニクス社と NEC 社で動的再構成デバイスの商品化開発を担当するグループと行った。再構成可能アーキテクチャならびにソフトエラー対策技術に関する情報交換を、日立製作所生産技術研究所において高信頼

化技術を担当しているグループと実施した。

ソフトエラーに焦点を絞った技術討論会を2011年9月に京都工芸繊維大学で開催し、JAXA、日立製作所、富士通セミコンダクタ、ルネサスエレクトロニクスなどに所属する日本を代表するソフトエラー関係の研究者と情報交換するとともに、今後の連携可能性について協議した。2012年9月には第2回の技術討論会を福岡システム LSI 総合開発センターにて開催、2013年8月には第3回の技術討論会を広島市立大学にて開催した。今後も当該技術領域に特化した国内唯一の技術情報交換と連携の場として活動を継続する事を確認した。平成22年度までは「VLSIディペンダビリティの物理・デバイス・回路レベルテスト構造フォーラム」を開催し、特にTEG(Test Element Group)の設計や評価技術に関する情報交換を領域内の多くの研究チームの間で実施した。さらにSpaceWire ユーザ会に参加し、公開頂いたSpaceWire IPを用いたリアルタイム動画転送への適用を市販 FPGAボードを用いて評価し、再構成可能 VLSIプラットフォームへの統合を進めた。本研究で得られた知見をもとに、SpaceWireネットワークで生ずる Blocking の問題を解決すべく、JAXAの宇宙科学研究所と共同でNon-Bloking ルーターIPを開発した。

# §4 研究実施内容及び成果

1)成果1. 「ディペンダブル VLSI プラットフォーム」(全グループ)

## ①実施方法•実施内容

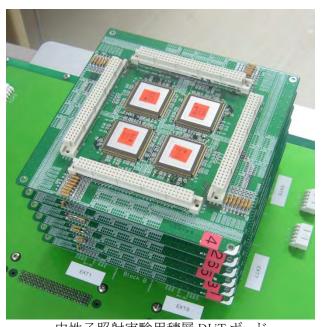

本プロジェクトの最終成果物として、再構成アーキテクチャグループによる信頼性可変再構成可能アーキテクチャ FRRARY、再構成プロセッサグループによる高信頼性プロセッサ DARA と高信頼性 FF の研究成果を統合したディペンダブル VLSI プラットフォームを構築した。本ディペンダブル VLSI プラットフォームを SoC として実装し、さらにその性能とディペンダビリティを評価するデモシステムを開発した(図4)。ビデオ入出力ボードを接続し、動画像アプリケーションによる評価を可能にした。

実証実験における信頼性可変再構成可能アーキテクチャへのアプリケーションマッピングは、C 設計ツールグループによる信頼性を考慮した動作合成技術と、マッピング技術グループによる信頼性を考慮した配置配線技術によって実現した。

宇宙向け高信頼通信規格 SpaceWire I/F も搭載しており、SpaceWire を介して再構成可能アーキテクチャの動的再構成が可能である。

## ②創造性

回路技術、アーキテクチャ技術、プロセッサ技術、設計自動化技術による階層横断的取り組みによって、 VLSI に要求される多様な機能やディペンダビリティを単一チップデザインにより適応的に満たす 「ディペンダブル VLSI プラットフォーム」は、世界に先駆けて Cross Layer Reliability を具現化 したものであり、その成果は極めて先進的である。

# ③有用性

評価用アプリケーションとしてリアルタイム画像処理を実現できる規模のディペンダブル VLSI プラットフォームの試作 SoC において、信頼性を考慮した動作合成や配置配線が可能な CAD 技術を利用することによって、面積コストとディペンダビリティのトレードオフ評価が可能である。アプリケーションに要求されるディペンダビリティを限られた面積コストで実現しながら、必要な処理性能を達成することができる。また、アプリケーション開発者が本プラットフォームの有用性を確認できる評価環境の整備が可能であることを示し、新たな出口展開の探索を加速させている。

### ④優位比較

本プラットフォームは、製造性劣化、物理的揺らぎ、一過性雑音、特性劣化などのディペンダビリティ阻害要因を対象として、回路技術、再構成可能アーキテクチャ技術、設計自動化技術、プロセッサ構成技術の総合的階層横断的取組みにより、要求されるレベルに応じたディペンダビリティを提供することができる世界初の組込みシステム用再構成可能 VLSI プラットフォームである。

(a) 全体構成

(b) 評価用デモボード

図 4: ディペンダブル VLSI プラットフォーム((a) 評価システム全体構成、(b) FPGA ボードの組み合わせによる試作 SoC 評価システム写真)

# 2) 成果 2.「信頼性可変再構成可能アーキテクチャ」(再構成アーキテクチャグループ)

### ①実施方法•実施内容

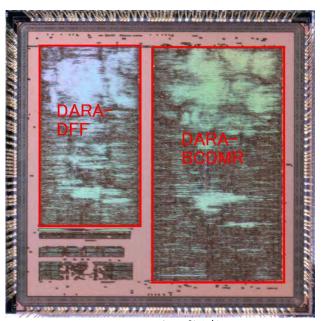

ソフトエラーによる回路誤動作や、経年劣化によるタイミング故障などの信頼性毀損要因に対して、アーキテクチャベルで柔軟にディペンダビリティを担保することが可能な粗粒度細粒度混合再構成可能アーキテクチャ FRRARYを開発した。FRRARYは、アレイ構造の基本要素であるクラスタ内で、構成情報メモリおよび演算回路の冗長化と機能交換を可能としており(図 5(a))、要求されるディペンダビリティに応じた適応的冗長化と、遅延故障やハードウェア故障発生時のスペア回路との動的機能交換(ホットスワップ)が可能である。FRRARYは、ALUベースの粗粒度型構成要素(図 5(b))のほかに、LUTベースの細粒度型構成要素(図 5(c))も有しており、条件分岐などの制御構造を含むプログラム全体のアクセラレータとして利用可能である。開発した信頼性可変再構成可能アーキテクチャの VLSI 化を行い、高信頼プロセッサとあわせて試作チップを作成した(図 5(d))。成果 1 で述べた評価用デモシステムを用いてその有効性を示した。

また、開発した再構成可能アーキテクチャを宇宙用途に対応させるため、宇宙機アプリケーションに適したファンクションと配線構造について検討し、混合粒度再構成可能アーキテクチャの改良を行った。回路動作の高速化および回路面積の削減を目指したアーキテクチャの改良に加えて、配線容易性とツール親和性を向上させるために配線構造を刷新した。さらに、実装可能状態数の向上と条件分岐処理マッピングの効率化によって、より複雑な制御処理を実現可能にした。SpaceWire インタフェースを搭載する粗粒度構成要素を設計し、SpaceWire による高速高信頼通信を可能にした。

### ②創造性

構成情報メモリと演算回路の冗長度を構成要素毎に自由に設定できる再構成可能アーキテクチャは、高信頼性を実現する技術として独創的なものである。また、データパス処理の加速を目的とする粗粒度構成要素を中心としながら、条件分岐などの制御構造やビット演算を実現する細粒度構成要素も有しており、混合粒度再構成可能アーキテクチャとしていることも特徴的である。粗粒度型の場合、アプリケーションの実現にはプロセッサとの協調動作が不可欠であるが、これに対して開発した混合粒度再構成可能アーキテクチャは、プロセッサとの通信オーバヘッドを大幅に削減でき、より実用的なアプリケーションを実現することができる。

#### ③有用性

再構成可能アーキテクチャでは、回路の冗長化によってディペンダビリティを実現するが、従来の構成可能アーキテクチャでは、LUT の内容や配線接続といった回路構成を定義する構成情報自体の冗長化は不可能である。一方、FRRARY は、構成要素毎に構成情報メモリと演算回路の適応的冗長化が可能である。これにより、FRRARY は、許容される面積コストで求められるソフトエラー耐性を効率良く実現できる。

粗粒度と細粒度の構成要素を併せ持つことで、データストリーミング処理だけでなく条件分岐などの制御処理を実現できるようになり、一般的な粗粒度型再構成可能アーキテクチャと比較して対象アプリケーション領域が大幅に拡大され、より実用的なアプリケーションが搭載することができる。さらに、C 設計ツール技術グループによる動作合成ツールとの連携により、状態遷移機械の導入によるリソース共有を効率的に実現でき、必要なリソース量の削減が可能である。また、マッピング技術グループによる信頼性を考慮したマッピングツールとの連携により、限られた面積で最大限のディペンダビリティを実現する。

#### ④優位比較

FRRARY における構成情報のサイズは、SRAM型 FPGAと比較して約1%であるため、FRRARY のソフトエラー発生率は相対的に2桁小さくなる。さらに、構成情報の書き換えに必要なサイクル数が少なく、再起動時のダウンタイムを大幅に削減できる。耐放射線 FPGAとして利用されているアンチフューズ型 FPGAでは、高いソフトエラー耐性と引き替えに動作速度や集積度が SRAM型 FPGAに対して大きく劣る。これに対し、FRRARY は先端 CMOS プロセスを用いて実装できるうえ、何度でも回路構成を書き換えることができる。

一方、粗粒度型再構成可能アーキテクチャの中での優位性について考えると、状態遷移機械による粗粒 度再構成可能演算器アレイの制御が可能であることに加えて、制御処理などを実現する細粒度構成要素を 持つことで状態遷移機械やビット演算も再構成可能アレイ上で実現できるデバイスは他に例がない。さらに、 信頼性を考慮したアプリケーションマッピングを行うための CAD 技術との連携により、構成要素毎に適切な 信頼性を設定し、アプリケーションや動作環境に応じて要求されるディペンダビリティを効率良く実現する。

図 5: 信頼性可変再構成可能アーキテクチャ FRRARY((a)構成要素の基本構成、(b)状態遷移機械による制御が可能な ALU クラスタ、(c)制御処理系やビット演算を実現する LUT クラスタ、(d)試作チップレイアウト)

3) 成果3. 高信頼性プロセッサ(再構成プロセッサグループ)

# ①実施方法•実施内容

多重化度を動的に変更し、一時故障の発見/回復と永久故障の発見には2重化構成を、永久故障の回復には3重化構成を用いることで平均多重化度を削減し、信頼性向上に要するコストを削減するプロセッサ・アーキテクチャ DARA(Dynamic Adaptive Redundancy Architecture)を提案した。適応的多重化実行の様子を図6左に示す。高信頼実行は2重化実行による故障検出と故障検出時の再実行を基本とし、一時故障からは実行結果不一致時に2重化実行のまま再実行することで回復する。永久故障は再実行を繰り返しても回復せず、

引き続き実行結果不一致の状態が続くため、3 重化実行に移行して故障箇所の検出と切り離しを行った後、また2 重化実行に戻る形を取る。2 重化から3 重化への変更は、パイプライン中の正常な状態のコピーによって実現する。

## ②創造性

マルチスレッド実行等を利用して多重化実行を可能とし、組み合わせるスレッド数で任意の多重化度を選択できる研究はいくつか存在する。しかしながら、ハードウェアとして自動的に動的な多重化度変更を行いソフトウェアサポートを必要としない点、および、動的な多重化度の変更を利用し、永久故障対応において、常に3重化を用いることなく2重化を基本として動作させる構成に、創造性がある。

### ③有用性

従来は3重化構成が一般的であった永久故障への対応についても、2重化を基本とするため、高信頼化のオーバヘッド、特に電力コストが削減できる。3重化実行を要する時間は2重化実行と比べて極めて短く、従来の固定3重化と比較して電力コストを約2/3に削減する。この電力削減による動作温度の低下は、NBTIなどの高温で進行が早い経年劣化の軽減にも効果がある。3重化動作時に使う予備パイプラインを別用途のプロセッサ・コアと共有することにより、回路面積コストも削減する。ステージ単位でエラー検出を行うため、エラーから高速に回復し、複数のエラーが蓄積してプロセッサ状態が回復不可能な状況に陥ることを防ぐ。なお、比較器等もパイプライン・モジュールに組み込み、種々のマルチコア/多重化構成における設計変更を不要とすることで設計/製造容易性について考慮してある。

DARA の有効性を示すため、180nm プロセスで試作した DARA 上で α 線を照射しつつ Stanford ベンチマークの各ベンチマーク・プログラムを 1,000 回実行した。図 6 右に、各ベンチマーク・プログラムの実行時間、および、実行中に発生したエラー数の平均/最大値/最小値を示す。グラフの横軸はベンチマーク・プログラムであり、棒グラフとそのエラー・バーは 1 実行あたりの再実行数を、折れ線グラフとそのエラー・バーは実行時間を示す。高いエラー・レートのもとでもエラーを検出して再実行を行い、プログラムの正常出力が得られることを確認した。

#### ④優位比較

多くのエラー耐性を持つプロセッサはチェックポイント回復と2 重化実行を組み合わせるものであり、永久故障には対応できないうえ、チェックポイント間のストア処理を保存するバッファが必要となる。マルチコア・プロセッサを利用した耐エラー・プロセッサの類似研究として、Configurable Isolation[1]や Core Cannibalization Architecture[2]がある。前者は多重化を行うコアの組が固定されており、また、多重化をエラー検出後に多重化を切り替える機構は準備されていない。後者は永久故障に特化した構成であり、また、故障発生時にプログラム実行を継続させたまま回復することを考慮していない。これらに対し、DARAは一時故障/永久故障双方への対応、多重化を行う組の自由度によるより長いライフサイクル、プログラム実行を継続したままエラー検出後の多重化度変更による電力/回路面積コスト削減、比較器等もパイプライン・モジュールに組み込み種々のマルチコア/多重化度に対する設計/製造容易性についても考慮してある点で優位である。

- [1] N. Aggarwal, et al., "Configurable Isolation: Building High Availability Systems with Commodity Multi-Core Processors," ISCA-2007, Jun. 2007.

- [2] B. F. Romanescu, et al., "Core Cannibalization Architecture: Improving Lifetime Chip Performance for Multicore Processors in the Presence of Hard Faults," PACT-2008, Oct. 2008.

図 6: DARA による適応的多重化実行(左)と試作チップにおける α 線照射評価結果(右)

4) 成果4.「C 言語設計環境」(C 設計ツールグループ・マッピング技術グループ)

### ①実施方法•実施内容

選択的三重化に対応した混合粒度再構成可能アーキテクチャをターゲットとする、C 言語からの設計開発環境の構築を進めた(図 7(a))。

動作合成は産業的にも実績のある CyberWorkBench をベースとし、ANSI-C 言語に準拠したデザインエントリと、面積や遅延時間制約への対応を可能とした。粗粒度再構成可能デバイスは、ALU ベースのアーキテクチャであるため、論理ゲートをベースとした ASIC や LUT をベースとした FPGA などとは演算のためのリソース配分がまったく異なる。通常の ASIC や FPGA 向けに最適化した RTL では、粗粒度アーキテクチャの特性を生かすことができず、リソースを効率よく利用することは困難である。本研究では、アーキテクチャの特性も考慮し、対象アーキテクチャ上で有利な演算を多く使用するように RTL を合成することで、人手により記述した RTLよりも使用するリソースを抑え、多重化によるディペンダビリティの確保にリソースを活用することを実現した。さらに、面積を増加せずに、時間方向へ3重化することで、冗長性を増し、ソフトエラー耐性をあげる方法を研究し、プロトタイプを実現した。また、FRRARY の16ビットアーキテクチャで任意のビット幅のプログラムを実行するための高位合成手法を研究し、システム上に実装した。

選択的三重化への対応については、与えられた回路面積等の制約のもとでソフトエラー耐性を最大化すべく、三重化を適用する箇所を自動的に選択する手法を開発した。ソフトエラー耐性の正確な評価には、アプリケーションの配置配線や故障挿入シミュレーションによる信頼性評価が必要になるが、これらには多くの時間を要する。そこで本研究では、アプリケーションの DFG から重要な特徴を抽出することで、最適な三重化の適用箇所の探索をヒューリスティックにより加速した。また、これまでに構築してきた自動配置配線ツールを含む信頼性評価環境を用いて、提案手法の有用性を示した。図 7(b)に示すように、開発したヒューリスティックによってほぼ理想的な設計空間探索が可能になっている。

対象アーキテクチャは、粗粒度演算要素のみからなる再構成可能アーキテクチャにとどまらず、ステートマシン等を実装するための細粒度の演算機構も有する粒度混合型アーキテクチャにも対応可能である。

## ②創造性

粗粒度再構成アーキテクチャを対象とした C 言語からの動作合成の研究は先導的であり、特に信頼性を 考慮した設計開発環境はユニークである。また一部の演算器を三重化することで効果的に信頼性を高めるこ とができることを示し、三重化すべき演算器を特徴づける性質を明らかにしている。特に、時間方向多重化は、 従来の設計手法(RTL 設計)では設計が難しく、事実上困難である。動作合成と結びつけたことで初めて実 用レベルで実現可能となった。

#### ③有用性

選択的三重化は与えられた信頼性制約下で最もリソース使用量の少ない回路実装を行う上で極めて有用であり、これを適用するためには三重化すべき箇所を最適に選択することが必要である。これを自動化し、動作合成ツールで利用可能とすることで、ディペンダブルな再構成可能アーキテクチャの実用化を加速する。時

間方向3重化は、空間3重化のように面積を3倍にすることなく、特定の面積制約のもとで、時間方向に3重化することを可能にした。再構成デバイスは一定の面積のチップを量産するため、この機能は従来使われなかった残りの面積を信頼性(ソフトエラー耐性の向上)に利用可能とするものである。

また、FRRARY は 16 ビット ALU のアレイであるが、任意ビット長(54 ビット、17 ビット等)の演算を可能にできるようにしたため、画像処理、本姓処理、暗号等さまざまなビット長を要求するアプリケーションに対応可能となった。(プロセッサの多倍長処理は複数サイクルかけてソフトウェア的なエミュレーションであるが、FRRARYでは任意ビット幅の演算を 1 クロックで実現可能であり、プロセッサの方式に比べ処理サイクル数が少なくてよい。)

### ④優位比較

動作仕様レベルで多重化する部分を指定し、選択的部分多重化をサポートするハードウェアに対応した RTL 上に実現する技術はこれまでに存在していない。粗粒度再構成可能アーキテクチャとこれに向けた配 置配線ツールには先行研究事例があるが、多重化を導入する等、ディペンダビリティを考慮したツールは見 られない。

FPGA を対象とした Sensitive bit の評価および部分的三重化の導入は Los Alamos 研究所などで研究が行われているが、粗粒度再構成可能アーキテクチャを対象とした研究はなく、世界に先駆けた研究である。

図 7: 信頼性を考慮した C 言語設計環境

5) 成果5.「放射線耐性強化回路技術」(再構成プロセッサグループ)

#### ①実施方法•実施内容

低電力な高信頼 FF の設計とその評価を行うとともに、重イオンビームによる高信頼 FF のソフトエラー耐性の評価を行い、信頼性の必要な地上や、宇宙への応用において利用できることを実証する。さらに、商用 FPGA、試作 LSI での経年劣化の評価も行い、経年劣化が LSI や FPGA に及ぼす影響についてまとめる。具体的には、BCDMR (Bistable Cross-coupled Dual-Modular Redundancy) FF の提案を行い、高いクロック周波数でも強靭なエラー耐性を持つことを、シミュレーションならびに実測で実証した。さらに、電力効率の低減を狙って、BCDMR ACFF (Adaptive Coupled FF)の提案を新たに行い、その電力効率の良さも実証した。発表前のため、ここでは触れていないが、DICE 構造を低電力化した DICE ACFF も評価中であり、BCDMR ACFF よりも省面積で、エラー耐性の高いことを実証予定である。評価は研究室で所有するα線源、阪大の加速器、JAEA 高崎の加速器にて行った。阪大では、地上での中性子線を加速した白色中性子線にて、LSIを多数積層した DUT ボードにより行った。JAEA 高崎の加速器では、重イオンをそのエネルギー毎に照射する実験を行った。平成23年度平成24年度に、実験を行い、エラー耐性の実証を行った。

#### ②創造性

本研究で提案した BCDMR FF, BCDMR ACFF は既存の回路(BISER FF 並びに ACFF)より, 新たに創造したものである. 高いクロック周波数での耐放射線 FF の脆弱性は, これまでほとんど指摘されていない新たな脆弱性である. 我々はの脆弱性を修正するための BCDMR FF を新たに考案した. また, 耐放射線 FF

の低電力化は未開拓の領域であり、新分野を先導する成果である.

# ③有用性

冗長化 FF は高信頼であるが、面積、電力ともに非冗長のものより大きくなる。冗長化のための面積オーバヘッドを減らすのは困難であるため、電力オーバヘッドを減らすことを目的として、BCDMR ACFF (図 5 左)の設計を行った。ACFF は東芝により 2011 年の ISSCC で発表された低電力型 FF である。クロックバッファを廃することで、特に活性化率(FF の入力のトグル率)が低いところで、電力が低くなる。Intel のサーバで利用されている DICE FF などとの消費電力を FF の入力の活性化率  $\alpha$  で比較した結果を図 8 右に示す。このグラフの通り BCDMR ACFF は  $\alpha$  が 10%を切ると冗長化していない TGFF よりも電力が小さくなる。一般に ASIC内の FF の活性化率は 5-10%と言われており、冗長化システムにおいても、非冗長化システムと同程度の消費電力が期待できる。

# ④優位比較

優位性は図 8 右を見れば明らかである。このグラフは横軸が活性化率、縦軸が従来の TGFF (Transmission Gate FF)の電力を 1 とした相対電力を表す。活性化率が高いところでは電力は従来型の BCDMR や商用のサーバに用いられている DICE に比べて電力は高くなる。しかし、活性化率が低くなると、 圧倒的に電力が低くなる。通常の ASIC 内での FF の活性化率は 5-10%程度といわれており、通常の DFF を BCDMR ACFF に置き換えても電力オーバヘッド 0 となることが期待される。

図 8: BCDMR ACFF(左)と活性化率(Data Activity)による電力比較(TGFF(通常の DFF)を 1)(右)

6)成果6.「ばらつき耐性強化設計技術」(ロバストファブリックグループ)

#### ①実施方法•実施内容

電源電圧の低下に伴い、デバイス特性のばらつきが回路特性のばらつきに及ぼす影響が顕著になっている。これらのばらつきには、製造ロットやウェファー/チップごとに変動する成分とともに、チップ内の場所に依存して変動する成分も含まれる。80 コアを集積化したプロセッサの例では、コア間での最大動作周波数のばらつきが電源電圧 1.2V において 28% あり、電源電圧 0.8V では 62% に拡大する事が報告されている[Dighe, et.al., JSSC2010, p.184]。本研究では、チップ内を多数の小領域に分割し、各小領域毎(細粒度)に自律的に特性ばらつきを診断して基板バイアス制御により動作特性ばらつきを補償する、ばらつき耐性強化設計技術(細粒度特性ばらつき補償回路)を開発した。

開発回路の基幹を成すのは、ディジタル型 PMOS/NMOS 特性モニタ回路とセルベース設計による小面積基板バイアス生成回路である。特性モニタ回路は、PMOS トランジスタと NMOS トランジスタの特性変動のそれぞれを独立に診断する。診断結果に基づき、基板バイアス生成回路が NウェルとPウェルの基板電位を独立に調節する。これらの特性補償は小領域毎に独立に行われるため、チップ間ばらつきとともにチップ内ばらつきについても動作特性補償を行う事が可能となった。65nmプロセスでの実証実験では、0.1mm²を対象とした細粒度特性ばらつき補償回路の専有面積は 2628μm²であり、その面積オーバヘッドは 2.6% と小さい。図 9 左に、他のロジックと混載した細粒度特性ばらつき補償回路を示す。条件振りチップ(SS, SF, FS, FF)による動作確認の結果、SS, SF, FS チップの動作速度を TT チップの目標速度まで回復する事が出来た(図 9 右参照)。本開発回路に使用した特性モニタ回路は、トランジスタのチップ間ばらつきを診断する回路である。

これ以外にも、チップ内ばらつきを診断可能な非均質構造モニタや動的に構成を変えることにより、チップ間ばらつきとチップ内ばらつきの双方を診断可能なモニタ回路を開発した。

#### ②創造性

セルベース設計可能な完全ディジタル型でありながら、NMOSトランジスタとPMOSトランジスタの特性変動を独立に評価可能な遅延セルの構造を明らかにした。また、遅延回路の構造を非均質にすることで、特定のトランジスタのばらつきが診断できることを明らかにした。更に、回路構造を動的に変更する事で、チップ間ばらつきとチップ内ばらつきの双方を診断できる回路方式を開発した。いずれもオリジナルな回路であり、創造性が高い。

基板バイアス生成回路はアナログ回路であり、通常はフルカスタム設計が行われてきた。本研究では、適切な回路分割を行う事で、セルベース設計の枠組みの中で自動設計を行う事が可能であることを明らかにした。これは、アナログ回路設計方法論の革新に向けた重要な一歩である。

#### ③有用性

今回の研究成果は、設計回路のばらつき耐性向上に直結する技術である。設計対象のアプリケーションを問わずに、全ての回路に対して有効であり、極めて有用性が高い。また、特性モニタは完全ディジタル型であり、アナログ部分を含んだ基板バイアス回路もセルベース設計環境で実装できる回路方式を開発した。そのため、通常のセルベース設計環境において設計可能であり汎用性も高い。特性変動をモニタする従来方式として、クリティカルパスの遅延時間を用いる方法があるが、PMOSとNMOSの変動量を独立に求める事が出来ず、リーク電流増加による不必要な消費電力増大が発生する。

#### ④優位比較

チップ内ばらつきへの対策として、先の 80 コアプロセッサにおいて、コア毎に電源電圧と動作周波数を調節する方式が提案されている。この方式では、コア毎に DCDC 変換回路や PLLを用意する必要があり、その実装コストや設計コストが膨大になると予想される。それに対して、今回の開発技術では、コア用の電源とクロック信号のみで動作する。さらに、通常のセルベース設計環境で実装可能である。そのため、実装コストと設計コストのいずれの面でも圧倒的に優位である。

図 9: 他のロジックと混載した細粒度特性ばらつき補償回路(左)と、コーナーチップ(SS, SF, FS, TT)の動作速度を補償した結果(右)。

## § 5 成果発表等

- (1)原著論文発表 (国内(和文)誌5件、国際(欧文)誌144件)

- 1. Hirokazu Muta, Hidetoshi Onodera (Kyoto Univ.), "Manufacturability-Aware Design of Standard Cells, "IEICE Trans. on Electronics, vol E90-A, no12, pp. 2682-2960, Dec. 12, 2007,

- DOI:10.1093/ietfec/e90-a.12.2682.

- 2. Takayuki Fukuoka, Akira Tsuchiya, Hidetoshi Onodera (Kyoto Univ.), "Statistical Gate Delay Model for Multiple Input Switching," The 13th Asia and South Pacific Design Automation Conference, pp. 286 291 Jan. 23, 2008, DOI: 10.1109/ASPDAC.2008.4483959.

- 3. Yuuri Sugihara, Yohei Kume, Kazutoshi Kobayashi, Hidetoshi Onodera (Kyoto Univ.), "Speed and Yield Enhancement by Track Swapping on Critical Paths Utilizing Random Variations for FPGAs," FPGA Conference, pp. 257–257, Feb. 25, 2008, DOI: 10.1145/1344671.1344711.

- 4. S. Abe, M. Hashimoto, and T. Onoye (Osaka Univ.), "Clock Skew Evaluation Considering Manufacturing Variability in Mesh-Style Clock Distribution," Proceedings of International Symposium on Quality Electronic Design (ISQED), pp.520- 525, Mar. 18, 2008, DOI: 10.1109/ISQED.2008.4479789.

- 5. K. Hamamoto, H. Fuketa, M. Hashimoto, Y. Mitsuyama, and T. Onoye (Osaka Univ.), "Experimental Study on Body-Biasing Layout Style -- Negligible Area Overhead Enables Sufficient Speed Controllability -," Proc. of ACM Great Lake Symposium on VLSI (GLSVLSI), pp.387-390, May 6, 2008, DOI: 10.1145/1366110.1366202.

- 6. Haruhiko Terada, Takayuki Fukuoka, Akira Tsuchiya, Hidetoshi Onodera (Kyoto Univ.), "Accurate Estimation of the Worst-case Delay in Statistical Static Timing Analysis," IPSJ Transactions on System LSI Design Methodology, vol 1, pp. 116-125, Aug. 29, 2008, DOI: 10.2197/ipsjtsldm.1.116.

- 7. H. Fuketa, M. Hashimoto, Y. Mitsuyama, and T. Onoye (Osaka Univ.), "Correlation Verification between Transistor Variability Model with Body Biasing and Ring Oscillation Frequency in 90nm Subthreshold Circuits," Proc. of IEEE/ACM International Symposium on Low Power Electronics and Design(ISLPED), pp.3–8, Aug. 2008, DOI: 10.1145/1393921.1393929.

- 8. Kazutoshi Kobayashi, Yohei Kume, Cam Lai Ngo, Yuuri Sugihara, Hidetoshi Onodera(Kyoto Univ.), "A Variation-aware Constant-Order Optimization Scheme Utilizing Delay Detectors to Search for Fastest Paths on FPGAs," Proc. of 2008 International Conference on Field Programmable Logic and Applications, pp.107-112, Sept. 8, 2008, DOI: 10.1109/FPL.2008.4629916.

- Yuuri Sugihara, Yohei Kume, Kazutoshi Kobayashi, Hidetoshi Onodera(Kyoto Univ.), "Performance Optimization by Track Swapping on Critical Paths Utilizing Random Variations for FPGAs," Proc. of 2008 International Conference on Field Programmable Logic and Applications, pp.503-506, Sept. 8, 2008, DOI: 10.1109/FPL.2008.4629994.

- 10.S. Abe, M. Hashimoto, and T. Onoye(Osaka Univ.), "Clock Skew Evaluation Considering Manufacturing Variability in Mesh-Style Clock Distribution," IEICE Trans. on Fundamentals of Electronics, Communications and Computer Sciences, Vol.E91-A, No.12, pp.3481-3487, Dec. 2008, DOI: 10.1093/ietfec/e91-a.12.3481.

- 11.Kentaro Nakahara, Shin'ichi Kouyama, Tomonori Izumi, Hiroyuki Ochi(Kyoto Univ.), and Yukihiro Nakamura, "Autonomous Repair Fault Tolerant Dynamic Reconfigurable Device," IEICE Trans. on Fundamentals, Vol.E91-A, No.12, pp.3612-3621, Dec. 2008, DOI: 10.1093/ietfec/e91-a.12.3612.

- 12.Hidetoshi Onodera(Kyoto Univ.), "Variability Modeling and Impact on Design," 2008 International Electron Devices Meeting Technical Digest, pp. 701–704, Dec. 24, 2008, DOI: 10.1109/IEDM.2008.4796791.

- 13.H. Fuketa, M. Hashimoto, Y. Mitsuyama, and T. Onoye(Osaka Univ.), "Trade-Off Analysis between Timing Error Rate and Power Dissipation for Adaptive Speed Control with Timing Error Prediction," Proc. of Asia and South Pacific Design Automation Conference (ASP-DAC), pp.266-271, Jan. 2009, DOI: 10.1109/ASPDAC.2009.4796491.

- 14.K. Hamamoto, H. Fuketa, M. Hashimoto, Y. Mitsuyama, and T. Onoye(Osaka Univ.), "An Experimental Study on Body-Biasing Layout Style Focusing on Area Efficiency and Speed Controllability," IEICE Trans. on Electronics, pp.281-285, Vol.E92-C, No.2, Feb. 2009, DOI: 10.1587/transele.E92.C.281.

- 15.Hiroki Sunagawa, Haruhiko Terada, Akira Tsuchiya, Kazutoshi Kobayashi, Hidetoshi Onodera(Kyoto

- Univ.), "Effect of Regularity-Enhanced Layout on Printability and Circuit Performance of Standard Cells," Proc. of the 10th International Symposium on Quality Electronic Design, pp.195-200, Mar. 16, 2009, DOI: 10.1109/ISQED.2009.4810293.

- 16.古田潤、小林和淑、 小野寺秀俊(京都大学)、「高い SEU/SET 耐性を持つ省面積・低遅延二重化フリップフロップ」、第22回回路とシステム軽井沢ワークショップ、pp.456-461、2009年4月.

- 17.天木健彦、橋本昌宜、密山幸男、尾上孝雄(大阪大学)、「マルコフモデルによるオシレータサンプリング方式真性乱数生成器の乱数品質解析」、第 22 回 回路とシステム(軽井沢)ワークショップ、pp.474-479、2009 年 4 月.

- 18.Hiroyuki Kanbara, Ryota Kinjo, Yuki Toda, Hiroyuki Okuhata, and Masanao Ise(ASTEM RI), "Dependable Embedded Processor Core for Higher Reliability," Proc. of 13th IEEE International Symposium on Consumer Electronics(ISCE 2009), pp.819-822, May 2009, DOI: 10.1109/ISCE.2009.5157061.

- 19.J. Yao(NAIST), K. Ogata(Mitsubishi Elec.), H. Shimada(NAIST), S. Miwa(TUAT), H. Nakashima, and S. Tomita(Kyoto Univ.), "An Instruction Scheduler for Dynamic ALU Cascading Adoption," 情報処理学会論文誌、コンピューティングシステム、Vol. 2、No. 2、pp.30-47、2009年7月、DOI: 10.2197/ipsjtrans.2.122.

- 20.Zoltan Endre Rakosi, Masayuki Hiromoto, Hiroyuki Ochi(Kyoto Univ.), and Yukihiro Nakamura(Ritsumeikan Univ.), "Hot-Swapping Architecture Extension for Mitigation of Permanent Functional Unit Faults," in Proc. of the 19th International Conference on Field Programmable Logic and Applications (FPL2009), pp.578-581, August 2009, DOI: 10.1109/FPL.2009.5272428.

- 21.K. Hamamoto, M. Hashimoto, Y. Mitsuyama, and T. Onoye(Osaka Univ.), "Tuning-Friendly Body Bias Clustering for Compensating Random Variability in Subthreshold Circuits," Proc. of IEEE/ACM International Symposium on Low Power Electronics and Design (ISLPED), pp.51-56, August 2009, DOI: 10.1145/1594233.1594246.

- 22.D. Alnajjar, Y. Ko(Osaka Univ.), T. Imagawa(Kyoto Univ.), H. Konoura(Osaka Univ.), M. Hiromoto(Kyoto Univ.), Y. Mitsuyama, M. Hashimoto(Osaka Univ.), H. Ochi(Kyoto Univ.), and T. Onoye(Osaka Univ.), "Coarse-Grained Dynamically Reconfigurable Architecture with Flexible Reliability," Proc. of International Conference on Field Programmable Logic and Applications (FPL), pp.186-192, August 2009, DOI:10.1109/FPL.2009.5272317.

- 23.H. Fuketa, M. Hashimoto, Y. Mitsuyama, and T. Onoye(Osaka Univ.), "Adaptive Performance Compensation with In-Situ Timing Error Prediction for Subthreshold Circuits," Proc. of IEEE Custom Integrated Circuits Conference (CICC), pp.215-218, September 2009, DOI:10.1109/CICC.2009.5280882.

- 24. Hidetoshi Onodera, Haruhiko Terada (Kyoto Univ.), "Characterization of WID Delay Variability Using RO-array Test Structures," Proc. of 8th IEEE International Conference on ASIC, pp. 658-661, October 2009, DOI: 10.1109/ASICON.2009.5351332.

- 25. Hiroyuki Kanbara, Hiroyuki Okuhata, Masano Ise, Ryota Kinjo, and Yuki Toda(ASTEM RI), "Probability of Calculation Failures by Soft Errors in an Embedded Processor Core," Proc. of the IEEE 8th International Conference on ASIC(IEEE ASICON 2009), October 2009, DOI: 10.1109/ASICON.2009.5351357.

- 26.T. Takahashi, T. Uezono(Kyoto Univ.), M. Shintani, K. Masu(Tokyo Inst. Tech.), and T. Sato(Kyoto Univ.), "On-Die Parameter Extraction from Path-Delay Measurements," IEEE Asian Solid-State Circuit Conference (ASSCC), pp.101-104, November 2009, DOI: 10.1109/ASSCC.2009.5357189.

- 27.T. Fukuoka, A. Tsuchiya, H. Onodera(Kyoto Univ.), "Statistical Gate Delay Model for Multiple Input Switching," IEICE Trans. Fundamentals, Vol.E92-A, No.12, pp.3070-3078, December 2009, DOI: 10.1587/transfun.E92.A.3070.

- 28.H. Fuketa, M. Hashimoto, Y. Mitsuyama, and T. Onoye(Osaka Univ.), "Trade-Off Analysis between Timing Error Rate and Power Dissipation for Adaptive Speed Control with Timing Error Prediction," IEICE Trans. on Fundamentals, vol.E92-A, no.12, pp.3094-3102, December 2009, DOI:

- 10.1587/transfun.E92.A.3094.

- 29.D. Alnajjar, Y. Ko(Osaka Univ.), T. Imagawa, M. Hiromoto(Kyoto Univ.), Y. Mitsuyama, M. Hashimoto(Osaka Univ.), H. Ochi(Kyoto Univ.), and T. Onoye(Osaka Univ.), "Soft Error Resilient VLSI Architecture for Signal Processing," Proc. of IEEE International Symposium on Intelligent Signal Processing and Communication Systems (ISPACS), pp.183–186, December 2009, DOI:10.1109/ISPACS.2009.5383872.

- 30.H. Fuketa, M. Hashimoto, Y. Mitsuyama, and T. Onoye(Osaka Univ.), "Adaptive Performance Control with Embedded Timing Error Predictive Sensors for Subthreshold Circuits," Proc. of Asia and South Pacific Design Automation Conference (ASP-DAC), pp.361-362, January 2010, DOI: 10.1109/ASPDAC.2010.5419861.

- 31.H. Sunagawa, H. Terada, A. Tsuchiya(Kyoto Univ.), K. Kobayashi(KIT), H. Onodera(Kyoto Univ.), "Effect of Regularity-Enhanced Layout on Variability and Circuit Performance of Standard Cells," IPSJ Trans. System LSI Design Methodology, Vol. 3, pp.130-139, February 2010, DOI:10.2197/jpsjtsldm.3.130.IPSJ.

- 32.H. Konoura, Y. Mitsuyama, M. Hashimoto, and T. Onoye(Osaka Univ.), "Comparative Study on Delay Degrading Estimation Due to NBTI with Circuit/Instance/Transistor-Level Stress Probability Consideration," Proc. of International Symposium on Quality Electronic Design (ISQED), pp.646-651, March 2010, DOI: 10.1109/ISQED.2010.5450508.

- 33.R. Harada, Y. Mitsuyama, M. Hashimoto, and T. Onoye(Osaka Univ.), "Measurement Circuits for Acquiring SET Pulse Width Distribution with Sub-FO1-Inverter-Delay Resolution," Proc. of International Symposium on Quality Electronic Design (ISQED), pp.839-844, March 2010, DOI: 10.1109/ISQED.2010.5450480.

- 34.J. Furuta(Kyoto Univ.), K. Kobayashi(KIT) and H. Onodera(Kyoto Univ.), "An Area/Delay Efficient Dual-modular Flip-Flop with Higher SEU/SET Immunity," IEICE Trans. Electron. Vol. E93-C, No.3, pp.340-346, March 2010, DOI: 10.1587/transele.E93.C.340.

- 35.H. Fuketa, M. Hashimoto, Y. Mitsuyama, and T. Onoye(Osaka Univ.), "Alpha-Particle-Induced Soft Errors and Multiple Cell Upsets in 65-nm 10T Subthreshold SRAM," Proc. of International Reliability Physics Symposium (IRPS), pp.213-217, May 2010, DOI: 10.1109/IRPS.2010.5488826.

- 36.S.Abe, K.Shinkai, M.Hashimoto, and T.Onoye(Osaka Univ.), "Clock Skew Reduction by Self-Compensating Manufacturing Variability with On-chip Sensors," ACM Great Lake Symposium on VLSI (GLSVLSI), pp.197-202, May 2010, DOI: 10.1145/1785481.1785530.

- 37.密山幸男、高橋一真、今井林太郎、橋本昌宜、尾上孝雄、白川功(大阪大学)、「メディア処理向け再構成可能アーキテクチャでの動画像復号処理の実現」、電子情報通信学会論文誌 A、vol. J93-A、no. 6、pp. 397-413、2010 年 6 月、DOI: 10.1145/1785481.1785530. 3.

- 38. Jun Furuta(Kyoto Univ.), Chikara Hamanaka, Kazutoshi Kobayashi(KIT), Hidetoshi Onodera(Kyoto Univ.), "A 65nm Bistable Cross-coupled Dual Modular Redundancy Flip-Flop Capable of Protecting Soft Errors on the C-element," 2010 Symposium on VLSI Circuits Digest of Technical Papers, pp.123-124, June 17, 2010, DOI:10.1109/VLSIC.2010.5560329.

- 39. Takashi Imagawa, Masayuki Hiromoto, Hiroyuki Ochi, and Takashi Sato(Kyoto Univ.), "A Tool Chain for Generating SEU-Vulnerability Map for Coarse-Grained Reconfigurable Architecture," in Proc. of 26th Annual Intl. Technical Conference on Circuits/Systems, Computers and Communications (ITC-CSCC 2010), July 2010.

- 40.H. Fuketa, M. Hashimoto, Y. Mitsuyama, and T. Onoye(Osaka Univ.), "Transistor Variability Modeling and Its Validation with Ring-Oscillation Frequencies for Body-Biased Subthreshold Circuits," IEEE Trans. on VLSI Systems, vol.18, no.7, pp.1118-1129, July 2010, DOI: 10.1109/TVLSI.2009.2020594.

- 41.T. Amaki, M. Hashimoto, Y. Mitsuyama, and T. Onoye(Osaka Univ.), "A Design Procedure for Oscillator-Based Hardware Random Number Generator with Stochastic Behavior Modeling," Proceedings of International Workshop on Information Security Applications (WISA), August 2010,

- DOI: 10.1007/978-3-642-17955-6\_8.

- 42.Takashi Matsumoto, Hiroaki Makino (Kyoto Univ.), Kazutoshi Kobayashi (KIT), and Hidetoshi Onodera (Kyoto Univ.), "A 65nm CMOS 400ns Measurement Delay NBTI-Recovery Sensor by Minimum Assist Circuit," Proceedings of International Conference on Solid State Devices and Materials (SSDM 2010), pp.806-807, Sept. 2010.

- 43.Hiroki Sunagawa, Hidetoshi Onodera(Kyoto Univ.), "Variation-Tolerant Design of D FlipFlops," Proc. of IEEE International SOC Conference 2010, pp. 147-151, Sept. 27, 2010, DOI: 10.1109/SOCC.2010.5784732.

- 44. Takashi Imagawa, Masayuki Hiromoto, Hiroyuki Ochi, and Takashi Sato(Kyoto Univ.), "A Routing Architecture Exploration for Coarse-Grained Reconfigurable Architecture with Automated SEU-tolerance Evaluation," in Proc. of 23rd IEEE Intl. SOC Conference (SOCC 2010), pp.248-253, Sept. 2010, DOI: 10.1109/SOCC.2010.5784754.

- 45.Bishnu Prasad Das, Hidetoshi Onodera(Kyoto Univ.), "Warning Prediction Sequential for Transient Error Prevention," 2010 IEEE International Symposium on Defect and Fault Tolerance in VLSI Systems, pp.382 390, Oct. 8, 2010, DOI: 10.1109/DFT.2010.52

- 46. M. Yabuuchi, and K. Kobayashi(Kyoto Inst. Of Tech.), "Evaluation of FPGA design guardband caused by inhomogeneous NBTI degradation considering process variations," International Conference on Field Programmable Technologies, pp. 417-420, Dec. 2010, DOI: 10.1109/FPT.2010.5681449.

- 47.J. Yao, R. Watanabe, T. Nakada, H. Shimada, Y. Nakashima(Nara Institute of Science and Technology), and K. Kobayashi(Kyoto Inst. of Tech.), "Minimal Roll-Back Based Recovery Scheme for Fault Toleration in Pipeline Processors," Pacific Rim International Symposium on Dependable Computing, pp. 237-238, Dec. 2010, DOI: 10.1109/PRDC.2010.44.

- 48.Takashi Imagawa, Masayuki Hiromoto, Hiroyuki Ochi, and Takashi Sato(Kyoto Univ.), "Reliability Evaluation Environment for Exploring Design Space of Coarse-Grained Reconfigurable Architectures," IEICE Trans. Fundamentals, Vol.E93-A, No.12, pp.2524-2532, Dec. 2010, DOI: 10.1587/transfun.E93.A.2524.

- 49.R. Harada, Y. Mitsuyama, M. Hashimoto, and T. Onoye(Osaka Univ.), "Measurement Circuits for Acquiring SET Pulse Width Distribution with Sub-Fo1-Inverter-Delay Resolution," IEICE Trans. on Fundamentals of Electronics, Communications and Computer Sciences, vol.E93-A, no.12, December 2010, DOI: 10.1587/transfun.E93.A.2417.

- 50. J. Furuta(Kyoto Univ.), C. Hamanaka, K. Kobayashi(Kyoto Inst. of Tech.), and H. Onodera(Kyoto Univ.), "A 65nm Flip-Flop Array to Measure Soft Error Resiliency against High-Energy Neutron and Alpha Particles," Proc. of Asia and South Pacific Design Automation Conference, pp.83–84, Jan. 2011, DOI:10.1109/ASPDAC.2011.5722306.

- 51.M. Hashimoto (Osaka Univ.), "Run-Time Adaptive Performance Compensation Using On-Chip Sensors (Invited)," Proc. of Asia and South Pacific Design Automation Conference (ASP-DAC), pp. 285-290, January 2011, DOI:10.1109/ASPDAC.2011.5722199.

- 52.T. Amaki, M. Hashimoto, and T. Onoye(Osaka Univ.), "Jitter Amplifier for Oscillator-Based True Random Number Generator," Proc. of Asia and South Pacific Design Automation Conference (ASP-DAC), pp.81-82, January 2011, DOI: 10.1109/ASPDAC.2011.5722301.

- 53. Hiroshi Yuasa, Hiroshi Tsutsui, Hiroyuki Ochi, Takashi Sato, "A fully pipelined implementation of Monte Carlo based SSTA on FPGAs," Proc. of 2011 International Symposium on Quality Electronic Design (ISQED), pp. 785 790, March 2011, DOI:10.1109/ISQED.2011.5770818.

- 54.K. Ito, T.Matsumoto, S. Nishizawa, H. Sunagawa(Kyoto University), K. Kobayashi(Kyoto Institute of Technology), and H. Onodera(Kyoto University), "Modeling of Random Telegraph Noise under Circuit Operation Simulation and Measurement of RTN-induced delay fluctuation," International Symposium on Quality Electronic Design, pp.22–27, Mar. 2011, DOI: 10.1109/ISQED.2011.5770698.

- 55. Islam A.K.M Mahfuzul, Akira Tsuchiya(Kyoto Univ.), Kazutoshi Kobayashi(Kyoto Institute of Tech.),

- Hidetoshi Onodera(Kyoto Univ.), "Variation-sensitive Monitor Circuits for Estimation of Die-to-Die Process Variation," Proc. of 2011 IEEE International Conference on Microelectronic Test Structure(ICMTS), pp. 153–157, April 2011. DOI: 10.1109/ICMTS.2011.5976878.

- 56.Takashi Matsumoto, Hiroaki Makino(Kyoto Univ.), Kazutoshi Kobayashi(Kyoto Institute of Tech.), Hidetoshi Onodera(Kyoto Univ.), "A 65 nm Complementary Metal-Oxide-Semiconductor 400 ns Measurement Delay Negative-Bias-Temperature-Instability Recovery Sensor with Minimum Assist Circuit," Japanese Journal of Applied Physics, vol. 50, 04DE06, April 2011, DOI: 10.1143/JJAP.50.04DE06b.

- 57. Jun Furuta(Kyoto Univ.), Chikara Hamanaka, Kazutoshi Kobayashi(Kyoto Institute of Tech.), Hidetoshi Onodera(Kyoto Univ.), "Measurement of Neutron-induced SET Pulse Width Using Propagation-induced Pulse Shrinking," Proc. of 2011 IEEE International Reliability Physics Symposium, pp. 5B2.1-5B2.5, April 2011, DOI: 10.1109/IRPS.2011.5784520.

- 58.Kyosuke Ito, Takahi Matsumoto, Shinichi Nishizawa, Hiroki Sunagawa(Kyoto Univ.), Kazutoshi Kobayashi(Kyoto Institute of Tech.), Hidetoshi Onodera(Kyoto Univ.), "The Impact of RTN on Performance Flucuation in CMOS Logic Circuits," Proc. of 2011 IEEE International Reliability Physics Symposium, pp. CR.5.1-CR.5.4, April 2011, DOI: 10.1109/IRPS.2011.5784563.

- 59.R. Harada (Osaka Univ.), Y. Mitsuyama (Kochi Univ. of Tech.), M. Hashimoto, and T. Onoye (Osaka Univ.), "Neutron Induced Single Event Multiple Transients with Voltage Scaling and Body Biasing," Proc. of International Reliability Physics Symposium (IRPS), pp. 253-257, April 2011, DOI: 10.1109/IRPS.2011.5784485.

- 60.H. Fuketa (Univ. of Tokyo), D. Kuroda, M. Hashimoto, and T. Onoye (Osaka Univ.), "An Average-Performance-Oriented Subthreshold Processor Self-Timed by Memory Read Completion," IEEE Transactions on Circuits and Systems II, vol. 58, no. 5, pp. 299-303, May 2011, DOI: 10.1109/TCSII.2011.2149110.

- 61.T. Amaki, M. Hashimoto, and T. Onoye (Osaka Univ.), "An Oscillator-Based True Random Number Generator with Jitter Amplifier," Proc. of IEEE International Symposium on Circuits and Systems (ISCAS), pp. 725-728, May 2011, DOI: 10.1109/ISCAS.2011.5937668.

- 62.M. Hashimoto (Osaka Univ.) and H. Fuketa (Univ. of Tokyo), "Adaptive Performance Compensation with On-Chip Variation Monitoring (Invited)," Proc. of International Midwest Symposium on Circuits and Systems (MWSCAS), August 2011, DOI: 10.1109/MWSCAS.2011.6026381.

- 63.H. Fuketa (Univ. of Tokyo), M. Hashimoto (Osaka Univ.), Y. Mitsuyama (Kochi Univ. of Tech.), and T. Onoye (Osaka Univ.), "Neutron-Induced Soft Errors and Multiple Cell Upsets in 65-nm 10T Subthreshold SRAM," IEEE Transactions on Nuclear Science, vol. 58, no. 4, pp. 2097-2102, August 2011, DOI: 10.1109/TNS.2011.2159993.

- 64. Takashi Matsumoto, Hiroaki Makino(Kyoto Univ.), Kazutoshi Kobayashi(Kyoto Institute of Tech.), Hidetoshi Onodera(Kyoto Univ.), "Multi-core LSI Lifetime Extension by NBTI-Recovery-bases Self-healing," Proc. of International Conference on Solid State Devices and Materials, pp. 1045-1046, September 2011.

- 65.H. Konoura (Osaka Univ.), Y. Mitsuyama (Kochi Univ. of Tech.), M. Hashimoto, and T. Onoye (Osaka Univ.), "Implications of Reliability Enhancement Achieved by Fault Avoidance on Dynamically Reconfigurable Architecture," Proc. of International Conference on Field Programmable Logic and Applications (FPL), pp. 189–194, September 2011, DOI: 10.1109/FPL.2011.108.

- 66.T. Kameda, H. Konoura (Osaka Univ.), Y. Mitsuyama (Kochi Univ. of Tech.), M. Hashimoto, and T. Onoye (Osaka Univ.), "NBTI Mitigation by Giving Random Scan-In Vectors during Standby Mode," Proc. of International Workshop on Power And Timing Modeling, Optimization and Simulation (PATMOS), pp. 152-161, September 2011, DOI: 10.1007/978-3-642-24154-3\_16.

- 67.J. Kawashima, H. Tsutsui, H. Ochi, and T. Sato (Kyoto Univ.), "A Design Strategy for Sub-Threshold Circuits Considering Energy-Minimization and Yield-Maximization," Proc. of 2011 IEEE International SOC Conference (SOCC), pp.57–62, Sep. 2011, DOI: 10.1109/SOCC.2011.6085076.

- 68.T. Sato, T. Kozaki, T. Uezono, H. Tsutsui, and H. Ochi, "A Device Array for Efficient Bias-Temperature Instability Measurements," Proc. of 2011 European Solid-State Device Research Conference (ESSDERC), pp.143-146, Sep. 2011, DOI: 10.1109/ESSDERC.2011.6044214.

- 69. Norihiro Kamae, Akira Tsuchiya, and Hidetoshi Onodera (Kyoto Univ.), "An Area Effective Forward/Reverse Body Bias Generator for Within-Die Variability Compensation," Proceedings of 2011 IEEE Asian Solid-State Circuits Conference, pp. 217-220, November 2011, DOI: 10.1109/ASSCC.2011.6123641.

- 70.Hidetoshi Onodera(Kyoto Univ.), "Dependable VLSI Program in Japan Program Overview and the Current Status of Dependable VLSI Platform Project —," Proc. of 2011 Asian Test Symposium, pp. 492–495, November 2011, DOI: 10.1109/ATS.2011.56.

- 71.Bishnu Prasad Das, Hidetoshi Onodera(Kyoto Univ.), "Reconfigurable Array-Based Area-Efficient Test Structure for Standard Cell Characterization," Proc. of 2011 International Workshop on RTL and Higl Level Testing, pp.113-118, November 2011.

- 72.J. Furuta(Kyoto University), R. Yamamoto, K. Kobayashi(KIT), and H. Onodera(Kyoto University), "Correlations between Well Potential and SEUs Measured by Well-Potential Perturbation Detectors in 65nm," IEEE Asian Solid-State Circuits Conference, pp.209-212, Nov. 2011, DOI: 10.1109/ASSCC.2011.6123639.

- 73.C. Hamanaka, R. Yamamoto(Kyoto Institute of Tech.), J. Furuta(Kyoto Univ.), K. Kubota, K. Kobayashi(Kyoto Institute of Tech.), and H. Onodera(Kyoto Univ.), "Variation-Tolerance of a 65-nm Error-Hardened Dual-Modular-Redundancy Flip-Flop Measured by Shift-Register-Based Monitor Structures," IEICE Trans. on Fundamentals of Electronics, Communications and Computer Sciences, vol.E94-A, no.12, pp. 2669-2675, Dec. 2011, DOI: 10.1587/transfun.E94.A.2669.

- 74.R. Yamamoto, C. Hamanaka(Kyoto Institute of Tech.), J. Furuta(Kyoto Univ.), K. Kobayashi(Kyoto Institute of Tech.), and H. Onodera(Kyoto Univ.), "An Area-efficient 65 nm Radiation-Hard Dual-Modular Flip-Flop to Avoid Multiple Cell Upsets," IEEE Trans. on Nuclear Science, vol.58, no.6, pp.3053-3059, Dec. 2011, DOI: 10.1109/TNS.2011.2169457.

- 75.H. Konoura (Osaka University), Y. Mitsuyama (Kochi Univ. of Tech.), M. Hashimoto, and T. Onoye (Osaka Univ.), "Stress Probability Computation for Estimating NBTI-Induced Delay Degradation," IEICE Trans. on Fundamentals of Electronics, Communications and Computer Sciences, vol. E94-A, no. 12, pp.2545-2553, December 2011, DOI: 10.1587/transfun.E94.A.2545.

- 76.H. Fuketa (Univ. of Tokyo), M. Hashimoto (Osaka Univ.), Y. Mitsuyama (Kochi Univ. of Tech.), and T. Onoye (Osaka Univ.), "Adaptive Performance Compensation with In-Situ Timing Error Predictive Sensors for Subthreshold Circuits," IEEE Transactions on VLSI Systems, vol.20, no.2, pp.333-343, Feb. 2012, DOI: 10.1109/TVLSI.2010.2101089.

- 77. Shuichi Fujimoto, Takashi Matsumoto, Hidetoshi Onodera(Kyoto Univ.), "Inhomogenious Ring Oscillator for WID Variability and RTN Characterization," Proc. of 25th IEEE International Conference on Microelectronic Test Structures, pp.25–30, March 2012, DOI: 10.1109/ICMTS.2012.6190607.

- 78. Shinichi Nishizawa, Hidetoshi Onodera(Kyoto Univ.), "Ring Oscillator with Calibration Circuit for Accurate On-Chip IR-drop Measurement," Proc. of 25th IEEE International Conference on Microelectronic Test Structures, pp.3–8, March 2012, DOI: 10.1109/ICMTS.2012.6190602.

- 79. Takashi Sato, Hiromitsu Awano, Hirofumi Shimizu, Hiroshi Tsutsui, and Hiroyuki Ochi, "Statistical observations of NBTI-induced threshold voltage shifts on small channel-area devices," Proc. of International Symposium on Quality Electrical Design (ISQED), pp.306-311, March 2012, DOI:10.1109/ISQED.2012.6187510.

- 80.T. Matsumoto, H. Makino(Kyoto University), K. Kobayashi(KIT), and H. Onodera(Kyoto University), "Multicore Large-Scale Integration Lifetime Extension by Negative Bias Temperature Instability Recovery-Based Self-Healing," Japanese Journal of Applied Physics, vol.51, no.4, 04DE02, Apr. 2012, DOI: 10.1143/JJAP.51.04DE02.

- 81.J. Furuta(Kyoto University), R. Yamamoto, K. Kobayashi(KIT), and H. Onodera(Kyoto University), "Evaluation of Parasitic Bipolar Effects on Neutron-Induced SET Rates for Logic Gates," Proc. of the International Reliability Physics Symposium (IRPS) 2012, pp. SE.5.1-SE.5.5, April 2012, DOI: 10.1109/IRPS.2012.6241930.

- 82.K. Zhang, R. Yamamoto(KIT), J. Furuta(Kyoto University), K. Kobayashi(KIT), H. Onodera(Kyoto University), "Parasitic bipolar effects on soft errors to prevent simultaneous flips of redundant flip-flops," Proc. of the International Reliability Physics Symposium (IRPS) 2012, pp. 5B.2.1-5B.2.4, April 2012, DOI: 10.1109/IRPS.2012.6241844.

- 83.R. Harada (Osaka Univ.), Y. Mitsuyama (Kochi Univ. of Tech.), M. Hashimoto, and T. Onoye (Osaka Univ.), "SET Pulse-Width Measurement Eliminating Pulse-Width Modulation and Within-Die Process Variation Effects," Proc. of International Reliability Physics Symposium (IRPS), pp. SE.1.1—SE.1.6, April 2012, DOI: 10.1109/IRPS.2012.6241926.

- 84.Michihiro Shintani and Takashi Sato(Kyoto Univ.), "A Bayesian-Based Process Parameter Estimation using IDDQ Current Signature," Proc. of IEEE VLSI Test Symposium (VTS), pp.86-91, Apr. 2012, DOI: 10.1109/VTS.2012.6231085.

- 85.M. Yabuuchi, and K. Kobayashi(Kyoto Institute of Technology), "NBTI-Induced Delay Degradation Analysis of FPGA Routing Structures," IPSJ Transactions on System LSI Design Methodology, vol.5, pp.143-149, Aug. 2012, DOI: 10.2197/ipsjtsldm.5.143.

- 86.T. Kameda, H. Konoura, D. Alnajjar (Osaka Univ.), Y. Mitsuyama (Kochi Univ. of Tech.), M. Hashimoto, and T.Onoye (Osaka Univ.), "A Predictive Delay Fault Avoidance Scheme for Coarse-Grained Reconfigurable Architecture," Proceedings of International Conference on Field Programmable Logic and Applications (FPL), pp. 615 618, August 2012, DOI: 10.1109/FPL.2012.6339220.

- 87.M. Masuda, K. Kubota, R. Yamamoto(KIT), J. Furuta(Kyoto University), K. Kobayashi(KIT), and H. Onodera(Kyoto University), "A 65 nm Low-Power Adaptive-Coupling Redundant Flip- Flops," Proc. of the conference on Radiation and its Effects on Components and Systems, pp. I-1-I-5, Sept. 2012.

- 88. Masahiro Kondo, Shinichi Nishizawa, Tohru Ishihara, Hidetoshi Onodera (Kyoto University), "A Standard Cell Optimization Method for Near-Threshold Voltage Operations," Proc. of the International Workshop on Power and Timing Modeling, Optimization and Simulation (PATMOS) 2012, pp. 32-41, Sept. 2012.

- 89. Takashi Matsumoto (Kyoto Univ.), Kazutoshi Kobayashi (KIT), Hidetoshi Onodera (Kyoto Univ.), "Impact of Body-Biasing Technique on RTN-induced Delay Fluctuation," Proc. of 2012 International Conference on Solid State Devices and Materials (SSDM2012), pp.1130-1131, Sept. 2012.

- 90. Shohei Nishimura, Takashi Matsumoto (Kyoto Univ.), Kazutoshi Kobayashi (KIT), Hidetoshi Onodera (Kyoto Univ.), "Impact on delay due to random telegraph noise under low voltage operation in logic circuits," Proc. of 2012 International Conference on Solid State Devices and Materials (SSDM2012), pp.170-171, Sept. 2012.

- 91.SinNyong Kim, Akira Tsuchiya, Hidetoshi Onodera(Kyoto University), "Modeling of Single-Event Failures in Divider and PFD of PLL based on Jitter Analysis," Proc. of the conference on Radiation and its Effects on Components and Systems(RADECS) 2012, PF-3, Sept. 2012.

- 92.R. Harada (Osaka Univ.), Y. Mitsuyama (Kochi Univ. of Tech.), M. Hashimoto, and T. Onoye (Osaka University), "Impact of NBTI-Induced Pulse-Width Modulation on SET Pulse-Width Measurement," Proceedings of European Conference on Radiation and Its Effects on Components and Systems (RADECS), G-2, Sep. 2012.

- 93. Shinichi Nishizawa, Tohru Ishihara, Hidetoshi Onodera (Kyoto University), "A Flexible Structure of Standard Cell and Its Optimization Method for Near-Threshold Voltage Operation," Proceedings of the 30th IEEE International Conference on Computer Design (ICCD), pp235-240, Oct. 2012.

- 94.T. Matsumoto(Kyoto Univ.), K. Kobayashi(KIT), and H. Onodera(Kyoto Univ.), "Impact of

- Body-Biasing Technique on RTN-induced CMOS Logic Delay Uncertainty," Proc. of IEEE/ACM Workshop on Variability Modeling and Characterization, Nov. 2012.

- 95.A.K.M. Mahfuzul Islam, and H. Onodera (Kyoto Univ.), "On-chip Detection of Process Shift and Process Spread for Silicon Debugging and Model-Hardware Correlation," Proceedings of IEEE 21st Asian Test Symposium 2012, pp.350-354, Nov. 19, 2012.

- 96. Norihiro Kamae, Akira Tsuchiya, Hidetoshi Onodera (Kyoto University), "A Body Bias Generator Compatible with Cell-based Design Flow for Within-die Variability Compensation," Proc. of the IEEE Asian Solid-State Circuits Conference (A-SSCC) 2012, pp.389-392, November 2012.

- 97. Islam A.K.M Mahfuzul, Norihiro Kamae, Tohru Ishihara, and Hidetoshi Onodera(Kyoto University), "A Built-in Self-adjustment Scheme with Adaptive Body Bias using P/N-sensitive Digital Monitor Circuits," Proc. of the IEEE Asian Solid-State Circuits Conference(A-SSCC) 2012, pp.101-104, November 2012.

- 98.T. Matsumoto (Kyoto Univ.), K.Kobayashi (KIT), and H. Onodera (Kyoto Univ.), "Impact of Random Telegraph Noise on CMOS Logic Delay Uncrtainty under Low Voltage Operation," Technical Digest of IEEE International Electron Devices Meeting, p.581-584, Dec. 10, 2012.

- 99.S. Tanihiro, M. Yabuuchi, and K. Kobayashi(KIT), "Measurement Results of Substrate Bias Dependency on Negative Bias Temperature Instability Degradation in a 65 nm Process," Components, Packaging, and Manufacturing Technology Symposium Japan, pp. 289–292, Dec. 14, 2012.

- 100.J. Yao(NAIST), S. Okada, M. Masuda, K. Kobayashi(KIT), and Y. Nakashima(NAIST), "DARA: A Low-Cost Reliable Architecture Based on Unhardened Devices and Its Case Study of Radiation Stress Test," IEEE Trans. on Nuclear Science, vol.59, no.6, pp. 2852 2858, Dec. 2012, DOI: 10.1109/TNS.2012.2223715.

- 101.R. Harada (Osaka Univ.), S. Abe (Kyushu Univ.), H. Fuketa (Univ. Tokyo), T. Uemura (Fujitsu Semiconductor), M. Hashimoto (Osaka Univ.), and Y. Watanabe (Kyushu Univ.), "Angular Dependency of Neutron Induced Multiple Cell Upsets in 65-nm 10T Subthreshold SRAM," IEEE Transactions on Nuclear Science, vol. 59, no. 6, pp. 2791-2795, December 2012, DOI: 10.1109/TNS.2012.2224373.

- 102.D. Alnajjar (Osaka Univ.), Y. Mitsuyama (Kochi Univ. of Tech.), M. Hashimoto, and T. Onoye (Osaka Univ.), "Static Voltage Over-Scaling and Dynamic Voltage Variation Tolerance with Replica Circuits and Time Redundancy in Reconfigurable Devices," Proceedings of International Conference on ReConFigurable Computing and FPGAs (ReConFig), December 2012, DOI: 10.1109/ReConFig.2012.6416787.

- 103. Hiromitsu Awano, Hiroshi Tsutsui, Hiroyuki Ochi, and Takashi Sato (Kyoto Univ.), "Bayesian Estimation of Multi-Trap RTN Parameters using Markov Chain Monte Carlo Method," IEICE Trans. Fundamentals, Vol. E95-A, No. 12, pp. 2272-2283, Dec. 2012, DOI: 10.1587/transfun. E95. A. 2272.

- 104. Junya Kawashima, Hiroshi Tsutsui, Hiroyuki Ochi, and Takashi Sato (Kyoto Univ.), "Variability-Aware Energy-Minimization Strategy for Subthreshold Circuits," IEICE Trans. Fundamentals, Vol. E95-A, No. 12, pp. 2242-2250, Dec. 2012, DOI: 10.1587/transfun. E95. A. 2242.

- 105.Islam A.K.M. Mahfuzul, Akira Tsuchiya(Kyoto University), Kazutoshi Kobayashi(KIT), Hidetoshi Onodera(Kyoto University), "Variation-sensitive Monitor Circuits for Estimation of Global Process Parameter Variation," IEEE Trans. Semiconductor Manufacturing, vol. 25, No. 4, pp.571–580, Dec. 2012. DOI: 10.1109/TSM.2012.2198677.

- 106.Bishnu Prasad Das and Hidetoshi Onodera(Kyoto University), "Area-Efficient Reconfigurable-Array-Based Oscillator for Standard Cell Characterization," IET Circuits, Devices & Systems, vol. 6, No. 6, pp.429-436, Dec. 2012. DOI: 10.1049/iet-cds.2012.0012.

- 107.Michihiro Shintani and Takashi Sato(Kyoto Univ.), "An Adaptive Current-Threshold Determination for IDDQ Testing Based on Bayesian Process Parameter Estimation," Proc. of Asia and South Pacific Design Automation Conference (ASP-DAC), pp.614-619, Jan. 2013. DOI: 10.1109/ASPDAC.2013.6509666.

- 108. J. Furuta(Kyoto Univ.), R. Yamamoto, K. Kobayashi(KIT), and H. Onodera(Kyoto Univ.), "Effects of Neutron-Induced Well Potential Perturbation for Multiple Cell Upset of Flip-Flops in 65 nm," IEEE Trans. on Nuclear Science, vol.60, no.1, pp. 213-218, Feb. 2013, DOI: 10.1109/TNS.2012.2229718.

- 109.密山幸男(高知工科大学)、尾上孝雄(大阪大学)、小野寺秀俊(京都大学)、「再構成可能ディペンダブル VLSI プラットホーム」、電子情報通信学会学会誌、pp.95-99、Feb. 2013.

- 110.Michihiro Shintani and Takashi Sato(Kyoto Univ.), "Device-parameter Estimation Through IDDQ Signatures," IEICE Transactions on Information and Systems, Vol.E96-D, No.2, pp.303-313, Feb. 2013, DOI: 10.1587/transinf.E96.D.303.

- 111.T. Amaki, M. Hashimoto, and T. Onoye (Osaka Univ.), "Jitter Amplifier for Oscillator-Based True Random Number Generator," IEICE Trans. on Fundamentals of Electronics, Communications and Computer Sciences, vol. E96-A, no. 3, pp. 684-696, March 2013, DOI: 10.1587/transfun.E96.A.684.

- 112.M. Hashimoto (Osaka Univ.), "Robust Subthreshold Circuit Design to Manufacturing and Environmental Variability," ECS Transactions, vol. 52, no. 1 pp. 1079—1084, March 2013, DOI: 10.1149/05201.1079ecst.

- 113. Takashi Imagawa, Hiroshi Tsutsui, Hiroyuki Ochi, and Takashi Sato(Kyoto Univ.), "High-Speed DFG-Level SEU Vulnerability Analysis for Applying Selective TMR to Resource-Constrained CGRA," Proc. of International Symposium on Quality Electrical Design (ISQED), pp.554-561, March 2013. DOI: 10.1109/ISQED.2013.6523663.

- 114.Hiromitsu Awano, Hiroshi Tsutsui, Hiroyuki Ochi, and Takashi Sato(Kyoto Univ.), "Multi-Trap RTN Parameter Extraction Based on Bayesian Inference," Proc. of International Symposium on Quality Electrical Design (ISQED), pp.613-618, March 2013. DOI: 10.1109/ISQED.2013.6523672.

- 115. Shinichi Nishizawa, Tohru Ishihara, Hidetoshi Onodera (Kyoto Univ.), "Analysis and Comparison of XOR Cell Structures for Low Voltage Circuit Design," Proc. of 2013 International Symposium on Quality Electronic Design (ISQED), pp.719–725, Mar. 2013.

- 116.Zoltan Endre Rakosi, Masayuki Hiromoto, Hiroshi Tsutsui, Takashi Sato, Yukihiro Nakamura, and Hiroyuki Ochi(Kyoto Univ.), "Hot-Swapping Architecture with Back-Biased Testing for Mitigation of Permanent Faults in Functional Unit Array," Proc. of Design, Automation & Test in Europe (DATE), pp.535-540, March 2013. DOI: 10.7873/DATE.2013.120.

- 117. Takashi Imagawa, Hiroshi Tsutsui, Hiroyuki Ochi, and Takashi Sato(Kyoto Univ.), "A Cost-Effective Selective TMR for Heterogeneous Coarse-Grained Reconfigurable Architectures Based on DFG-Level Vulnerability Analysis," Proc. of Design, Automation & Test in Europe (DATE), pp.701-706, March 2013. DOI: 10.7873/DATE.2013.151.

- 118.D. Alnajjar (Osaka Univ.), Y. Mitsuyama (Kochi Univ. of Tech.), M. Hashimoto, and T. Onoye (Osaka Univ.), "PVT-Induced Timing Error Detection Through Replica Circuits and Time Redundancy in Reconfigurable Devices," IEICE Electronics Express (ELEX), vol. 10, no. 5, April 2013, DOI: 10.1587/elex.10.20130081.

- 119. Takashi Imagawa, Hiroshi Tsutsui, Hiroyuki Ochi, and Takashi Sato (Kyoto Univ.), "A Cost-Effective Selective TMR for Coarse-Grained Reconfigurable Architectures Based on DFG-Level Vulnerability Analysis," IEICE Transactions on Electronics, Vol. E96-C, No. 4, pp. 454-462, Apr. 2013. DOI: 10.1587/transele. E96. C. 454.

- 120.T. Matsumoto (Kyoto Univ.), K. Kobayashi (KIT), H. Onodera (Kyoto Univ.), "Impact of Body-Biasing Technique on Random Telegraph Noise Induced Delay Fluctuation", Japanese Journal of Applied Physics, vol 52, No. 4, 04CE05, April 2013. DOI: 10.7567/JJAP.52.04CE05.

- 121. J. Furuta (Kyoto Univ.), K. Kobayashi (Kyoto Institute of Tech.), H. Ondera (Kyoto Univ.), "Impact of Cell Distance and Well-contact Density on Neutron-induced Multiple Cell Upsets," Proc. of 2013 IEEE International Reliability Physics Symposium (IRPS), pp.6C.3.1-6C.3.4, April 2013. DOI: 10.1109/IRPS.2013.6532053.

- 122. Hiroshi Yuasa, Hiroshi Tsutsui, Hiroyuki Ochi and Takashi Sato (Kyoto Univ.), "Parallel

- acceleration scheme for Monte Carlo based SSTA using generalized STA processing element," IEICE Transactions on Electronics, Vol.E96-C, No.4, pp.473-481, April, 2013. DOI: 10.1587/transele.E96.C.473.

- 123. Shiyi Zhang, Hiroshi Tsutsui, Hiroyuki Ochi, and Takashi Sato (Kyoto Univ.), "Histogram Propagation Based Statistical Timing Analysis using Dependent Node Selection," The 28th International Technical Conference on Circuits/Systems, Computers and Communications (ITC-CSCC 2013), pp.321-324, June 2013.

- 124. SinNyoung Kim, Akira Tsuchiya, Hidetoshi Onodera (Kyoto Univ.), "Perturbation-Immune Radiation-Hardened PLL with a Switchable DMR Structure," Proc. of IEEE 19th International On-Line Testing Symposium, pp.128-132, July 2013.

- 125. S. Fujimoto, A. K. M. M. Islam, T. Matsumoto, H. Onodera (Kyoto University), "Inhomogeneous Ring Oscillator for Within-Die Variability and RTN Characterization," IEEE Transactions on Semiconductor Manufacturing, Vol.26, No.3, pp.296-305 Aug. 2013. DOI: 10.1109/TSM.2013.2265702.

- 126. Shinichi Nishizawa and Hidetoshi Onodera (Kyoto Univ.), "A Ring Oscillator With Calibration Circuit for On-Chip Measurement of Static IR-drop," IEEE Transactions on Semiconductor Manufacturing, Vol.26, No.3, pp.306-313, Aug. 2013. DOI: 10.1109/TSM.2013.2261577.

- 127.M. Masuda, K. Kubota, R. Yamamoto(KIT), J. Furuta(Kyoto Univ.), K. Kobayashi(KIT), and H. Onodera(Kyoto Univ.), "A 65 nm Low-Power Adaptive-Coupling Redundant Flip-Flop," IEEE Trans. on Nuclear Science, vol.60, no.4, pp. 2750-2755, Aug. 2013, DOI: 10.1109/TNS.2013.2245344.

- 128.R. Harada (Osaka Univ.), Y. Mitsuyama (Kochi Univ. of Tech.), M. Hashimoto, and T. Onoye (Osaka Univ.), "Impact of NBTI-Induced Pulse-Width Modulation on SET Pulse-Width Measurement," IEEE Transactions on Nuclear Science, vol. 60, no. 4, pp.2630-2634, August 2013, DOI: 10.1109/TNS.2012.2232680.

- 129.T. Kameda, H. Konoura, D. Alnajjar (Osaka Univ.), Y. Mitsuyama (Kochi Univ. of Tech.), M. Hashimoto, and T.Onoye (Osaka Univ.), `Field Slack Assessment for Predictive Fault Avoidance on Coarse-Grained Reconfigurable Devices,' IEICE Trans. on Information and Systems, vol. E96-D, no. 8, pp. 1624-1631, August 2013, DOI: 10.1587/transinf.E96.D.1624.

- 130.T. Amaki, M. Hashimoto (Osaka Univ.), Y. Mitsuyama (Kochi Univ. of Tech.), and T. Onoye (Osaka Univ.), "A Worst-Case-Aware Design Methodology for Noise-Tolerant Oscillator-Based True Random Number Generator with Stochastic Behavior Modeling," IEEE Transactions on Information Forensics and Security, vol. 8, no. 8, pp. 1331-1342, August 2013, DOI: 10.1109/TIFS.2013.2271423.

- 131. D. Alnajjar, H. Konoura (Osaka Univ.), Y. Mitsuyama (Kochi Univ. of Tech.), H. Shimada (NAIST), K. Kobayashi (KIT), H. Kanbara (ASTEM), H. Ochi (Ritsumeikan Univ.), T. Imagawa (Kyoto Univ.), S. Noda, K. Wakabayashi (NEC), M. Hashimoto, T. Onoye (Osaka Univ.), and H. Onodera (Kyoto Univ.), "Reliability-Configurable Mixed-Grained Reconfigurable Array Supporting C-To-Array Mapping and Its Radiation Testing," Proceedings of IEEE Asian Solid-State Circuits Conference (A-SSCC), pp. 313-316, Nov. 2013, DOI: 10.1109/ASSCC.2013.6691045.

- 132. H. Konoura, D. Alnajjar (Osaka Univ.), Y. Mitsuyama (Kochi Univ., of Tech.), H. Ochi (Ritsumeikan Univ.), T. Imagawa (Kyoto Univ.), S. Noda, K. Wakabayashi (NEC), M. Hashimoto, and T. Onoye (Osaka Univ.), "Mixed-Grained Reconfigurable Architecture Supporting Flexible Reliability and C-Based Design," Proceedings of International Conference on ReConFigurable Computing and FPGAs (ReConFig.), Dec. 2013, DOI: 10.1109/ReConFig.2013.6732309.

- 133.D. Alnajjar, H. Konoura, Y. Ko (Osaka Univ.), Y. Mitsuyama (Kochi Univ. of Tech.), M. Hashimoto, and T. Onoye (Osaka Univ.), "Implementing Flexible Reliability in a Coarse Grained Reconfigurable Architecture," IEEE Transactions on VLSI Systems, Vol. 21, No. 12, pp. 2165–2178, Dec. 2013, DOI: 10.1109/TVLSI.2012.2228015.

- 134.H. Fuketa, R. Harada, M. Hashimoto, and T. Onoye (Osaka Univ.), "Measurement and Analysis of

- Alpha-Particle-Induced Soft Errors and Multiple Cell Upsets in 10T Subthreshold SRAM," IEEE Transactions on Device and Materials Reliability, in press.

- 135. H. Konoura (Osaka Univ.), T. Imagawa (Kyoto Univ.), Y. Mitsuyama (Kochi Univ. of Tech.), M. Hashimoto, T. Onoye (Osaka Univ.), "Comparative evaluation of lifetime enhancement with fault avoidance on dynamically reconfigurable devices," IEICE Trans. on Fundamentals of Electronics, Communications and Computer Sciences, in press.

- 136. H. Konoura, T. Kameda (Osaka Univ.), Y. Mitsuyama (Kochi Univ. of Tech.), M. Hashimoto, T. Onoye (Osaka Univ.), "NBTI mitigation method by inputting random scan-in vectors in standby time," IEICE Trans. on Fundamentals of Electronics, Communications and Computer Sciences, in press.

- 137.R. Harada (Osaka Univ.), Y. Mitsuyama (Kochi Univ. of Tech.), M. Hashimoto, T. Onoye (Osaka Univ.), "SET Pulse-Width Measurement Suppressing Pulse-Width Modulation and Within-die Process Variation Effects," IEICE Trans. on Fundamentals of Electronics, Communications and Computer Sciences, in press.

- 138. A.K.M. Mahfuzul Islam, and Hidetoshi Onodera, "Area-efficient Reconfigurable Ring Oscillator for Characterization of Static and Dynamic Variations," Proc. of International Conference on Solid State Devices and Materials, pp. 132-133, Sep. 2013.

- 139. A.K.M. Mahfuzul Islam, and Hidetoshi Onodera (Kyoto Univ.), "On-Chip Detection of Process Shift and Process Spread for Post-Silicon Diagnosis and Model-Hardware Correlation," IEICE Transactions on Information and Systems, vol. E96-D, no. 9, pp. 1971—1979, 2013, DOI:10.1587/transinf.E96.D.1971.

- 140. A.K.M. Mahfuzul Islam, Tohru Ishihara, and Hidetoshi Onodera, "Reconfigurable Delay Cell for Area-efficient Implementation of On-chip MOSFET Monitor Schemes," in Proceedings of the 2013 IEEE Asian Solid State Circuits Conference, pp. 125 -- 128, Nov. 2013, DOI:10.1109/ASSCC.2013.6690998.

- 141. Norihiro KAMAE, Akira TSUCHIYA, Hidetoshi ONODERA (Kyoto Univ.), "A Body Bias Generator with Low Supply Voltage for Within-die Variability Compensation," IEICE Transactions on Fundamentals, Vol. E97-A, No. 3, pp. 734 -- 740, March 2014, DOI:10.1587/transfun.E97.A.734.

- 142. SinNyoung Kim, Akira Tsuchiya, and Hidetoshi Onodera (Kyoto Univ.), "Analysis of Radiation-Induced Clock-Perturbation in Phase-Locked Loop," IEICE Transactions on Fundamentals, vol. E97-A, no. 3, pp. 768 -- 776, March 2014, DOI:10.1587/transfun.E97.A.768.

- 143. Fujita Tomohiro (Ritsumeikan Univ.), SinNyoung Kim, and Hidetoshi Onodera (Kyoto Univ.), "Computer Simulation of Radiation-Induced Clock-Perturbation in Phase-Locked Loop with Analog Behavioral Model," Proceedings of 15th International Symposium on Quality Electronic Design(ISQED), March 2014.

- 144. A.K.M. Mahfuzul Islam and Hidetoshi Onodera (Kyoto Univ.), "In-Situ Variability Characterization of Individual Transistors using Topology-Reconfigurable Ring Oscillators," Proc. 27th IEEE International Conference on Microelectronic Test Structures (ICMTS2014), March 2014.