# 研究報告書

# 「Si/III-V族半導体超ヘテロ界面の機能化と低電カスイッチ素子の開発」

研究タイプ: 通常型

研究期間: 平成 21 年 10 月~平成 25 年 3 月

研究者: 冨岡 克広

#### 1. 研究のねらい

ミスフィット転位とアンチフェーズドメインのない原子配列を精密に制御した Si/III-V 族半導体超へテロ接合界面の形成を一次元ナノ構造選択成長技術で実現し、Si/III-V 半導体接合のバンド不連続性の詳細を明らかにし、Si/III-V 族化合物半導体一次元ナノ構造接合界面のバンド不連続性を機能化することで、従来の MOSFET 特性のサブスレッショルド特性の理論限界を超えるトンネルスイッチ素子を開発する。また、シリコン CMOS 技術と整合性の高い次世代 3 次元立体ゲートトランジスタの集積プロセス技術の確立を目指す。

#### 2. 研究成果

#### (1)概要

本研究では、従来の MOSFET のスイッチ動作の理論限界を超える新型トンネルトランジスタ構造を提案・実証した。具体的には、一次元ナノ構造選択成長技術で、転位とアンチフェーズドメインのない原子配列を精密に制御した Si/III-V 族半導体ナノワイヤへテロ接合界面を形成することで、Si/III-V 半導体接合のバンド不連続性の詳細を明らかにし、極めて転位の少ない Si/III-V 半導体接合界面でトンネル輸送を生じることを明らかにした。さらに、これら Si/III-V 半導体接合界面を新しい接合界面と位置付け、MOSFET に潜在的に存在するサブスレッショルド特性の理論限界を突破できる新型トンネルトランジスタ構造を提案した。新型トンネルトランジスタ構造の作製では、垂直自立ナノ細線構造に対して、3次元的にソース・ゲート・ドレイン構造からなる縦型 3端子電極構造の作製工程と先端プロセス技術を確立した。これらの加工技術を確立することで、InAs ナノワイヤ/Si ヘテロ接合界面で生じるトンネル輸送過程を縦型トランジスタに応用し、室温で 12mV/桁の急峻なサブスレッショルド特性をもつトンネルトランジスタを実現できることを世界で初めて実証した。従来の MOSFET のサブスレッショルド特性の限界値はおよそ 60 mV/桁であるため、これらの新型トンネルトランジスタを回路に実現した場合、現行の集積回路の消費電力を 1/25 にし、待機電力を大幅に削減できる潜在性を有している。

これらの研究を通して、一次元ナノ構造による低消費・高速スイッチ特性をもつデバイスをシリコン基板上に構築し、次世代化合物半導体異種集積と立体ゲート構造の作製へ向けた3次元立体集積プロセス技術の確立と展開を促した。さらに、提案デバイスを作製する過程で、極めて転移の少ない III-V/Si ヘテロ接合界面やコヒーレント成長とプラスチック成長の境界、ヘテロ接合界面の電子特性のバンド不連続性を明らかにし、結晶成長学、電子物性へ新しい知見を提供することができた。また、ナノメートルスケールの結晶成長技術で生じる III-V/Si 接合界面に新しい物性を見出し、低電カスイッチ素子の提案・実証することで、Si-CMOS 分野における低消費電力化への可能性について、新しい界面:Si/III-V 界面の潜在性、実証することができた。

#### (2)詳細

### 研究テーマ A. Si/III-V 異種接合の結晶評価とコヒーレント成長

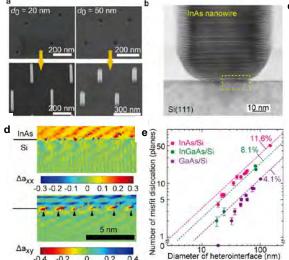

と接合界面の関係。破線は理論値。

図 1. a. Si 上 InAs ナノワイヤ選択成長の SEM 像、b.

Si/InAs ナノワイヤ接合界面の断面 TEM 像、 c. GaAs

ナノワイヤと Si 接合界面の断面 TEM 像 c. Si/GaAs

ナノワイヤ界面の  $\varepsilon_{yy}$  歪分布図。接合界面から 4 原

子層の範囲で、コヒーレント成長を示す歪層が観察さ

れている。d. Si/InAs ナノワイヤ界面の歪み分布図。 ▲がミスフィット転位の位置。e. ミスフィット転位の数

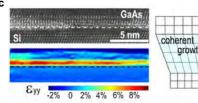

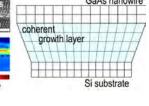

InAs、GaAs、InGaAs ナノワイヤと Si の接合界面の結晶評価を行い。微小直径からなる一次元ナノ構造の接合の場合において、格子不整合によるミスフィット転位のないコヒーレント成長を生じることを、実験的に証明した[図 1c]。さらに、格子不整合度の大きな Si/InAs, Si/InGaAs 界面においても、ナノメートルスケールの選択成長技術で、転位の入る数を理論値よりも少なくできることを明らかにした。これにより、格子不整合とナノワイヤの直径の制御で、超ヘテロ接合界面を実現することができることが分かり、他の III-V 化合物半導体ナノワイヤと Si の組み合わせにおいても、同様のコヒーレント成長を実現できることを示している。

### 研究テーマ B. Si/III-V ナノワイヤ固相界面の電子物性評価

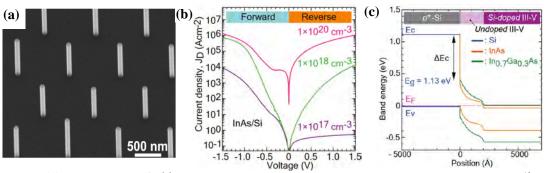

Si基板上に直径 100 nm、高さ 1  $\mu$ mからなるInAsナノワイヤアレイを作製し、縦型二端子電流電圧特性を調べた[**図 2(a)**]。n型InAs基板上のInAsナノワイヤアレイではオーミック特性を示す一方で、Si基板上のInAsナノワイヤの場合、Si/InAs接合間のバンド不連続性により図 1(b)に示すバンド構造からなる電流電圧特性を示した」。さらに、高濃度p型シリコン基板上においては、江崎トンネル輸送による不性抵抗微分曲線が得られた。これは**図 2(c)**に示すようなバンド不連続性が接合界面で生じたと考えられ、高濃度p型シリコンでは、フェルミ準位は価電子帯に入るためバンド間トンネル輸送を生じたと考えられる。また、p-Si/n-InAs接合界面は、staggered Type-IIに近いバンド不連続性を示すことを明らかにした。

**図 2 (a)** p<sup>+</sup>-Si 上に作製した *undope*-InAs/n-InAs ナノワイヤアレイの SEM 像、**(b)** *undope*-InAs/n-InAs ナノワイヤの縦型 2 端子 I-V 曲線、**(c)** p<sup>+</sup>-Si/*undope*-InAs/n-InAs 接合界面のバンドアライメントのシミュレーション結果。

また、InGaAsナノワイヤとSi接合界面においても同様の特性評価を行なった。InGaAsナノワイ ヤの場合にも同様に、図 2(c)に示すような価電子帯のバンドオフセット値が大きい特性を示した。 選択成長法により接合界面に生じる転位・欠陥の発生を抑制したp-Si/III-Vナノワイヤの接合界 面を従来の化合物半導体ヘテロ接合のように機能化することで新しいデバイス原理に応用する ことができることを示し、それらを利用した Si/III-V ヘテロ接合界面を応用したトンネル FET を作 製できることを示した。

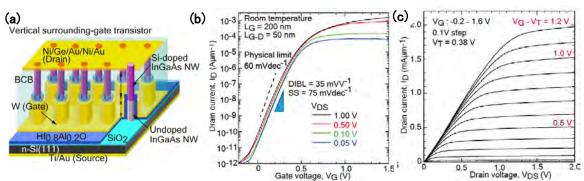

# 研究テーマ C. ナノワイヤ縦型トランジスタ作製プロセスの確立

Si基板上のInGaAs/InP/InAlAs/InGaAsコア・マルチシェルナノワイヤ作製技術にシラン(SiH4)に よるn型ドーピングを導入し、縦型トランジスタ作製プロセスを用いた集積技術を最適化している。 図3はデバイス特性と、スイッチング特性である。Si基板上の半導体ナノワイヤで、世界にさきが けてHEMT構造を実現した結果である。Si上III-Vナノワイヤ縦型トランジスタでSi-MOSFETのスイ ッチング特性を上回る性能を示すことができた<sup>2</sup>。

図 3 (a) ナノワイヤ縦型トランジスタの SEM 像、(b) ナノワイヤ HEMT の伝達特性。室温で MOSEFT の理想限界(SS = 60 mV/dec)に近いスイッチ特性を示す。(c) Si 上のナノワイヤ HEMT の出力特性。

# 研究テーマ D. 急峻なサブスレッショルド特性をもつ InAs/Si ヘテロ接合型トンネルトランジスタ

#### (低電カスイッチ)の動作実証

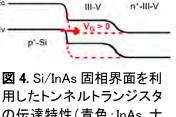

ンネルトランジスタの動作実証を 行った。提案する固相界面では、 図4に示すように、従来の MOSFETの物理限界を突破(最小 💆 SS = 12 mV/dec, 平均SS = 21 V/dec)することを実証した3。

10-6 VDS = 1.00 V Si基板上のInAsナノワイヤについ て、Si/InAs固相界面を利用したト 10-7 10-8 SO 10-1 04 mV/de n'-III-V 10-10-1 10-1 -0.5 0 0.5 Gate voltage, VG (V)

Gate

Drain

Source

の伝達特性(青色:InAs ナ ノワイヤ縦型トランジスタ、 赤色:トンネルトランジスタ)

急峻なSS特性を実現するため

には、ナノワイヤ直径の微細化で、接合界面のミスフィット転位の発生を抑制することが重要で あることを明らかにし、ナノワイヤチャネルの伝導性がスイッチング特性の立ち上がり電圧制御 の重要な要因となることを明らかにした。

### 3. 今後の展開

本研究では、従来のMOSFETのデバイス動作を超えるIII-V族化合物半導体ナノワイヤによる低消費・高速スイッチ特性をもつスイッチ素子をSi基板上に集積する結晶成長技術と3次元集積プロセス技術の展開を確立した。また、ナノメートルスケールの結晶成長技術で生じるIII-V/Si接合界面に新しい物性を見出し、低電カスイッチ素子の提案・実証することで、Si-CMOS分野における低消費電力化への可能性について、新しい界面: Si/III-V界面の潜在性、実証することができた。今後は、本研究で得られた低電カスイッチ素子を実用化するために、(i) p型トンネルFETの作製、(ii) CMOS/基本論理回路の試作、(iii) Si(100)上におけるSi/III-Vへテロ接合界面型トンネルFETの集積、(iv)トンネル電流の高電流化技術の研究を実施し、実用化への道筋を確固たるものにする予定である。

### 4. 自己評価

一次元ナノ構造選択成長技術で、転位とアンチフェーズドメインのない原子配列を精密に制御した Si/III-V 族半導体へテロ接合界面を形成することで、Si/III-V 半導体接合のバンド不連続性の詳細を明らかにし、Si-MOSFET のサブスレッショルド係数の理論限界を大幅に上回るトンネルFET の作製し、Si/III-V へテロ接合界面の潜在性を実証した。また、Si-CMOS 技術と整合性の高い次世代 3 次元集積プロセス技術確立した。これらの研究成果から、当初の目標であったSi/III-V へテロ接合界面の目標(i)新しい物性・概念の創成(初期目標)、(ii) デバイスプロセス・原理の構築(中期目標)、(iii)次世代デバイスとしての認知と実用化(後期目標)について、概ね予定通り研究項目を進めることができたと考えられる。また、次世代 LSI 回路の低消費電力化を実現する基本素子として Si/III-V ヘテロ接合界面が有効であることを広く提案・実証することができた。

### 5. 研究総括の見解

冨岡研究者は、JSTの専任研究者として北大集積センターの福井教授のもとで研究を進める 化合物半導体デバイスの研究者です。彼はInAsのナノワイヤを用いたトンネル接合型電界効果 トランジスタをシリコン基板上に作製するという提案によりさきがけに採択されました。

シリコン LSI は、リソグラフィの微細化の限界、スイッチ速度の限界、消費電力低減の限界などにより、高集積化の転機を迎えています。これを克服するための方法として、富岡研究者は化合物半導体でナノサイズの縦型トランジスタを作るとともに、化合物半導体/シリコン界面のバンド不連続性を利用したトンネル接合を用いて立ち上がりの急峻なスイッチ特性を得ることを提案しました。

はじめに、シリコン基板上に選択成長した InAs、GaAs、InGaAs ナノワイヤと基板との接合界面の結晶評価を行い、微小直径からなる一次元ナノ構造の接合の場合において、格子不整合によるミスフィット転位のないコヒーレント成長を生じることを、実験的に証明しました。

つぎに、ナノワイヤアレイの縦型二端子電流電圧特性を調べた結果、選択成長法により接合界面に生じる転位・欠陥の発生を抑制した p-Si/III-V ナノワイヤの接合界面を従来の化合物半導体へテロ接合のように機能化することで新しいデバイス原理に応用することができること、それらを利用した Si/III-V ヘテロ接合界面を応用したトンネル FET を作製できることを明かにしました。

これを受けて、Si 基板上の III-V 半導体コアシェル構造のナノワイヤで、世界にさきがけて

HEMT 構造を実現し、Si 上縦型トランジスタで Si-MOSFET のスイッチング特性を上回る性能を示すことを実証しました。さらに、Si 基板上の InAs ナノワイヤについて、Si/InAs 固相界面を利用したトンネルトランジスタの動作実証を行い、従来の MOSFET の物理限界(SS=60mV/dec)をはるかに超える最小 SS = 12 mV/dec, 平均 SS = 21 V/dec という急峻なスイッチ特性が得られること、これにより従来の 1/10 の省電力化が図れることを明らかにしました。この成果は、新聞等で大きく報道されるとともに、インテル、IBM はじめ世界の半導体産業に大きなインパクトを与えました。

このように、冨岡研究者の研究は、結晶工学的基礎研究をベースに、匠の技ともいうべき半導体プロセス技術を駆使して、世界最高レベルの半導体特性を実現したもので、真のイノベーションにつながる研究成果として極めて高く評価されます。この成果は、JST 直雇用という研究に専念できる環境があればこそできたものであるという点にも注目すべきでしょう。

# 6. 主な研究成果リスト

#### (1)論文(原著論文)発表

- 1. <u>K. Tomioka</u>, M. Yoshimura, and T. Fukui, "A III-V nanowire channel on silicon for high-performance vertical transistors" *Nature*, Vol. 488, pp.189-192 (2012).

- 2. <u>K. Tomioka</u>, T. Tanaka, S. Hara, K. Hiruma, T. Fukui, "III-V Nanowires on Si Substrate: Selective-Area Growth and Device Applications", *IEEE J. Selec. Topic Quant. Elec.*, Vol. 17, No. 4, pp.1112-1129 (2011).

- 3. <u>K. Tomioka</u> and T. Fukui, "Tunnel field-effect transistor using InAs nanowire/Si heterojunction", *Appl. Phys. Lett.*, Vol. 98, pp.083114-1 ~ 3 (2011).

- K. Tomioka and T. Fukui, "Steep-slope Tunnel Field-Effect Transistors using III-V Nanowire/Si Heterojunction" IEEE VLSI Technology 2012 Tech. Dig. pp.47-48 (2012).

- K. Tomioka, M. Yoshimura, T. Fukui, "Vertical InGaAs Nanowire Surrounding-Gate Transistors with High-k Gate Dielectrics on Si Substrate", *IEEE IEDM Tech. Dig.* pp.773-776 (2011).

#### (2)特許出願

研究期間累積件数:8件

(3) その他の成果(主要な学会発表、受賞、著作物等)

### 【受賞】

第57回応用物理学関係連合講演会応用物理学会講演奨励賞「MOVPE選択成長法と再成長によるシリコン基板上の GaAs/InAs/GaAs ナノワイヤ量子井戸の作製」社団法人応用物理学会

### 【国際会議】

本研究に関連した招待講演:計20件、内第一発表者6件

<u>K. Tomioka</u>, J. Motohisa, S. Hara, K. Hiruma, and T. Fukui: "III-V Semiconductor Nanowires on Si: Selective Area MOVPE and Their Device Applications (招待講演)" MRS spring meeting 2011, USA, April 27 (2011).

# 【著作物】

- 1. Katsuhiro Tomioka and Takashi Fukui: Semiconductor Nanowire and Their Optical Applications, (担当:分担執筆, 範囲:Chapter 3: III-V Semiconductor Nanowires on Si by Selective-Area Metal-Organic Vapor Phase Epitaxy.) Springer 2012 年 1月 ISBN:3642224792

- 2. 冨岡克広、福井孝志、「半導体ナノワイヤデバイスの新展開」応用物理 81 号 1 巻、59-64 (2012) 2012 年 1 月

- 3. Junichi Motohisa, Katsuhiro Tomioka, Bin Hua, Kumar S. K. Varadwaj, Shinjiroh Hara, Kenji Hiruma and Takashi Fukui: Advances in III-V Semiconductor Nanowires and Nanodevices, edited by J. Li, D. Wang, and R. R. LaPierre (担当:分担執筆, 範囲:III-V Semiconductor Nanowire Light Emitting Diodes and Lasers) Bentham Science Publisher 2011年11月4: 冨岡克広、福井孝志、「シリコン基板を用いた新構造発光素子の開発」月刊ディスプレイ7号39-46 (2010) 2010年7月

# 【プレスリリース】

1. 「トランジスターの理論限界を突破 次世代省エネデバイス実現へ」(2012 年 6 月) <a href="http://www.jst.go.jp/pr/announce/20120613-2/index.html">http://www.jst.go.jp/pr/announce/20120613-2/index.html</a>