# 戦略的創造研究推進事業 CREST 研究領域「ディペンダブル VLSI システムの 基盤技術」

研究課題「組込みリアルタイムシステム用ディペンダブル SoC 及び SiP に関する基盤技術の研究」

研究終了報告書

研究期間 平成21年10月~平成27年3月

研究代表者:山﨑 信行 (慶應義塾大学 大学院理工学研究科 教授)

# §1 研究実施の概要

# (1) 実施概要

本研究は、組込みリアルタイムシステムの構築をターゲットとし、SoC(System-on-Chip)及びSiP(System-in-Package)をコデザインすることでディペンダブルかつ実用的なVLSIシステム実現する基盤技術に関する研究を行った。本研究がターゲットとしている組込みリアルタイムシステムは、産業的にも技術的にも、今後の日本にとって非常に重要な位置を占め続けると考えられる。従来、組込みリアルタイムシステムに関する研究はソフトウェアに関するものがほとんどであり、時間粒度が 1msec 程度のシステムを対象としていた。それに対して本研究開発では、 $10\mu$  sec 程度の時間粒度を達成すると共に、ディペンダブルで超小型・高機能・低消費電力である組込みリアルタイムシステムを構築するための基盤技術を構築した。本研究では、基盤ソフトウェア(ディペンダブルオペレーティングシステム)、基盤ハードウェア(ディペンダブルアーキテクチャ及びディペンダブル SoC)、基盤パッケージ(ディペンダブル SiP)、及び組込みアプリケーション(先端ロボット応用によるディペンダビリティ評価)の大きく4つにテーマ(グループ)を分けつつも、相互に密接な連携を保ちつつ、コデザインを行いながら研究開発を行った。

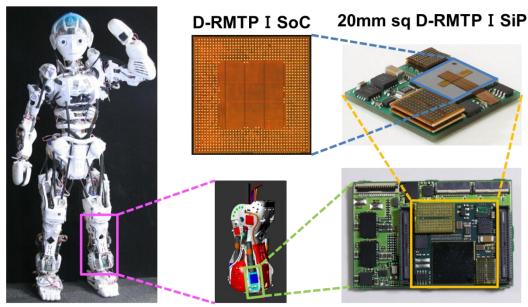

Humanoid Kojiro Leg Module (3D CAD) 20mm D-RMTP I SiP Control Board

図 1: 研究概要図:基盤ハードウェア(D-RMTPI SoC)、基盤パッケージ(D-RMTPI SiP)、 アプリケーション(ロボット)

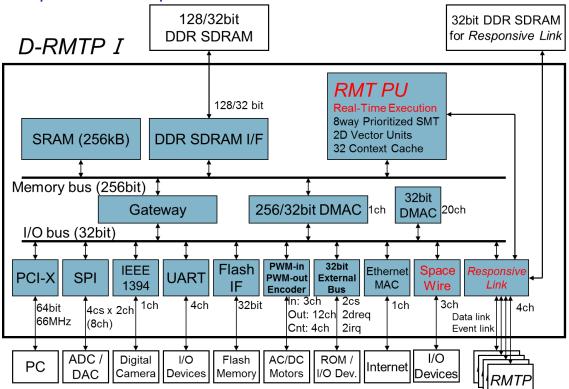

このうち、慶應義塾大学が基盤ソフトウェア及び基盤ハードウェアを、NEC プラットフォームズ (旧 NEC アクセステクニカ)が基盤パッケージを、東京大学が組込みアプリケーション (ロボット 応用)を担当した (図 1 参照)。具体的には、慶應義塾大学では、リアルタイム性を有したプロセッサアーキテクチャ、オンチップネットワーク (NoC (Network-on-Chip))、チップ 間通信リンク (Responsive Link) の研究開発を行い、それらと各種 I/O (SPI, PWM, SpaceWire 等)を集積した分散リアルタイム制御用マルチスレッド  $SoC(D-RMTP\ I:$  Dependable Responsive MultiThreaded Processor I)、普及版分散リアルタイム制御用  $SoC(I/O\ Core)$ 、分散リアルタイム制御用へテロジニアス・マルチスレッド・マルチコア  $SoC(D-RMTP\ II:$  Dependable Responsive MultiThreaded Processor II)の設計・実装・評価を行った。さらに、リアルタイムスケジューリング

アルゴリズム、ルーティングアルゴリズム、電圧周波数制御等の研究を行い、それらをリアルタイムオペレーティングシステムである独自 OS(favor OS)及び iTRON に設計・実装した。NEC プラットフォームズでは、SoC と SiP とをコデザインし、高信頼性化、小型化、高機能化を付与する SiPの研究開発を行い、30mm/20mm 角 D-RMTP I SiP、I/O Core SiP 及び 20mm 角 D-RMTP II SiPの研究開発を行った。東京大学では、D-RMTP SiP 及び I/O Core SiP を用いた各種制御基板を研究開発し、実際にロボットに組み込んで分散制御を行い、ディペンダビリティを実機評価した。最終的に、SoC/SiP/OS から構成される VLSI システムに、高信頼性化、小型化、高機能化、低消費電力化等の特徴を付与する設計・実装・評価に関する基盤技術を確立した。

## (2)顕著な成果

# <優れた基礎研究としての成果>

# 1. リアルタイム処理機構

$10\,\mu\,\mathrm{sec}$  オーダのリアルタイム処理を実現するために、マイクロプロセッサ( $RMT\,PU$ )にリアルタイム実行機構を設計・実装した[19]。具体的には、ハードウェアによるリアルタイムスケジューリング・実行を可能にする優先度付き SMT 実行( $RMT\,\mathrm{gr}$ )、スレッドの実行速度を一定にする IPC 制御機構[4,14]、コンテキストスイッチのオーバヘッドを削減するコンテキストキャッシュの要素技術を研究開発し、さらにそれらを組み合わせることにより、従来までは不可能であった  $10\,\mu\,\mathrm{sec}$  オーダのリアルタイム処理を実現するマイクロプロセッサ( $RMT\,PU$ )を研究開発した[26]。従来、リアルタイム処理は主にソフトウェアのみで実現されており、伝統的なソフトウェアによるリアルタイム処理では、 $1\mathrm{msec}$  オーダ程度のリアルタイム性しか実現することができなかった。本研究開発により、 $10\,\mu\,\mathrm{sec}$  オーダのリアルタイム処理が可能となり[37]、非常に高精度で信頼性が高く時間粒度の細かいリアルタイム処理を実現することができるようになり、産業的なインパクトも大きい。例えば、本技術をロボット制御に応用すると、制御帯域の大きな制御を実現することができ、従来までは実現困難であった非常に高速に動作するロボットや高周波数の振動を制御するようなことが実現可能となる。

# 2. リアルタイム通信機構

ディペンダビリティを有したリアルタイム通信を実現するために、ISO/IEC 24740として標準化された Responsive Link をベースにして、ロボット内の高ノイズ環境においてもディペンダブルに  $100\,\mu$  sec オーダのリアルタイム通信が可能になるリアルタイム通信機構を設計・実装した [17,22,25,27,29]。具体的には、優先度を用いたパケット追い越しによってリアルタイム通信を実現するために通信におけるプリエンプションを実現すると共に、複数種類のラインコード及びエラー訂正コードを設計・実装し、ノイズレベルによって動的にそれらのラインコードとエラー訂正コードの組み合わせを選択できるようにしてディペンダブルなリアルタイム通信を実現した。

従来、リアルタイム通信は USB や IEEE1394 のようにアイソクロナス転送を用いたソフトリアルタイム通信のみが実現されていた。これらの通信は主に PC 向けのものであり、接続ノード数が限られ(USB: 127, 1394: 63)、またバス型であるためノード数が増えると単位ノードあたりの帯域が低下し、さらにはアイソクロナス転送ではエラー訂正をサポートしておらず、分散制御用途には不向きであった。CAN は優先度をサポートしているが、エラー訂正をサポートしておらず、バス型で通信速度は 1Mbps 程度であるので、現在の分散制御システムを構築することは困難である。一方、Responsive Linkは、エラー訂正強度と通信速度のトレードオフを制御することができ、通信速度も高速(片方向 800Mbaud)である。また、バス型ではなくスイッチングを行いながらバーチャルカットスルーすることで1対1通信を行い、パケットに付与された優先度を元にノード毎にパケットの追い越しをすることで通信のプリエンプションを実現するので、リアルタイムアルゴリズムを通信に応用することが可能となる。その結果、大規模な分散リアルタイムシステム(特に分散制御システム)をトップダウンに構築することができる。さらに、ディペンダビリティを向上するために、ラインコード自体にエラー訂正能力を持たせた 4b10b というラインコードを新規に設計し、ラインコードにエラー訂正を入れ込むことを初めて実現した。通信規格は標準化しない

と意味がないので、現在、情報処理学会試行標準として 4b10b を標準化作業中である。試行標準として標準化された後、ISO/IEC において標準作業を行う予定である。これらの技術を組み合わせることにより、 $100~\mu$  sec オーダのリアルタイム性と耐ノイズ性を共に有したディペンダブルな通信を実現した。

#### 3. リアルタイムオペレーティングシステム

D-RMTP に搭載されているリアルタイム処理機構及び Responsive Link に搭載されているリアルタイム通信機構をサポートするリアルタイムオペレーティングシステムを設計・実装した。 D-RMTP の固有機能を使用することで、10usec オーダのリアルタイム処理である Responsive Task を実現した[37]。本研究で開発したリアルタイムオペレーティングシステムは、マルチプロセッサスケジューリング[11,35]をはじめ、計算精度を向上させるインプリサイス計算モデルに基づくリアルタイムスケジューリング[3,6,7,8,12,16,18,20,34,38,40,41,42,43]や、低消費電力量を実現する電圧周波数制御に基づく省電力スケジューリング[5,13]をサポートする。また、μITRON 仕様をサポートするリアルタイムオペレーティングシステムを開発したことにより、アプリケーションの開発効率を向上させるだけでなく、本研究の普及を促進することが可能になった[9,31]。さらには、インプリサイス計算モデルと省電力機構のトレードオフを調査し、単位消費電力量当たりの品質を最大化する手法を明らかにした[33,39]。Responsive Link のリアルタイム通信と省電力機構のトレードオフを調査し[36]、Responsive Link 固有機能をアプリケーション開発者が容易に利用するためのライブラリをリアルタイムオペレーティングシステムに実装している[22,25]。

# <科学技術イノベーションに大きく寄与する成果>

#### 1. D-RMTP I SoC/SiP の設計・実装・検証・評価

ヒューマノイド[42,43,46,47]の分散制御を実現する SoC である D-RMTP I を設計・実装・評 価した。D-RMTP I には、前述のリアルタイム処理機能及びリアルタイム通信機能、さらにはロ ボットの分散制御に必要な全ての I/O を集積した初の SoC である(図 1 参照)[26]。そして、 D-RMTP I SoC、DRAM、Flash memory、電圧センサ、温度センサ、及び DVFS のための電源 モジュール等を30mm 角及び20mm 角のサイズに集積した画期的なSiPを実現した。コアに供 給する電圧と周波数を動的に制御することにより消費電力量を 1/5 以下に削減可能であること を実証した[24,30]。 D-RMTP I SiP 上の AD コンバータによりコア及び DRAM に供給される電 源電圧をソフトウェアからモニタリングできるため、RT-DVFS の際に電圧が指定した値に確実 に遷移してから周波数制御を行うことができる。これによってプログラムの安定的な動作を保証 してディペンダビリティを向上させ、かつ、リアルタイム性を維持しながら消費電力を削減できる。 また、ロボットの体内等の非常にノイズが大きい場所においても信頼性が高く時間粒度の細か いリアルタイム通信を実現することができる。分散リアルタイムシステムを構築するために必要な ほぼ全ての機能を SoC/SiP として超小型かつディペンダブルに実現し、産業的なインパクトも 大きい。 同様に、プロセッシングコア(RMT PU)と DRAM の温度をソフトウェアからリアルタイムに 監視できるため、デバイスの動作環境(温度等)に応じて電圧及び動作周波数をディペンダブ ルに調節することができる。本研究ではデバイスの電圧と温度をリアルタイムに観測しつつ RT-DVFS を行うスケジューリングアルゴリズム及び機構を研究開発しており、このようなアプロ ーチはロボットや宇宙機等過酷な条件で動作する組込みアプリケーションにおいてディペンダ ビリティを実現するために重要である。 D-RMTP は周辺 I/O 機能を有した単なる 1 チップマイコ ンではなく、プロセッシングコアや通信機構にディペンダブルなリアルタイム処理・通信機能を 有しており、このような SoC は他に存在しない。

# 2. 異種の VLSI の多段実装技術

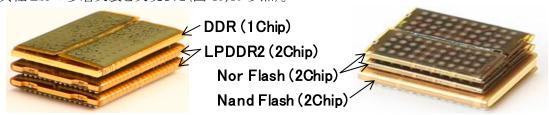

従来技術では不可能であった異種の VLSI の多段実装技術を研究開発した[44]。 VLSI を 3

次元実装するパッケージング技術である FFCSP (Flexible carrier Folded real Chip Size Package)を応用することでメモリモジュールを高信頼性を維持しつつ大幅に小型化し、30mm 角 *D-RMTP I* SiP、20mm 角 *D-RMTP II* SiP、1/O Core SiP を実現した。 具体的には、DRAM と Flash memory の 3 段及び 4 段実装を実現する SiP 技術を研究開発した。DRAM モジュールに関しては、DDR SDRAM および LPDDR2 SDRAM を 3 段積層することができた。その際、詳細にシミュレーションを行い、下段には高速な VLSI (LPDDR2)を配置し、上段には比較的低速な VLSI (DDR SDRAM)を実装することで、信頼性の向上を実現した。 Flash memory モジュールに関しては、Nor flash と Nand flash という異種の Flash memory を多段実装することで、両方の機能を持つ Flash メモリモジュールを実現した。この技術により Flash モジュールのサイズを大幅に小型化することで 20mm 角 *D-RMTP* SiP を実現でき、SiP をヒューマノイドロボット体内に実装できるようになった。

#### 3. 大出力発揮可能な高効率モータ駆動制御モジュール(2軸対応)

ダイナミックレンジの大きな高効率なモータ電流制御回路及びモータ内部温度推定機能に基づく大出力発揮可能な高効率モータ駆動モジュール(2軸対応)の開発を行った[46,47,48]。また、開発した高効率モータ駆動モジュールを用いた大出力脚の設計・実装・評価を行った。本技術により、全身 20 自由度程度を想定した等身大ヒューマノイドに十分搭載可能な駆動基板サイズでありながら、従来技術での駆動系よりも飛躍的にモータ駆動出力が高まり、人間と同程度の関節速度及びトルクを発揮可能なヒューマノイドが構築可能となり、介護現場を始めとする将来的なヒューマノイドの社会進出を現実的なものとして推進する基礎技術として期待できる。従来技術では、発揮可能な関節トルクあるいは関節速度のいずれかを犠牲にしており、本技術による駆動基板のように関節トルク及び速度双方を両立するものは提案されていない。一方で実際の介護現場においては、人を支えることのできる十分な関節トルクや、咄嗟に人を支えられるだけの瞬間的な関節速度が不可欠であり、本技術が非常に優位であると考える。

# § 2. 研究構想

#### (1) 当初の研究構想、課題設定

# ①本研究の背景、社会や産業に存在する問題と本研究の課題設定

本研究がターゲットとしている組込みリアルタイムシステムは、産業的にも技術的にも、今後の 日本にとって非常に重要な位置を占め続けると考えられる。従来、組込みリアルタイムシステム に関する研究はソフトウェアに関するものがほとんどであったが、ディペンダブルで超小型・高機 能・低消費電力な組込みリアルタイムシステムを構築するためには、ターゲットアプリケーション、 ハードウェア、ソフトウェアをコデザインし、トータルシステムとして研究開発するのが望ましい。 一方、VLSI (SoC)は基板に実装してはじめて動作するので VLSI システムに対するディペンダビ リティは基板実装技術と共に考慮する必要がある。 近年、VLSI システムに対するする高信頼性 や省電力など多くの要求に対して SoC を補間する手段として、SiP の研究が盛んに行われてい る。VLSI システムのディペンダビリティは、チップ、パッケージ、基板を互いに考慮しながら設計 することによって、はじめて大幅に向上させることが可能であると考えられる。本研究においては、 組込みリアルタイムシステム(特にロボットの分散制御システム)の構築をターゲットとして、ディ ペンダブルな SoC 及び SiP の設計・実装・評価に関する基盤技術を確立する。その際、本研究 の成果としてできあがる SoC と SiP からなる VLSI システム及び基本ソフトウェアを用いて、各種 組込みリアルタイムシステム(特にロボット)への組込み応用を目指す。これらの実現のために、 ターゲットアプリケーション、ハードウェア、ソフトウェアをコデザインし、トータルシステムとして研 究開発する手法を構築する。

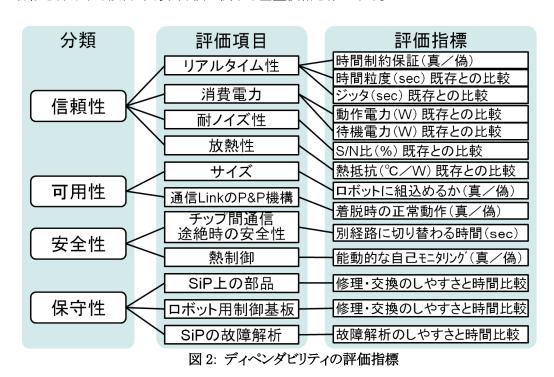

本研究で取り扱うディペンダビリティを図 2 の様に定義する。この評価指標に沿ってディペンダビリティの向上を目指すための研究を行い、さらには研究開発の成果の評価を行う。実用的

な組込みリアルタイムシステムを構築するために、アプリケーション(ロボットへの応用)とソフトウェア(OS)及びハードウェア(アーキテクチャ)のコデザイン、SoC と SiP のコデザイン、及びそれらの設計・実装・評価手法の研究を行う。その実現のためにソフトウェアで行うべき処理とハードウェアで行うべき処理の切り分けを行いつつ、リアルタイム性を有したプロセッサアーキテクチャ、オンチップネットワーク、チップ間通信リンク、動的電圧周波数制御等の研究開発を行う。並行して SoC と SiP とをコデザインし、SoC/SiP に高信頼性化、小型化、高機能化、低消費電力化等の特徴を付与する設計・実装・評価に関する基盤技術を確立する。

#### ②本研究チームの達成目標。

本研究の目的は、組込みリアルタイムシステム(特に分散制御システム)の構築をターゲットとして、ディペンダブルな SoC 及び SiP の設計・実装・評価に関する基盤技術を確立することにある。その際、本研究の成果としてできあがる SoC と SiP からなる VLSIシステム及び基本ソフトウェアを用いて、各種組込みリアルタイムシステム(ロボット等)への組み込み応用を目指し、ディペンダブルで超小型・多機能・低消費電力な VLSIシステムを SoC と SiP をコデザインすることによって実現すること、及びそのための設計・実装・評価手法を確立することを目標とする。

個別の目標としては、第 1 にターゲットアプリケーション(ロボット等の制御)を実現するために基本ソフトウェア (OS) 及びハードウェア(プロセッサ及び NoC (Network-on-Chip)等のアーキテクチャ)のコデザインを行い、基本ソフトウェアで行うべき処理とハードウェアで行うべき処理の切り分けを行って、組込みリアルタイム処理を高効率で実現することにある。そのために、QoS (Quality of Service)の理論と共に、プロセッサアーキテクチャ、NoC、チップ間通信アーキテクチャ、電圧周波数制御等の要素技術の研究開発を行い、それらをまとめて SoC として設計・実装する。従来、リアルタイム性の時間粒度は 1msec 程度であったが、本研究によって時間粒度  $10 \mu$  sec 程度のリアルタイム性を実現し、アプリケーションとしては非常に高精度な分散制御システム(ロボットシステム)を構築する。

第2の個別の目標は、ディペンダブルで超小型・高機能・低消費電力な SoC/SiP を実現するための基盤技術を、SoC と SiP をコデザインすることによって確立することにある。

現在の高機能な組込みシステムは、リッチな開発実行環境(Linux 等の組込み OS 等)を 要求し、それらは大容量メモリ(DRAM)やフラッシュメモリを要求する。さらに、SoCには 様々な規格の I/O (Ethernet, USB, IEEE1394 等)を集積することが要求されている。SoC にはそれら必要な機能(MPU, Bus, Memory IF, I/0 等)をほぼすべて集積可能であるが、 DRAM、フラッシュメモリ、及び各種 I/O のドライバ(Phy) をすべて同時に SoC に集積す ることはプロセス的に困難であるとともに、歩留まり低下や欠陥を内包するリスクを伴 うことにもなる。一方で、ターゲットの組込みリアルタイムシステム (ロボット等) は、 狭く形状が特殊な筐体内に多種多数のセンサ/アクチュエータを搭載し、それらセンサ /アクチュエータ毎にコントローラが必要となるため、 非常に狭いスペースに VLSI シス テムを構築することが求められる。これらの要求を満たしつつ実用的でディペンダブル な VLSI システムを構築するためには、SoC 技術と SiP 技術を相乗的に組み合わせる(各々 の弱点をカバーしつつ特長を引き出す)必要がある。その際、ディペンダビリティの向 上を目指し、SiP 化する際には SoC を含む全てのデバイスを KGD (Known Good Die)とし て実装し、さらには制御兼自己モニタリング用センサ(電圧センサや温度センサ等)を SiP に内蔵し、VLSI システムをより安定化させる。最終的には SoC と DRAM 等の周辺デバ イスを高密度実装技術 (TSV (Through Silicon Via)、コアレス基板等) の技術を応用し て多ピン接続して複数積層し、同時に高効率な放熱構造を実現することで、ディペンダ ブルでスケーラブルな超小型の VLSI システムを実現するための基盤技術を構築する。

第3の個別としては、組込みアプリケーション(ロボットへの応用)を用いたディペンダビリティ(主に信頼性、可用性、安全性、保守性)の実証評価を行うと共に、その評価結果を次バージョンへフィードバック(同様な研究開発ループを研究期間内に繰返し)することによって、最終的には要求仕様(時間粒度の非常に細かいリアルタイム性、低消費電力、超小型化等)を満たしつつ非常に高いディペンダビリティを実現することを目指す。研究開発した SoC/SiP を組み込んだロボットシステムと、従来採用していた既存の商用マイコンを組み込んだロボットシステムとを比較して、実際にロボットを動作させた際の駆動ノイズ、温度上昇、実時間制御性、衝撃によるロボットリンク損傷、電装系損傷、センサ系の経年変化・故障といった様々なケースのロボットの実挙動が安全性の観点から十分改善されていることを実証する。

## ③本研究の特徴

国内外において、組込みシステムやリアルタイム処理・通信に関する研究はほとんどソフトウェア中心に行われている。それに対して本研究では、理論(アルゴリズム)及びソフトウェア(OS、スケジューラ)の研究とハードウェア(アーキテクチャ)の研究とを同時に協力しつつ行い、最適な役割分担を決定しつつ互いに研究を行うことにより、ソフトウェア/ハードウェア単独では実現できない演算や通信の QoS 制御を実現可能とする。また、従来のマルチコアやオンチップネットワークに関する研究は、サーバ向けの同一のコアを効率よく接続するための研究がほとんどであったが、本研究は組込みシステムをターゲットとしており、大きさや機能及び速度の異なるプロセッサ、メモリ、及び各種 IO を接続可能にし、さらには各機能に QoS を持たせる点に大きな独創性がある。

同様に、SoC と SiP のコデザインに関する研究は、要素技術が黎明期だということもあり、これまではほとんど行われてこなかった。FFCSP 以外の 3 次元 SiP 技術には、PoP (Package on Package)、部品内蔵基板、TSV (Through Silicon Via)などがあるが[45]、何れも積層したチップの放熱が困難であるうえ、歩留まりや伝送速度に問題がある。本研究では、ディペンダブルなVLSI システムを構築するために、上記のような 3 次元 SiP 技術の問題点を FFCSP を用いて解決する。FFCSP は、センサやパッシブデバイスなど多種類のデバイスも内蔵可能という他の同様な技術にはない特徴を有した自由度が高い 3 次元 SiP 実装技術であり、さらには SoC 設計とコデザインしてディペンダビリティの向上を行う点に大きな独創性を有する。また、異種の VLSI の多段実装はいくつも提案されているが、本研究に様に簡単な製造装置で実現している方法は存在しない。

実アプリケーションとして、過酷な条件である大出力ロボット環境下で D-RMTP SoC/SiP の

検証を行い有効性を実証していき、既存の研究用ロボットプラットフォームだけではなく、工業用ロボットアームや宇宙用ロボットも含めたロボット環境下でも応用可能であることを示していくことが可能となる。具体的には、これら大出力脚プラットフォームを軸として、必要な評価基板設計・開発、単軸での評価、ロボット体外での同等規模システム構成での評価、実ロボット組込み評価を段階的に行っていくことで、着実に実証評価を行う。

以上の基盤技術が実現されると、技術的にも産業的にも非常に大きなインパクトを与えられると考えられる。

#### ④研究実施方法

1) 本研究チーム運営の方針、研究グループ間の分担・協力関係

本研究では、基盤ソフトウェア(ディペンダブルオペレーティングシステム:担当 慶應義塾大学)、基盤ハードウェア(ディペンダブルアーキテクチャ及びディペンダブル SoC:担当 慶應義塾大学)、基盤パッケージ(ディペンダブル SiP:担当 NEC アクセステクニカ)、及び組込みアプリケーション(先端ロボット応用によるディペンダビリティ評価:担当 東京大学)の大きく4つにテーマ(グループ)を分けつつも、相互に密接な連携を保ちつつ、コデザインを行いながら研究開発を行う。

基盤ハードウェアグループがリアルタイム処理用 SoC の開発を行い、基盤パッケージグループが SiP 化及びボード設計を行う。基盤ソフトウェアグループがソフトウェアの開発環境及び RT-OS を研究開発し、組込みアプリケーショングループが D-RMTP SoC/SiP 及び RT-OS の実機検証及びそれらの検証結果のフィードバックを行う。

# 2) 領域外部の企業等との連携

組込みアプリケーションに関しては、共同研究グループとしては入ってもらわないが外部アドバイザー(JAXA 宇宙研 高橋忠幸教授及び坂井真一郎准教授)を依頼し、アドバイザーからの助言を元にして宇宙機への応用も目指す。

ET 展示会(組込み総合技術展)において、普及の一環として評価キットを配布しているが、数 社から実用化に向けた検証作業を行っているとの報告を受けており、協力企業との連携体制を 今後も維持していく。

- 3) 領域内他研究チームとの連携関係特に無し。

- (2)新たに追加・修正など変更した研究構想、発展テーマ

- ① 中間評価で受けた指摘や助言、それを踏まえて対応した結果について

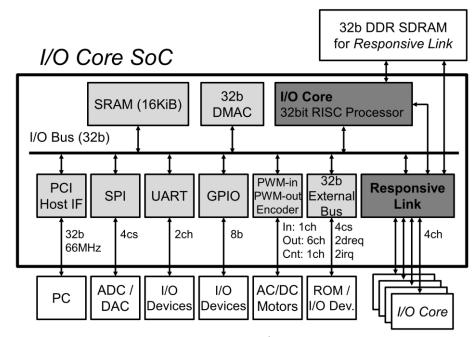

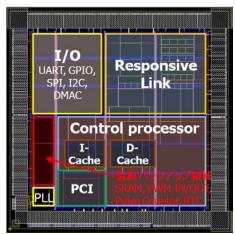

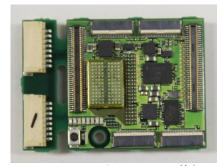

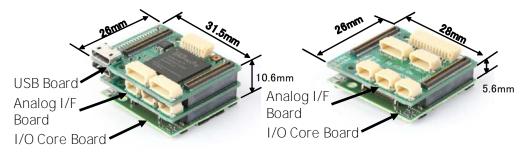

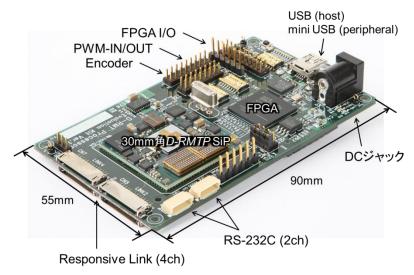

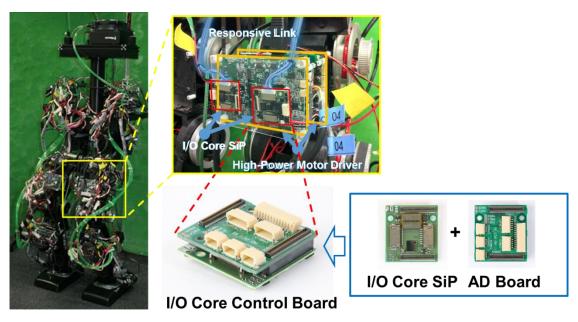

研究成果を広めるために、30mm 角 D-RMTP I SiP 搭載評価キット(図 41 参照)の研究開発を行い、普及を図る努力をした。更に Responsive Linkの普及を図るために、D-RMTPの命令セットと互換性のある廉価版 CPU を搭載した I/O Core SoC (図 3,4,5 参照) 及び I/O Core SiP (図 6 参照)を研究開発した。I/O Core SiP には、様々な機能を拡張基板を挿せば拡張できるように外部バスを共通化した BtoB コネクタを設計実装した。BtoB 基板に拡張基板を挿すことで様々な構成となりるように、拡張基盤としてはアナログ制御基板 (図 7 参照)、USB 基板 (図 8 参照)、DRAM 基板 (図 9 参照)等を設計実装した。ロボット制御に使用する際には、I/O Core SiP にアナログ制御基板を挿し、開発時にはさらに USB 基板をスタックする構成となる (図 10 参照)。ここで、アナログ制御基板には、AD コンバータ、加速度センサ、温度センサ等を搭載している。USB 基板には、USB インタフェース (Host 及び Device の両方)を搭載しており、この基板を接続することで USB インタフェースを持つ様々なデバイスとの通信が可能となる。DRAM 基板はメモリ空間の拡張を図ることができると同時に、基板上の FPGA に Responsive Link を搭載できるよう設計している。このように Responsive Link を書き換え可能な FPGA に搭載できるようにすることで、Responsive Link の更なる普及を図ることができる。ハードウェアの小型化と信頼性の向上を実現すると共に、これらの基板を用いて普及を促進させる。

さらに、これら研究開発した I/O Core SiP を実際に大出力脚ロボットへと実装することで、従来 RS-485で行っていた体内通信を容易に Responsive Link に置き換えることができることを示した。 また、制御基板のサイズを小型化しているため物理的にも実装が容易であり、筋骨格ロボットのように狭小スペースに多数のノードが配置されていても問題なく組込み評価を行えることを示した。

図 3: I/O Core ブロック図

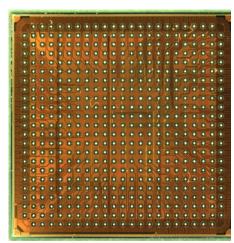

図 4: I/O Core SoC レイアウト

図 5: I/O Core SoC チップ写真

図6: I/O Core SiP

図 7: アナログ制御基板

図 8: USB 基板

図 9: DRAM 基板 (左: 表面 右: 裏面)

I/O Core SiP (for Development Environment)

I/O Core SiP (for Embedded in Robots)

# 図 10: I/O Core 基板(左:プログラム開発用、右:ロボット制御用)

② 中間報告書§ 6. 今後の研究の進め方、および研究成果の見通しの記載事項に関し、研究を進めた結果について

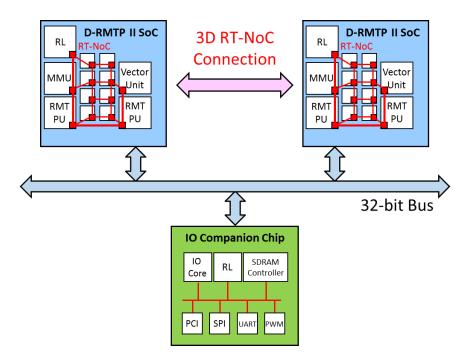

基盤ハードウェアグループと基板パッケージグループとでコデザインし、超薄型コアレス基板の表裏に D-RMTP II SoC を Face to Face で実装しチップ間の RT-NoC を最短で配線することで、低コスト・低消費電力で広帯域かつディペンダブルなチップ間通信を実現した。 DRAM はアプリケーションの要求に応じて、高パフォーマンスを優先する場合は GDDR3 を、低消費電力を優先する場合は LPDDR2 を選択できるように FFCSP を用いて 3 次元積層し、かつピン互換にして SiP に実装できるようにした。さらに、D-RMTP II SoC を Face to Face で接続する際に、チップ間 RT-NoC の帯域を広げてディペンダビリティを高めるために、チップ間垂直リンクの接続にコアレス基板を用いることで、広帯域幅のチップ間接続を低コストで実現した[41]。 DRAM 実装に関しては、異種 DRAM の多段実装と異種 DDR の交換搭載をFFCSP を用いて可能とした。

③ 上記①②以外で生まれた新たな展開について

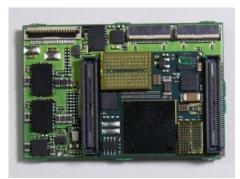

20mm 角 D-RMTP ISiP を搭載し、I/0 Core SiP 用の拡張基板と BtoB コネクタ経由で接続可能にした 20mm 角 D-RMTP I汎用制御基板を研究開発した(図 11 参照)。この基板上の FPGA には前述した DRAM 基板と同様に Responsive Link を搭載可能なように設計しており、本基板及び DRAM 基板を搭載した基板との間で Responsive Link による通信を行うことができるように設計・実装した。この基板の研究開発により、D-RTMP I においても I/0 Core と同様にハードウェアの小型化と信頼性を向上させると共に、研究成果の普及を促進させることが可能となった。

図 11: 20mm 角 D-RMTP I 汎用制御基板 (左: 裏面 右: 表面)

# §3 研究実施体制

(1)研究チームの体制について

① 「慶大(基盤ソフトウェア、基盤ハードウェア)」グループ 研究参加者

|         | 氏名     | 所属          | 役職      | 参加時期         |  |

|---------|--------|-------------|---------|--------------|--|

| $\circ$ | 山﨑 信行  | 慶應義塾大学大学院•理 | 教授      | H21.10~H27.3 |  |

|         |        | 工学研究科       |         |              |  |

|         | 松谷 宏紀  | 同上          | 専任講師    | H23.4~H25.3  |  |

|         | 加藤 真平  | 同上          | 博士訪問研究員 | H21.10~H24.3 |  |

| *       | 水頭 一壽  | 同上          | 特任助教    | H21.10~H26.3 |  |

| *       | 千代 浩之  | 同上          | 助教      | H21.10~H27.3 |  |

| *       | 村田 祐介  | 同上          | M2      | H21.10~H23.3 |  |

| *       | 向後 卓磨  | 同上          | M2      | H21.10~H23.3 |  |

| *       | 梅尾 寛之  | 同上          | M2      | H21.10~H23.3 |  |

| *       | 池田 雄児  | 同上          | M2      | H21.10~H23.3 |  |

| *       | 石川 洋輔  | 同上          | M2      | H21.10~H23.3 |  |

| *       | 新井 寛   | 同上          | M1      | H21.10~H22.3 |  |

| *       | 稲垣 文二  | 同上          | M2      | H22.4~H23.9  |  |

| *       | 笹川 雄二郎 | 同上          | M2      | H22.4~H24.3  |  |

| *       | 藤井 啓   | 同上          | M2      | H22.4~H24.3  |  |

| *       | 谷口 将一  | 同上          | M2      | H23.4~H25.3  |  |

| *       | 利長 勇児  | 同上          | M2      | H23.4~H25.3  |  |

| *       | 冨澤 裕貴  | 同上          | M2      | H23.4~H25.3  |  |

| *       | 松本 康平  | 同上          | M1      | H23.4~H24.3  |  |

| *       | 吉住 修   | 同上          | M1      | H23.4~H25.3  |  |

| * | 金田 健佑 | 同上 | D1 | H24.4~H27.3 |

|---|-------|----|----|-------------|

| * | 川口 雄輝 | 同上 | M2 | H24.4~H27.3 |

| * | 川瀬 大樹 | 同上 | M2 | H24.4~H27.3 |

| * | 山崎 大輝 | 同上 | M2 | H24.4~H26.3 |

| * | 上田 陸平 | 同上 | M2 | H24.4~H26.3 |

| * | 伊藤 康人 | 同上 | M2 | H24.4~H26.3 |

| * | 石田 匠  | 同上 | M2 | H25.4~H27.3 |

| * | 久村 雄輔 | 同上 | M2 | H25.4~H27.3 |

| * | 溝谷 圭悟 | 同上 | M2 | H25.4~H27.3 |

| * | 高須 雅義 | 同上 | M2 | H25.4~H27.3 |

| * | 室伏 良平 | 同上 | M1 | H25.4~H26.3 |

| * | 高橋 昌裕 | 同上 | M1 | H25.4~H27.3 |

| * | 萩原 秀磨 | 同上 | M1 | H26.4~H27.3 |

| * | 羽鳥 雄介 | 同上 | M1 | H26.4~H27.3 |

|   | 村田 太郎 | 同上 | В4 | H27.3~H27.3 |

|   | 松井 司  | 同上 | B4 | H27.3~H27.3 |

|   | 山田 賢治 | 同上 | В4 | H27.3~H27.3 |

# 研究項目

- ・ ディペンダブル SoC 及び SiP の設計

- ・ ディペンダブル OS の設計及び実装

- リアルタイムスケジューリング理論の確立

- リアルタイム通信によるディペンダビリティの確立

- ・ 低消費電力、時間精度などの QoS を制御

# ②「基盤パッケージグループ」グループ

# 研究参加者

|   | 氏名     | 所属                                       | 役職        | 参加時期         |

|---|--------|------------------------------------------|-----------|--------------|

| 0 | 和田 喜久男 | NEC プラットフォームズ<br>(株) AD(事) 第一組込み<br>グループ | シニアエキスパート | H21.10~H27.3 |

|   | 齋藤 昌彦  | NEC アクセステクニカ(株)<br>開発本部                  | リーダー      | H21.10~H26.3 |

|   | 増田 靜昭  | NEC アクセステクニカ(株)<br>商品開発部                 | 主任        | H21.10~H26.3 |

|   | 大須 良二  | NEC アクセステクニカ(株)<br>パッケーシ゛製造部             | グループリーダー  | H21.10~H24.3 |

|   | 鈴木 克彦  | NEC アクセステクニカ(株)<br>生産効率推進部               | 主任        | H24.4~H26.4  |

|   | 金井 政史  | NEC アクセステクニカ(株)<br>PWB 設計部               | 主任        | H21.10~H22.3 |

|   | 松田 敬毅  | NEC アクセステクニカ(株)<br>商品開発部                 | 担当        | H21.10~H22.3 |

# 研究項目

・基盤パッケージグループは、組込アプリケーショングループからの要求を基に基盤ハードウェアグループとコデザインしつつ FFCSP を応用することで、ディペンダブルな超小型基盤パッケージ(SiP)の研究開発、及びその設計・組立・評価手法を確立する。

# ③「東大(組込みアプリケーション)」グループ研究参加者

| 研究 参加者 一种 |        |               |       |              |  |

|-----------------------------------------------|--------|---------------|-------|--------------|--|

|                                               | 氏名     | 所属            | 役職    | 参加時期         |  |

| $\circ$                                       | 稲葉 雅幸  | 東京大学情報理工学系研究科 | 教授    | H21.10~H27.3 |  |

|                                               | 岡田 慧   | 同上            | 准教授   | H21.10~H27.3 |  |

|                                               | 垣内 洋平  | 同上            | 特任講師  | H24.4~H27.3  |  |

|                                               | 菅井 文仁  | 同上            | 特任助教  | H26.4~H27.3  |  |

|                                               | 中西 雄飛  | 同上            | 特任研究員 | H21.10~H26.3 |  |

|                                               | 浦田 順一  | 同上            | 特任研究員 | H21.10~H26.3 |  |

| *                                             | 白井 拓磨  | 同上            | D3    | H24.4~H27.3  |  |

| *                                             | 上月 豊隆  | 同上            | D2    | H23.4~H27.3  |  |

| *                                             | 浅野 悠紀  | 同上            | D2    | H23.4~H27.3  |  |

| *                                             | 伊藤 佳人  | 同上            | D1    | H23.4~H26.3  |  |

| *                                             | 梯 百合子  | 同上            | D1    | H23.4~H26.3  |  |

| *                                             | 溝口 弘悟  | 同上            | M2    | H23.4~H25.3  |  |

| *                                             | 黒飛 朋子  | 同上            | M2    | H23.4~H25.3  |  |

| *                                             | 中岡 卓也  | 同上            | M2    | H24.4~H26.3  |  |

| *                                             | 笹渕 一宏  | 同上            | M2    | H25.4~H27.3  |  |

| *                                             | 小島 邦生  | 同上            | M2    | H25.4~H27.3  |  |

| *                                             | 中島 慎介  | 同上            | M2    | H26.4~H27.3  |  |

| *                                             | 木村 航平  | 同上            | M2    | H26.4~H27.3  |  |

| *                                             | 茂木 陽太郎 | 同上            | M1    | H24.4~H25.3  |  |

| *                                             | 室岡 雅樹  | 同上            | M1    | H25.4~H26.3  |  |

| *                                             | 野田 晋太朗 | 同上            | M1    | H25.4~H26.3  |  |

| *                                             | 大久保 壮一 | 同上            | M1    | H26.4~H27.3  |  |

| *                                             | 柚木崎 創  | 同上            | M1    | H26.4~H27.3  |  |

| *                                             | 黒岩 英則  | 同上            | M1    | H26.4~H27.3  |  |

# 研究項目

- ・大出力系でのディペンダビリティ評価基板基礎モジュール単体での制御実験評価

- ・大出力系での 30mm 角 D-RMTP 搭載基板ネットワークによる通信系の実験評価

- ・大出力脚を用いた高速制御に基づく転倒回避アルゴリズムによるリアルタイム制御の検証評価

- ・小型分散系での高密度実装モータ駆動基板を用いた制御実験評価

- ・小型分散系での 20mm 角 D-RMTP 搭載モータ制御基板の設計開発

- (2)国内外の研究者や産業界等との連携によるネットワーク形成の状況について リアルタイム処理に関しては、名古屋大学加藤真平准教授とOSに関して連携している。 ロボット制御に関しては、産業技術総合研究所DHRCと連携している。

# §4 研究実施内容及び成果

- 4.1 「リアルタイム処理機構」(慶大 基盤ハードウェアグループ)

- (1)研究実施内容及び成果

- ① 実施方法・実施内容

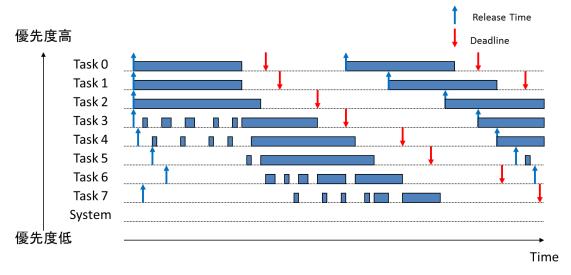

10 μ sec オーダのリアルタイム性を実現するために、マイクロプロセッサ(RMT PU)にリアルタイム実行機構を設計・実装した。具体的には、ハードウェアによるリアルタイムタスク(スレッド)のスケジューリング及び実行を可能にする RMT 実行(優先度付き SMT 実行)(図 12 参照)、リアルタイムスレッドの実行速度を一定にする IPC 制御機構(図 13,14 参照)[4,14]、コンテキストスイッチのオーバヘッドを削減するコンテキストキャッシュ、割り込みによるスレッド起床機能を実装した。

# ② 創造性

本研究では、従来はソフトウェアで行っていたコンテキストスイッチを行うことなく、ハードウェア (プロセッサ) で優先度付のスレッドを同時実行することで、リアルタイム実行を実現した (RMT 実行と呼称する)。また、同時実行する各スレッドの実行速度である IPC を一定に制御する IPC 制御機構を実現し、プログラムの実行予測性を大幅に向上した。さらに、コンテキストキャッシュを使うことでコンテキストスイッチのオーバヘッドを大幅に削減した。割り込み (特にタイマー割り込み)によるスレッド起床機能により、割り込み発生後、1 クロックで対応するスレッドを起床することを可能とし、大幅に割り込み処理のオーバヘッドを削減するとともに、スレッドの正確な時間同期を可能にした。これらの機能を融合することで、従来は不可能であった  $10 \mu \sec$  オーダのリアルタイム処理を実現した[26,37]。

#### ③ 有用性

従来、リアルタイム処理は主にソフトウェアのみで実現されており、伝統的なソフトウェアによるリアルタイム処理では、1 msec オーダ程度のリアルタイム性しか実現することができなかった。本研究開発により、 $10 \mu sec$  オーダのリアルタイム処理が可能となり、非常に高精度で信頼性が高く時間粒度の細かいリアルタイム処理を実現することができるようになり、産業的なインパクトも大きい。例えば、本技術をロボット制御に応用すると、制御帯域の大きな制御を実現することができ、従来は実現困難であった非常に高速に動作するロボットや高周波数の振動を制御するようなことが実現可能となる。

#### ④ 優先比較

現在、単なる SMT は Intel CPU (Core i7 等)の Hyper Threading をはじめとして、多くの CPU で用いられている。これらの通常の CPU では、スレッド間の並列性を抽出し CPU のスループット を向上する手段として SMT を用いているが、本研究はアプローチが根本的に異なる。本技術で は、ハードウェアコンテキストを OS のタスクキューとみなし、コンテキスト(スレッド)にリアルタイム 処理の優先度をつけてSMT 実行させることにより、優先度順にタスクを並列実行しながら(つまり 通常は OS がソフトウェアで行う優先度実行をハードウェア(CPU)で行いながら)、リアルタイム実 行を行いつつ従来の SMT 同様にスループットも向上させる(図 12 参照)。 しかしながら、この方 式では、高スループットで優先度順にスレッドを並列実行できるが、同時に実行するスレッドの組 み合わせ等によってはスレッドの実行速度が変化してしまう可能性がある(図 13 参照)。そこで、 各スレッドの速度(IPC)を一定にする IPC 制御を研究開発した。この IPC 制御機構を組み合わせ ることにより、正確なリアルタイム処理を実現可能にした(図 14 参照)。 ここで、*RMT PU*のハード ウェアコンテキスト数は8なので、スレッド(プログラム)の数が9以上になると、ソフトウェアが介在 する必要があり、本機構が有効に働かなくなってしまう。そこで、コンテキススイッチをハードウェ アで行うコンテキストキャッシュを研究開発した。このコンテキストキャッシュは、ソフトウェアで制 御され(CPU の命令で制御され)、4 クロックでコンテキストスイッチを行うことができる。 さらに、割り 込み(特にタイマー割り込み)により、対応するスレッドが 1 クロックで起床するメカニズムを設計 実装した。これらの技術を組み合わせることにより、 $10 \mu \sec x$  オーダのリアルタイム処理を実現した。

図 12: 優先度付き SMT 実行 (RMT 実行)

図 13: マルチスレッド実行(IPC 制御なし) 図 14: マルチスレッド実行(IPC 制御あり)

# 4.2 「リアルタイム通信機構」(慶大 基盤ハードウェアグループ)

# ① 実施方法・実施内容

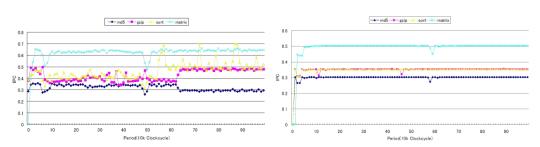

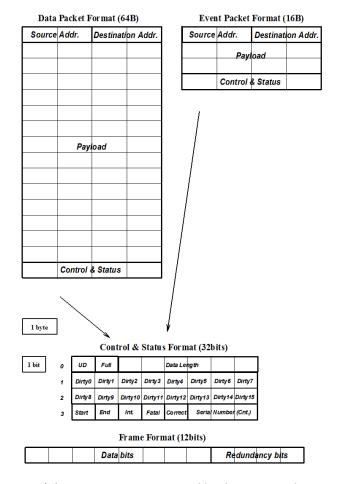

$100\,\mu$  sec オーダのリアルタイム性をディペンダブルに実現するために、リアルタイム通信機構を設計・実装した。ISO/IEC 24740 として標準化された Responsive Link [16]をベースに、ロボット内の高ノイズ環境においてもディペンダブルに  $100\,\mu$  sec オーダのリアルタイム通信が可能なようにリアルタイム通信機構を設計・実装した。具体的には、リアルタイム通信を実現するために通信におけるプリエンプションを、優先度を用いたパケット追い越しによって実現した。さらには、複数種類のラインコード及びエラー訂正強度と符号化率の異なるエラー訂正コードを設計・実装し、ノイズレベルによって動的にそれらのラインコードとエラー訂正コードの組み合わせを選択できるようにした。そのために、新規にエラー訂正機能付のラインコード 4b10b を研究開発した。

#### ② 創造性

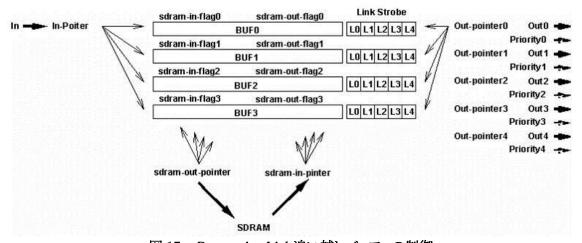

本研究では、研究代表者が研究開発し ISO/IEC 24740 として標準化されたリアルタイム通信 規格 Responsive Link をベースに研究開発を行っている。Responsive Link は、ハードリアルタイム通信 (イベントリンク)とソフトウェアリアルタイム通信 (データリンク)の物理的な分離 (図 15 参照)、通信におけるプリエンプション、優先度を用いたパケット追い越し(図 16,17 参照)を実現する[17,22,25,27,29]。さらに、複数種類のラインコード及びエラー訂正コード (図 18,19 参照))を動的に組み合わせることを可能にしている。この際、ディペンダビリティを向上するために、ラインコード自体にエラー訂正能力を持たせた 4b10b というラインコードを新規に設計し、ラインコードに

#### ③ 有用性

従来、リアルタイム通信は USB や IEEE1394 のようにアイソクロナス転送を用いたソフトリアルタイム通信のみが実現されていた。これらの通信は主に PC 向けのものであり、接続ノード数が限られ(USB: 127, 1394: 63)、またバス型であるためノード数が増えると単位ノードあたりの帯域が低下し、さらにはアイソクロナス転送ではエラー訂正をサポートしておらず、分散制御用途には不向きであった。 CAN は優先度をサポートしているが、エラー訂正をサポートしておらず、バス型で通信速度は 1Mbps 程度であるので、現在の分散制御システムを構築することは困難である。一方、Responsive Link は、エラー訂正強度と通信速度のトレードオフを制御することができ、通信速度も高速(片方向 800Mbaud)である。また、バス型ではなく1対1通信をスイッチングを行いながらバーチャルカットスルーし、パケットに付与された優先度を元にノード毎にパケットの追い越しをすることで通信のプリエンプションを実現するので、リアルタイムアルゴリズムを通信に応用することが可能となる。その結果、大規模な分散リアルタイムシステム(特に分散制御システム)をトップダウンに構築することができる。さらには、環境から受けるノイズに応じてエラー訂正強度を動的に変更することができる、スループット、エラー訂正強度、消費電力のトレードオフを制御することで、多種多様なアプリケーションに対応することができる。

#### ④ 優位比較

リアルタイムアルゴリズムを通信に応用するためには、通信においてもプリエンプションを実現する必要がある。Responsive Linkでは、パケットに優先度を付けノード毎にパケットの追い越しを行うことで通信のプリエンプションを実現しているが、通信のプリエンプションを実現している通信規格は他には存在しない。また、環境に応じてエラー訂正の強度と通信速度のトレードオフを制御できるようになっているが、そのような通信規格も存在しない。今回、ディペンダビリティを向上するために、ラインコード自体にエラー訂正能力を持たせた 4b10b というラインコードを新規に設計し、ラインコードにエラー訂正を入れ込むことを初めて実現した。通信規格は標準化しないと意味がないので、現在、情報処理学会試行標準として 4b10b を標準化作業中である。試行標準として標準化された後、ISO/IEC において標準作業を行う予定である。これらの技術を組み合わせることにより、100 μ sec オーダのディペンダブルなリアルタイム通信を実現した。リアルタイム性と耐ノイズ性を共に有した通信規格は他に存在せず、国際標準化も行われているので、技術的にも産業的にも機器間のリアルタイム通信としては非常に大きなインパクトがある。

図 15: Responsive Link インタフェース

図 16: Responsive Link 追い越し機能付きネットワークスイッチ

図 17: Responsive Link 追い越しバッファの制御

図 18: Responsive Link パケットフォーマット

| エラー訂正(1バイト)  | ラインコード                                      | 符号化率                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              | BS+NRZI (9, 8)                              | 29.6%                                                                                                                                                                                                                                                                                                                                                                                |

| BCH (16, 8)  | 8b10b (10, 8)                               | 26.7%                                                                                                                                                                                                                                                                                                                                                                                |

|              | 4b10b (10, 4)                               | 13.3%                                                                                                                                                                                                                                                                                                                                                                                |

|              | BS+NRZI (9, 8)                              | 39.5%                                                                                                                                                                                                                                                                                                                                                                                |

| ハミング (12, 8) | 8b10b (10, 8)                               | 35.6%                                                                                                                                                                                                                                                                                                                                                                                |

|              | 4b10b (10, 4)                               | 17.8%                                                                                                                                                                                                                                                                                                                                                                                |

| ECC 無し       | 8b10b (10, 8)                               | 53.3%                                                                                                                                                                                                                                                                                                                                                                                |

|              | 4b10b (10, 4)                               | 26.7%                                                                                                                                                                                                                                                                                                                                                                                |

|              | BS+NRZI (9, 8)                              | 44.4%                                                                                                                                                                                                                                                                                                                                                                                |

| BCH (16, 8)  | 8b10b (10, 8)                               | 40.0%                                                                                                                                                                                                                                                                                                                                                                                |

|              | 4b10b (10, 4)                               | 20.0%                                                                                                                                                                                                                                                                                                                                                                                |

|              | BS+NRZI (9, 8)                              | 59.3%                                                                                                                                                                                                                                                                                                                                                                                |

| ハミング (12, 8) | 8b10b (10, 8)                               | 53.3%                                                                                                                                                                                                                                                                                                                                                                                |

|              | 4b10b (10, 4)                               | 26.7%                                                                                                                                                                                                                                                                                                                                                                                |

| ECC 無し       | 8b10b (10, 8)                               | 80.0%                                                                                                                                                                                                                                                                                                                                                                                |

|              | 4b10b (10, 4)                               | 40.0%                                                                                                                                                                                                                                                                                                                                                                                |

|              | BCH (16, 8) ハミング (12, 8) ECC 無し BCH (16, 8) | BS+NRZI (9, 8)  BCH (16, 8)  BS+NRZI (9, 8)  4b10b (10, 4)  BS+NRZI (9, 8)  ハミング (12, 8)  Bb10b (10, 8)  4b10b (10, 4)  ECC 無し  BS+NRZI (9, 8)  4b10b (10, 4)  BS+NRZI (9, 8)  BCH (16, 8)  BS+NRZI (9, 8)  4b10b (10, 4)  BS+NRZI (9, 8)  Ab10b (10, 4)  BS+NRZI (9, 8)  Ab10b (10, 4)  BS+NRZI (9, 8)  Ab10b (10, 8)  BS+NRZI (9, 8)  Ab10b (10, 8)  BS+NRZI (9, 8)  Ab10b (10, 8) |

図 19: Responsive Link の各種符号化

4. 3 「D-RMTP I SoC/SiP の設計・実装・検証・評価」(慶大 基盤ハードウェア・ソフトウェア グループ)

#### ① 実施方法・実施内容

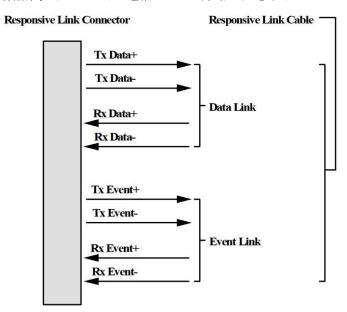

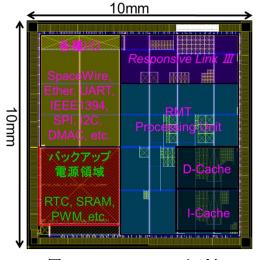

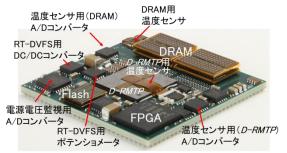

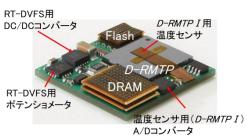

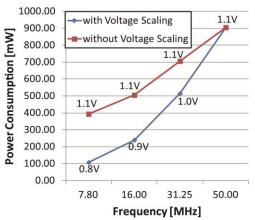

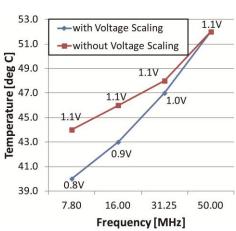

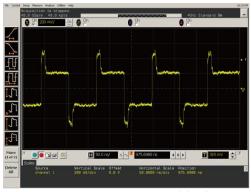

ロボットの分散制御を実現する SoC である D-RMTP I を設計・実装・評価した。D-RMTP I には、リアルタイム処理機能及びリアルタイム通信機能、さらにはロボットの分散制御に必要な全ての I/O を集積した初の SoC である(図 20,21,22 参照)[26]。そして、D-RMTP I SoC、DRAM、Flash memory、電圧センサ、温度センサ、及び DVFS のための電源モジュール等を30mm 角(図 23 参照)及び 20mm 角(図 24 参照)のサイズに集積した SiP を実現した。コアに供給する電圧と周波数を動的に制御することにより消費電力量を 1/5 以下に削減可能であることを実証した[24,30]。実機評価の結果、電圧 1.1V 時の消費電力は 693mW、電圧 0.80V の時の消費電力は 120mW であり、電圧と周波数を動的に制御することにより消費電力量を 1/5 以下に削減可能であることを実証した(図 25,26 参照)[24,30]。同様に、D-RMTP I 用のスケジューリングアルゴリズムの研究、及び、スレッドの実行速度を一定に制御する IPC 制御機構を用いたリアルタイム DVFS の検証を行った。さらに、 $Responsive\ Link$ のディペンダビリティ(特にリアルタイム性と信頼性(耐ノイズ性))に関して実機及びシミュレーションの両面から評価を行い、非常に高いリアルタイム性(100  $\mu$  sec オーダ)と耐ノイズ性(強力なエラー検出及びエラー訂正能力)を有していることを実機検証した(図 27,28 参照)[17,22,25,27,29]。

# ② 創造性

D-RMTP I SoC は上述したように、リアルタイム処理機能 (RMT 実行、IPC 制御、コンテキストキャッシュ)及びリアルタイム通信機能 (Responsive Link)というユニークな機能を備えている。これらの機能 (RT-DVFS、IPC 制御、Responsive Linkのノイズ耐性等) に関する評価を行い、ディペンダビリティを示した。

# ③ 有用性

D-RMTP I SiP 上の AD コンバータによりコア及び DRAM に供給される電源電圧をソフトウェアからモニタリングできるため、RT-DVFS の際に電圧が指定した値に確実に遷移してから周波数制御を行うことができる。これによってプログラムの安定的な動作を保証してディペンダビリティを向上させ、かつ、リアルタイム性を維持しながら消費電力を削減できる。また、ロボットの体内等の非常にノイズが大きい場所においても信頼性が高く時間粒度の細かいリアルタイム通信を実現することがでる。分散リアルタイムシステムを構築するために必要なほぼ全ての機能をSoC/SiPとして超小型かつディペンダブルに実現し、産業的なインパクトも大きい。

# ④ 優位比較

プロセッシングコアと DRAM の温度をソフトウェアからリアルタイムに監視できるため、デバイスの動作環境(温度等)に応じて電圧及び動作周波数をディペンダブルに調節することができる。本研究ではデバイスの電圧と温度をリアルタイムに観測しつつ RT-DVFS を行うスケジューリングアルゴリズム及び機構を研究開発しており、このようなアプローチはロボットや宇宙機等過酷な条件で動作する組込みアプリケーションにおいてディペンダビリティを実現するために重要である。 D-RMTP は周辺 I/O 機能を有した単なる 1 チップマイコンではなく、プロセッシングコアや通信機構にディペンダブルなリアルタイム処理・通信機能を有しており、このような SoC は他に存在しない。

# Dependable Responsive Multithreaded Processor I

図 20: *D-RMTP I* ブロック図

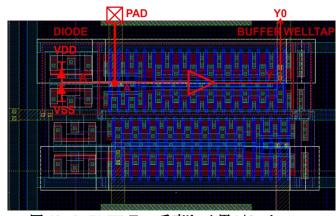

図 21: D-RMTP I レイアウト

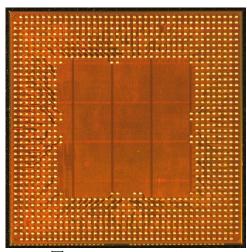

図 22: D-RMTP I SoC

図 23: 30mm 角 D-RMTP I SiP

図 24: 20mm 角 D-RMTP I SiP

図 25: D-RMTP I の消費電力

図 26: D-RMTP I の温度

図 27: Responsive Link 送信波形

図 28: Responsive Link 受信波形 (ノイズあり)

4. 4 「D-RMTP I におけるリアルタイムオペレーティングシステム」(慶大 基盤ソフトウェアグループ)

# ① 実施方法•実施内容

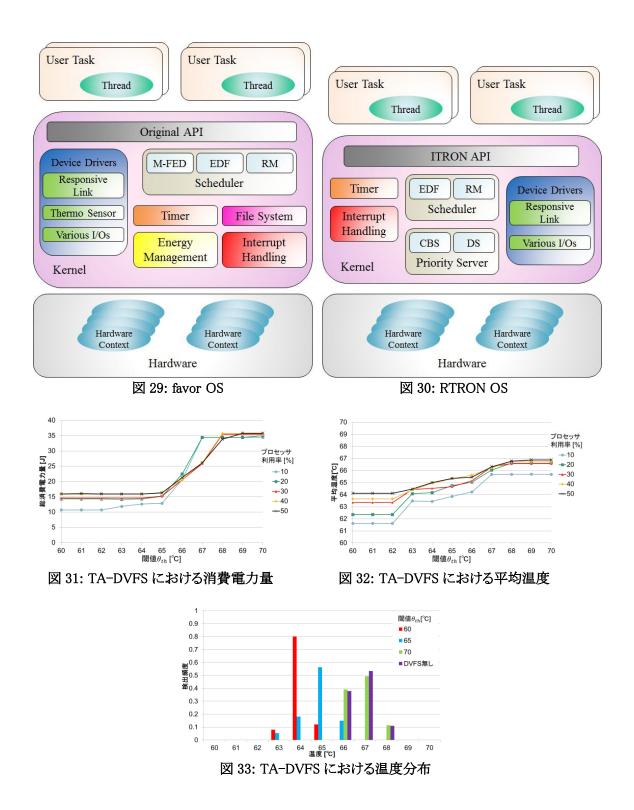

D-RMTPI上で動作するための基盤ソフトウェア (リアルタイムオペレーティングシステム) として、favor OS (図 29 参照) と RTRON OS (図 30 参照) [9,31]を開発した。favor OS は D-RMTP 向けに独自設計したリアルタイムオペレーティングシステムであり、RTRON OS は  $\mu$  ITRON 仕様のリアルタイムオペレーティングシステムである。これらの OS の特徴としては、D-RMTP固有機能を利用するための API を実装したことである。具体的には、ハードウェアによるリアルタイムスケジューリングを可能にする優先度付き SMT 実行 (RMT 実行)、コンテキストスイッチのオーバヘッドを

削減するコンテキストキャッシュ等の D-RMTP 固有機能をサポートしている。

favor OS は、インプリサイス計算モデル及びそのリアルタイムスケジュールアルゴリズム Mandatory-First with Earliest Deadline (M-FED)を実装しており、温度センサを読み込むことにより温度を考慮しつつ時間制約を保証する Temperature-Aware (TA)-DVFS を実現する。 Favor OS では、D-RMTPの固有機能であるタイマー割り込みによるスレッドの起床機能を使用することで、従来までは不可能であった  $10~\mu$  sec オーダの時間粒度の周期タスクである  $Responsive\ Task$ を実現している[37]。

これに対して、RTRON OS は D-RMTP I 固有機能を μ ITRON 仕様の API で利用可能であり、 時間制約を保証しつつ非周期イベントの応答性を向上させる優先度サーバ Constant Bandwidth Server(CBS)と Deferrable Server (DS)を実装している[9,31]。

D-RMTPISiP には DVFS を実現するための各モジュールや温度センサが実装されている。温度を閾値として用いた DVFS を適用した場合の消費電力量と平均温度、温度分布を図 31、図 32 及び図 33 に示す。図から分かるように、SiP 上の温度センサを用いて SoC の温度を読み取り、その温度が閾値を超過した場合に周波数と電圧を下げることで SoC の温度を一定値以下に保っことを可能とした[33,39]。図 31 と図 32 より閾値を下げ周波数と電圧を下げる機会を増やすことで、消費電力量と平均温度を下げられていることが見て取れる。また、図 33 より DVFS を行わなかった場合と比べ、SoC の温度上昇を抑えて設定した閾値付近の温度に保たれていることが見て取れる。このようにして、D-RMTPISiP において SoC の温度を考慮した動的な消費電力削減を実現した。さらには、D-RMTPISiP におけるインプリサイス計算モデルを用いた周波数電圧制御を行った[40]。これにより、周波数電圧制御による消費電力の削減とインプリサイス計算による精度向上のトレードオフの制御を実現した。

## ② 創造性

組込み分野で広く普及している $\mu$  ITRON 仕様に則ったリアルタイムオペレーティングシステムを D-RMTP I 向けに拡張した。また、D-RMTP ISoC 上で動作する独自のリアルタイムオペレーティングシステムの開発を行い、TA-DVFS の実機評価を行った。さらには、 $10~\mu$  sec の時間粒度で周期タスクを実現する  $Responsive\ Task$ を実現した。

# ③ 有用性

D-RMTP / 固有のリアルタイム処理機能である RMT 実行(優先度付き SMT 実行)を有効利用しつつ、 $\mu$  ITRON 仕様の APIをサポートすることに成功した。これにより、D-RMTP / 固有の機能を利用したアプリケーションを  $\mu$  ITRON 仕様の API を用いて開発することが可能になる。

# ④ 優位比較

$\mu$  ITRON 仕様のマルチプロセッサ向け OS は名古屋大学の TOPPERS/FDMP や東京大学の T-Kernel 等が存在するが、D-RMTP I 固有のリアルタイム処理機能である RMT 実行(優先度付き SMT 実行)及び IPC 制御機構をサポートした  $\mu$  ITRON 仕様のリアルタイムオペレーティングシステムを実現することで、非常に時間粒度の細かいリアルタイム処理を TRON ベースで実現可能にした。

時間粒度  $10 \mu$  sec の周期タスクを実行することのできる Responsive Taskを実現した。従来のリアルタイム処理の時間粒度は 1msec 程度であったため、非常に時間解像度の高い(従来比 100 倍程度の)リアルタイム処理を実現することが可能となった。

4.5 「分散制御用 D-RMTP II SoC の実現」(慶大 基盤ハードウェアグループ)

# ① 実施方法・実施内容

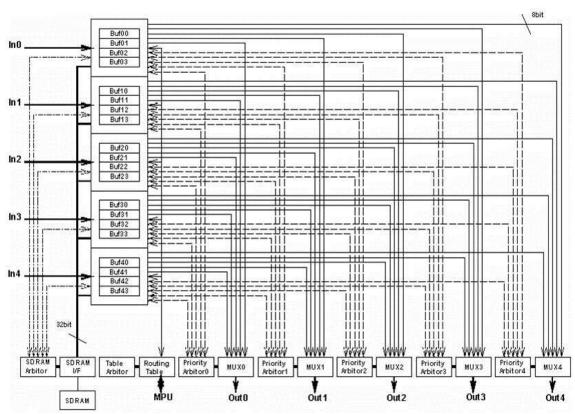

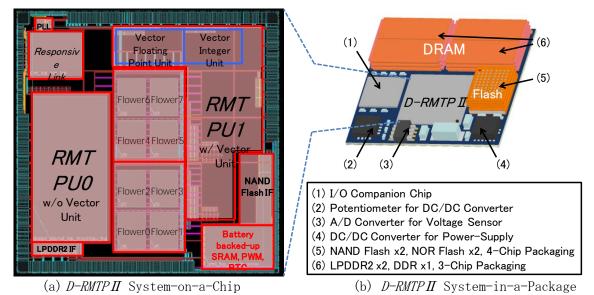

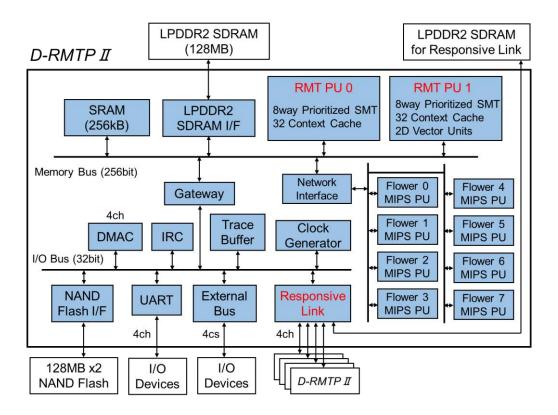

3 種類の特徴の異なる複数の CPU を RT-NoC (Real-Time Network-on-Chip)で接続し、さらにはメモリインタフェース(LPDDR2 IF, NAND Flash IF)やリアルタイム通信リンクである Responsive Link を集積した SoC である D-RMTP IIの研究開発を行った(図 34 参照)。 RMT 実

行(優先度付 SMT)と IPC 制御等によって実現するプロセッサ内部のリアルタイム処理、3 次元リアルタイムオンチップネットワーク(3D RT-NoC)により実現するチップ内リアルタイム通信、Responsive Linkにより実現するチップ間リアルタイム通信によって、時間粒度の非常に細かいリアルタイム性を有した分散リアルタイムシステムを実現可能にした。同時に、8 系統の電源ドメイン、20 系統のクロックドメインを設計・実装しており、RT-DVFS を用いて、高精度のリアルタイム処理を非常に低消費電力で行うことが可能となっている。

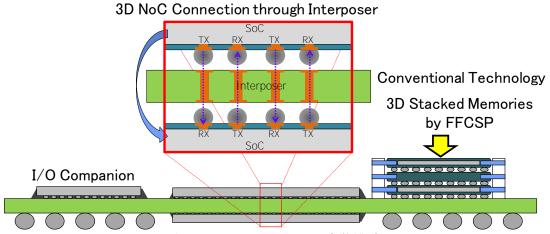

具体的には、リアルタイムオンチップネットワーク(RT-NoC)[10,15,21,28,32]を用いて、リアル タイム処理用プロセッサ及び各種 I/O を 1 チップに集積した並列分散リアルタイム処理用 SoC である D-RMTPIIを設計した(図 35,36,37 参照)[23, 37]。 D-RMTPIIは、組込みアプリケーショ ン向けに、大きさや機能及び速度の異なるプロセッサ、メモリ、及び各種 I/O を柔軟に統合して いる。D-RMTPIIに集積するリアルタイム処理用プロセッシングコアとして、RMT PUをベースに した高性能なマルチスレッドプロセッサ(RMT PUO及びRMT PUI)を設計し、さらにシンプルな 構成の並列処理用プロセッサ(Flower)を新規に設計した(図 35 参照)。 *RMT PU0*及び *RMT PU* I は D-RMTP Iと同様に 8 スレッドを同時実行可能である。 さらに、RMT PU1 には一度に大量 のデータを扱うデータ並列性を抽出するリアルタイムマルチメディア処理(画像や音声処理等) を行うために、2 次元ベクトルプロセッシングユニットを設計実装している。 Flower は RMT PU命 令セットアーキテクチャを備えた並列処理用プロセッサであり、*D-RMTPI*I SoC 内に 8 個集積し ている。RMT PU0及び RMT PU 1と並列して動作可能であるため、D-RMTP II SoC では最大 24 スレッドを同時実行することができる。 さらに、これらのプロセッシングコアと各種 I/O 及びメモ リモジュールを相互接続するために、プリエンプション(優先度によるパケット追い越し)が可能な RT-NoC を研究開発した。具体的には、パケットに8ビット(256 段階)の優先度を付与して優先 度制御を行い、さらには優先度逆転問題に対処する機構をも備えており、高優先度パケットの ジッタを低減し時間制約に関して高いディペンダビリティを有することを確認している[21]。 RT-NoC は、チップ内コアの接続だけではなく、チップ間接続用リンクとしての機能をも果たす (図 38,39 参照)。この実現のために、チップ間接続用に、ESD 付きの垂直リンク用 I/O バッファ (図40参照)を新規に設計・実装している。

また、D-RMTPII SoC2 個を 3 次元 RT-NoC で接続し、さらにそれらと I/O Core SoC とをバスで接続した 20mm 角 D-RMTPII SiP を設計実装した(図 38,39 参照)。異なるチップ間を 3 次元 RT-NoC により通信することで、SiP 上の D-RMTPII及び IO Core SoC で合計 49 スレッドを同時実行可能となり、多種多様なアプリケーションに対応できるようにした。

図 34: 分散リアルタイム処理用プロセッサ D-RMTP II SoC/SiP

図 35: D-RMTP II SoC のブロック図

図 36: D-RMTPII の RDL パターン

図 37: D-RMTP II のチップ写真

図 38: D-RMTPII SiP のブロック図

図 39: D-RMTP II SiP の実装構造

図 40: D-RMTP II の垂直リンク用 I/O バッファ

#### ② 創造性

*D-RMTPII* SoC はチップ内に特徴の異なる3種類のプロセッサをRT-NoC で接続し、ヘテロジニアスなマルチコアを実現している。その際、SoC内処理、SoC内通信、SiP内 SoC間通信、SiP間通信の全てにおいて、リアルタイム性を有している点に大きな創造性がある。

また、D-RMTPII SiP は 20mm 角という非常に小型なサイズでありながらも、D-RMTPII SoC 2 個と I/O 制御用チップ (I/O Core SoC) を 3 次元 RT-NoC で接続することで最大 49 スレッドの同時実行を可能とした。

# ③ 有用性

D-RMTPII SoC には大きさの異なる 3 種類の CPU が実装されており、各々性質の異なるリアルタイム処理をすることができる。 20mm 角という非常に小型の SiP に、2 個の D-RMTPII SoC、I/O core SoC、DRAM (LPDDR2, DDR)、NAND flash 等を集積している。非常に小型で低消費電力なので色々な箇所に埋め込んで機器の制御をできると共に、49 スレッド同時実行、177 スレッド並行実行することができ、異なる性質を持つ制御用スレッドを全て同時に動かすことも可能となる。

#### ④ 優位比較

用途に応じた3種類の大きさ・機能の異なるコア(CPU)を複数個実装して24スレッド同時実行でき、当該スレッドの実行に最適なコアを選択することにより、電力消費を抑えたリアルタイム処理を行うことができる。また、組込み用プロセッサにおいて88スレッドも並行実行できるプロセッサは他には存在しない。さらには、演算処理、チップ内通信、チップ間通信の全てにおいてリアルタイム性を有したプロセッサは他には存在しない。

4.6 「評価キットの実現」(NEC プラットフォームズグループ)

# ① 実施方法・実施内容

NECPF グループは、基盤ハードウェアグループとコデザインを行いつつ、FFCSP を応用した 3 次元 SiP の設計、シミュレーション、実装組立、テストを行い、最適な実装要素技術を研究開発 することにより、ディペンダブルかつ低コスト、高性能、低消費電力な VLSI システムの構築を目指す。基盤ハードウェアグループと共同で 30 mm 角 D-RMTPI SiP [19]を実装した評価キットの研究開発・製造を行った(図 41 参照)。D-RMTPI SoC/SiP の豊富な機能を名刺サイズで全て利用でき、USB バスパワーもしくは 5V 単一電源で容易に評価できるようにした。

図 41: 30mm 角 D-RMTP I SiP 評価キット

#### ② 創造性

30mm 角 *D-RMTP I* 評価キットは非常に多くの I/O ピンや USB2.0 インタフェースを備えながらも小型化(名刺サイズ)を実現している。それにより、ディペンダビリティの各評価指標(例:リアルタイム性、消費電力、耐ノイズ性等)の評価を容易に実現可能にした。

# ③ 有用性

D-RMTP I の豊富な I/O を全て実装すると共に、ホストインタフェースとして新規に評価キット基板上に USB2.0 インタフェースを実装した評価キットを設計実装した。 $Responsive\ Link$  によるリアルタイム通信、D-RMTP I のリアルタイム処理機能 (IPC 制御機構等)、RT-DVFS 機構等を本評価キットで簡単に評価できるようになった。

#### ④ 優位比較

非常に多くの種類の I/O を搭載した評価キットでありながら、名刺サイズを実現している。I/O としては、Responsive Link, SpaceWire, IEEE1394, Ethernet, USB2.0 (Host&Peripheral), PWM 発生器, PWM 入力, Pulse counter, Digital port, RS232C, SPI, ADC, PIO, JTAG (RMTP&FPGA) を搭載している[2,26]。外部から供給する電源は、ユーザが使いやすいように、DC ジャックからの 5V 単一電源か USB バスパワーのどちからで動作するように設計している。また、リアルタイム通信、リアルタイム処理機能、RT-DVFS 機構等を容易に試すことができる。

# 4.7 「高良品率を実現する3次元実装の実現」(NEC プラットフォームズグループ)

#### ① 実施方法・実施内容

本研究では LSI の近傍に性能維持のための部品を実装し、LSI の性能を維持しつつ、LSI を 3 次元実装する前に個々に回路的良品、不良品の判定を実施し、3 次元実装の最大の問題点である性能の低下と LSI の不良の積み重ねを回避した SiPを実現する手法を確立した。

# ② 創造性

LSIのみならず抵抗・コンデンサ等の受動部品も内蔵し、各段を単独でテスト/評価した後に全体の実装を行うことで、システム全体の良品率向上を実現した。

# ③ 有用性

LSIを多段に実装する際のLSIと周辺回路を含めた回路性能の多段化による劣化を防止しながら、LSIの多段実装を実現した。

# ④ 優位比較

TSV 等の3次元実装では、3次元実装前にはウェハレベルの良、不良の判定しか実現できておらず、多段実装を進めるに従い、LSI 本来の性能の低下と不良の積み重ねを招いている。本研究で採用したFFCSPはLSIの近傍に性能維持のための部品を配置し、LSIの性能低下を回避しつつ、3次元実装する前にLSIの良・不良の判定を実施し、良品のみを3次元実装することで高い製造品質を実現している。

# 4.8 「ハイブリッド FPC による 3 次元実装」 (NEC プラットフォームズグループ)

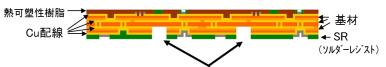

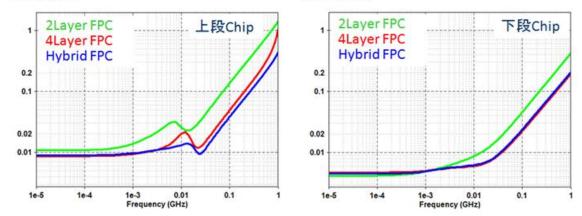

# ① 実施方法•実施内容

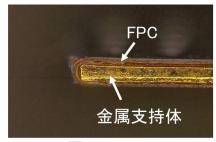

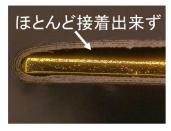

FFCSP において FPC の配線層数を 2 層から 4 層にすることにより、高速信号や電源をアナログ的に安定させて高信頼性を実現する。単なる 4 層では FFCSP の折り曲げが正常にできないため、折り曲げ部分のみ 2 層構造とすることで、高速伝送における信号安定性と折り曲げ易さを併せ持つハイブリッド FPC を研究開発した(図 42,43 参照)[40]。

2層FPCの断面 (正常に接着)

3層FPC断面 (隙間の発生)

4層FPCの断面 (未接着)

外側面の折曲げ部分にあたる、配線層2層と基材1層を削除

4層の性能を維持しつつ2層の製造性と 同様の曲げ及び接着性

図 42: ハイブリッド FPC

図 43: 2 層-4 層ハイブリッド FPC モデルのシミュレーション結果

図 44: ハイブリッド FPC を用いた DRAM モジュール

# ② 創造性

場所に応じて配線層を2層と4層に使い分けることで、信号の安定性と折り曲げやすさを両立した FPC を実現した。

# ③ 有用性

本技術により、3 次元実装における課題である高速信号および電源の安定性を解決しつつ、組立易いディペンダブルな3次元実装を実現できる(図44参照)。

# ④ 優位比較

TSVによる3次元実装と比較して信号密度は劣るが、LSIへの安定した電源供給による低ノイズを実現でき、かつ金属支持体による放熱により、ディペンダビリティの高いシステムを構築できる。

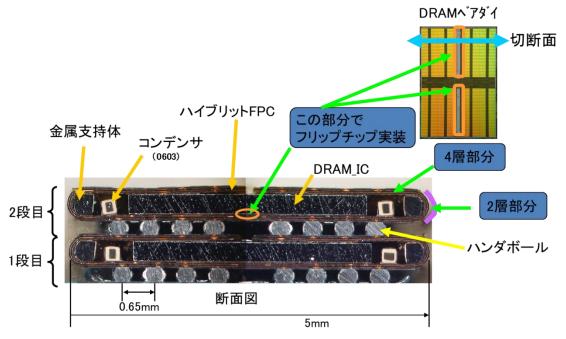

4.9 「LSI の多段実装の実現」(NEC プラットフォームズグループ)

#### ① 実施方法・実施内容

組込みアプリケーショングループの要求を受け、基板ハードウェアグループとのコデザインを実施し、20mm 角 D-RMTPI SiP と同じ大きさで DRMTP-IIを実装して 3D-NoC を実現するためには DRAM ベアチップと Flash ベアチップの高密度実装を実現しなければならない。更に D-RMTPII SiP においては DRAM に関しては DDR と DDR2、また Flash memory に関しては Nor Flash と Nand Flash のように、異種の VLSI の積層実装を要求される。それを実現するために FFCSP 技術を採用しているが、従来の 4 層 FPC では実現できないため、6 層FPCを採用して、異種 LSI の多層実装を実現した(図 45,46 参照)。

図 45: DRAM の 3 段実装

図 46: Flash の 4 段実装

## ② 創造性

異種の VLSI を多段実装するために、FPC 用いて VLSI ベアチップを包み込み、それをハンダボールを介してモジュール間を接続して VLSI を積層することで、VLSI の多段実装を実現している。また積層するものは VLSI のみならず周辺回路 (抵抗・コンデンサ等)も一緒に積層することができ、ディペンダビリティを向上させることが可能である。

#### ③ 有用性

異種の VLSI を多段実装する手段にはいくつかの方法が提案されているが、本研究で採用した FFCSP は異種の VLSI の多段を実現する方法として設計と製造が単純である。その結果、特殊なツールや知識を用いることなく多段の 3 次元実装が実現できる。

#### ④ 優位比較

異種の VLSI を多段実装する手段はいくつか存在するが、本研究で取り上げたFPCを用いた 多段実装は、基板を設計する技術で多段実装を実現するという開発優位性が非常に高い。新たな開発環境も必要無く、製造に際しては、従来の半田付け工程がそのまま利用でき、新たな装置を必要としない。

# 4. 10 「DRMTP SiP 搭載ロボットアクチュエータ制御用モジュールの開発」(東大グループ)

#### ① 実施方法・実施内容

ダイナミックレンジの大きな高効率なモータ電流制御回路及びモータ内部温度推定機能に基づく大出力発揮可能な高効率モータ駆動モジュール(2軸対応)の開発を行った[48]。また、開発したモータ駆動モジュールを用いた大出力脚の設計・実装・評価を行った[46,47,48,49]。

このモータ駆動モジュールの制御システム用として高速リアルタイム制御性、高ノイズ下通信可用性、低レイテンシ通信リアルタイム性を備えた  $30 \,\mathrm{mm}$  角 D-RMTPI SiP [19]を搭載した通信制御用基板の開発及び評価を行った(図 47,48 参照)。また、D-RMTPI の機能を極小パッケージに収めた  $20 \,\mathrm{mm}$  角 D-RMTPI SiP を用いて、細見の人型ロボットに搭載可能なアクチュエータコントロール/センサ入力/汎用入出力を行う D-RMTPI 搭載分散制御基板モジュール及び切符サイズの汎用小型モータ駆動モジュールの開発を行った(図 49,50 参照)。

さらに、I/O core SiP 及び 20mm 角 D-RMTP I 汎用制御基板による大出力モータ駆動を行うために BtoB コネクタを搭載したモータ駆動モジュールの開発を行った(図 51 参照)。

モータの高速リアルタイム制御を実現するために D-RMTPIのリアルタイム処理機能を利用した高速応答モータ制御プログラム及び運動軌道生成プログラムを実装し、試験機にて応答性能を評価した。

図 47: 30mm 角 D-RMTP I SiP 搭載制御基板

図 48: 大出力モータ駆動モジュール

図 49: 汎用小型モータ駆動モジュール

図 50: 20mm 角 *D-RMTP* 制御モジュール

図 51: B to B コネクタ搭載モータ駆動モジュール

# ② 創造性

大出力モータ駆動モジュールにリアルタイム処理可能なプロセッサを搭載した *D-RMTP I* SiP を使用することで、モータ制御タスクに専用スレッドを割り当てたりセンサ割込み信号に対する即応的な制御を可能にする等の高度なリアルタイム制御計算を行うモータ制御モジュールを非常に小型に製作することが可能となり、これまでにない高速応答性を備えたロボットの制御システムの実現可能性を示した。

# ③ 有用性

本技術により、等身大のヒューマノイドに十分搭載可能なモータ駆動基板サイズにおいて、介護等をロボットが行うのに十分な関節トルクを発揮しつつ、各モータ駆動基板において高度なリアルタイム制御計算を独立して実現可能となった。これにより大出力ヒューマノイドによる作業支援の実用に向けて十分な信頼性を備えた制御システムを構築するための基盤ができあがった。

また小型制御モジュールとモータ駆動モジュールの開発により、全身に 100 以上のアクチュエータを持ち、さらにそれ以上の数のセンサを持った人間模倣ヒューマノイドロボットにおいても、高い信頼性を備えたアクチュエータ/センサネットワークが容易に構築できるようになる。 従来は

小型化などのために商用マイコンを用いて専用基板を開発し、USB などの汎用の規格の通信路を用いていたが、本技術により電磁ノイズに強く高いリアルタイム性のある通信経路を確保し、汎用モジュール群を構築して採用していくことで、ロボットの迅速な開発が可能になる。

#### ④ 優位比較

従来の大出力を目指したロボットは、万が一暴走した場合を想定し基本的には囲いによって 人を遠ざけてないと利用することができなかった。しかし、本プロジェクトによるディペンダブルな 制御系と組み合わせることで、より安全性を向上させた制御システムを構築できる可能性が生ま れるため、本技術はロボットの現場普及への重要なキーファクタであると考える。

また、自動車の車体内通信に用いられる CAN や、近年ロボット分野で用いられている Ether-CAT のような通信規格はあるが、それらを用いたアクチュエータ/センサシステムとしての 信頼性、リアルタイム性を得ようとすると専用の基板を開発する必要があった。本 SiP 技術を用いれば、ディペンダビリティが保証された通信経路を得ることができ、容易に信頼性の高いアクチュエータ/センサアレイを構築することができる。相互に接続可能な小型の分散型モジュールとして設計することにより、高い拡張性を備えさせることが可能となる。

こうした、高い信頼性を持ちつつ素早いシステム構築が可能な拡張性の高いモジュール群は、 新たな要求に素早く応え、日々研究開発される新技術を取り組んだモジュールを試すことができるシステムであり、今後のロボットの普及において必要不可欠な要素であると考える。

# 4. 11 「ロボットへの組込みにおけるディペンダビリティ評価」(東大グループ)

# ① 実施方法・実施内容

開発したリアルタイムプロセッサをロボットへ組み込むにあたってのディペンダビリティ評価として、一般的なヒューマノイドロボットである HRP2、大出力駆動系を有した大出力ヒューマノイドロボット、および筋骨格ヒューマノイドロボット体内のノイズ・温度環境を測定し、開発したリアルタイムプロセッサおよびリアルタイム通信が問題なく動作することを確認した。

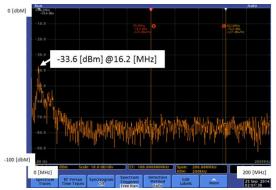

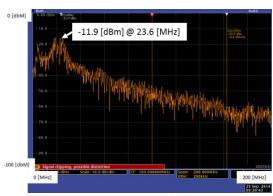

図 52 は一般的なヒューマノイドロボット HRP2 の体内におけるノイズ環境を測定したもので、ピーク値は 16.2MHz において-33.6dBm であった。一方で、図 53 に示すように、大出力駆動系を有する大出力ヒューマノイド体内のノイズ環境は HRP2 のそれと比べて大幅に大きく、ピーク値は 23.6 MHz において-11.9dBm であった [50]。

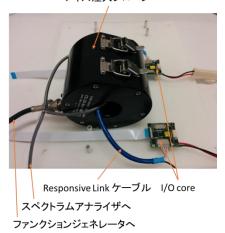

この環境下において、リアルタイム通信が問題なく行えるかを確認するために、Responsive Linkのノイズ耐性を測定した。ノイズ耐性試験装置は図 54 に示すもので、Responsive Linkのケーブルにノイズ注入 CT でノイズを注入し、通信が途絶した時のノイズ強度を測定した。測定の結果 12MHz において+18dBmのノイズを印加した時に通信が途絶することが分かった。また、図 55 上に示すシールド無の Responsive Link ケーブルとシールド、図 55 下に示すツイストペアの Responsive Link ケーブルを比較したところ、ノイズ耐性は 0.1dBm の差しか見られず、Responsive Linkのノイズ耐性の高さを確認できた。これらの結果から、Responsive Link は非常に高いノイズ耐性を有しており、ロボット体内のノイズ環境に対して十分なマージンを持つことが分かった。

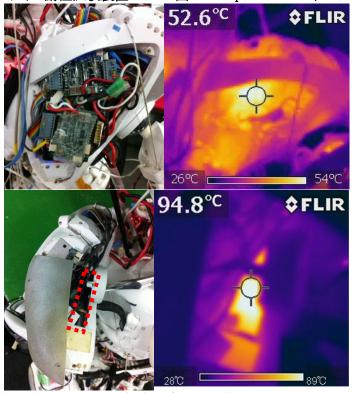

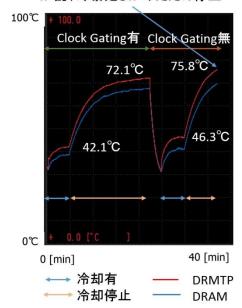

一方で、温度環境に関して、図 56 は筋骨格ヒューマノイドに 10kg のおもりを持ち上げさせる高負荷運動を行わせた時の制御基板周辺の温度分布を測定した物である。この結果から、モータ部は非常に高温になっているが、制御基板周辺は50℃前後であることが分かる。図 57 は4. 11において開発した 30mm 角 *D-RMTP I* SIP 上の CPU コアの温度と DRAM の温度を測定したもので、冷却ファンによる強制空冷を停止した後、何度まで動作可能かを測定した結果である。測定の結果、CPU コアが約 70~75℃程度まで動作可能であることが分かった。この結果から、筋骨格ヒューマノイドのように制御基板が高密度実装されているようなロボット体内の温度環境においても問題なく動作可能であることが確認できた。また、図 57 に示すように、制御に不必要なモジュールに対してはクロック供給を停止することで消費電流と発熱量を抑えることが可能であり、温度環境の厳しいロボット体内において有効な機能であることが確認できた。

図 52:HRP2 体内のノイズ環境 ノイズ注入プローブ

図 53:大出力ヒューマノイド体内のノイズ環境

図 54:ノイズ耐性試験装置

図 55:Responsive Link ケーブル

図 56: 高負荷運動時の筋骨格ヒューマノイド体内温度(上:制御基板周辺、下:モータ周辺)

# モータ制御スレッドの制御周期が乱れ、暴走しかけたため停止

図 57:動作限界温度の測定及びクロック停止による効果

#### ② 創造性

これまでに、ロボット体内に組み込む制御機器に関して、このようなディペンダビリティ評価は行われてこなかったが、今回の結果から、ロボット体内のノイズおよび温度環境下で問題なく動作することが確認でき、この成果によりディペンダブルなロボットを設計する上での指標を明らかとすることができた。

# ③ 有用性

ロボット体内に開発したプロセッサを組み込むためのディペンダビリティ評価指標を明らかとすることで、よりディペンダブルなロボットを開発することも可能であるし、最低限のディペンダビリティを確保しつつ、より高性能なロボットを実現することも可能となる。例えば、Responsive Link の高ノイズ耐性を生かして、より高出力なアクチュエータを搭載しロボットの運動能力を向上させたり、プロセッサの未使用モジュールへのクロック供給を停止し体内温度を下げることで、より高密度に制御機器を実装し、よりスリムなロボットを実現したりといった設計が可能になる。

# ④ 優位比較

評価結果から分かるようにロボット体内には非常に狭い空間内に多数の制御機器を組み込む必要があるため、高温・高ノイズ環境であることが分かる。評価の結果、Responsive Link は従来ロボットの通信に用いていた RS-485 や USB よりも高速であり、リアルタイム通信が可能であるうえに、高いノイズ耐性を持っていることが分かった。

また、制御機器が密集している筋骨格ヒューマノイドでは、ロボット体内が高温の環境になるが、開発したリアルタイムプロセッサ(*D-RMTP I*)はその環境下でも問題なく動作可能であり、さらに、使用していないモジュールへのクロック供給を停止することで温度を低く抑えることが可能である。

4.12 「大出力発揮可能な高効率モータ駆動制御モジュールの Responsive Link 通信を用いた制御」(東大グループ)

# ① 実施方法・実施内容

D-RMTP I を搭載したダイナミックレンジの大きな高効率なモータ電流制御回路及びモータ内部温度推定機能に基づく大出力発揮可能な高効率モータ駆動モジュールを用いて、 Responsive Link 通信を通して制御を行った。また、既存ロボットの通信系を I/O Core を用いて Responsive Link 通信に容易に置き換えて検証を行えることを示した。

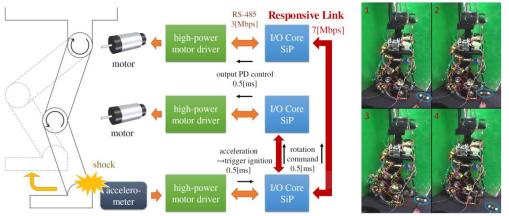

を搭載したモータ駆動モジュールを開発し、大出力駆動系に組み込み評価を行った。図 58 に示すように 2 つのモータを用いたマスター・スレーブ系を構築し、D-RMTPIの高速リアルタイム制御性により制御周期を 500  $\mu$  s で制御し、 $Responsive\ Link$  通信によりマスターの指令値をスレーブ側に低レイテンシで送信可能であることを示した[48]。

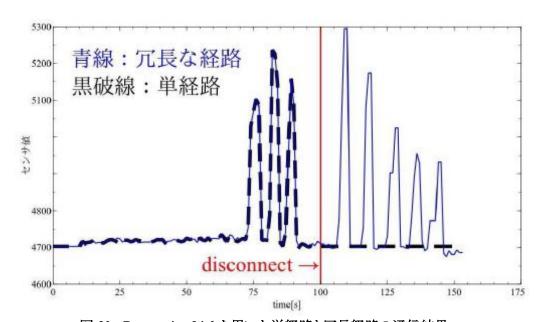

図 58: D-RMTP I による2モータ同期制御

また、I/O Core を用いたロボットへの組込評価として、大出力脚ロボットに対して、モータ駆動モジュールへの送受信に従来 RS-485を用いていた部分を Responsive Link へと置き換えを行った(図 59 参照)。置き換えには、開発した I/O Core を用いた。ロボット体内の I/O Core 同士は Responsive Link で通信し、各ノードとモータ駆動モジュール間は RS-485 で通信を行うことで容易に置き換え可能であることが示せた。加えて、冗長なトポロジを構成することで冗長経路が切断されても制御を継続できることを示せた(図 60 参照)[51]。大出力脚において、衝撃センサモジュール信号を Responsive Link を用いて全身の各軸へ送信し、衝撃応答動作を可能とするシステムを構成することで、通常システムでは最短でも数 msec かかっていた応答動作を数十~数百  $\mu$  sec のオーダに短縮することが可能になることを示した(図 61 参照)[52]。

また、筋骨格ロボットのように大規模分散制御系においては、全身のモータ駆動モジュール間の通信レイテンシの増大が問題であったが、*Responsive Linkを*実装しているI/O Core を適用することで全身の筋を同期制御する見通しを示すことができた。

図 59: 大出力脚ロボットへの I/O Core の組み込み

図 60: Responsive Link を用いた単経路と冗長経路の通信結果

図 61: Responsive Linkを用いた大出力脚ロボットでの衝撃応答システム

#### ② 創造性

D-RMTP I をロボットのモータ制御モジュールに適用することで高速リアルタイム制御が可能となることを示すだけでなく、分散リアルタイム制御系を構築する上で有用である低レイテンシリアルタイム通信の機能を I/O Core を用いることで容易に既存ロボットに適用可能であることを示した。

## ③ 有用性

本技術により、全身 20 自由度程度を想定した等身大ヒューマノイドに十分搭載可能な駆動基板サイズにおいて、従来技術での駆動系よりも飛躍的にモータ駆動出力が高まり、人間と同程度の関節速度及びトルクを発揮可能なヒューマノイドが構築可能となるため、介護現場を始めとする将来的なヒューマノイドの社会進出を現実的なものと推進する基礎技術として期待できる。従来ではモータ駆動モジュールへの送受信は RS-485 等を用いた通信を行っており、リアルタイム性に問題があり、耐ノイズ性を高めるために符号化のための追加ロジックを必要としていた。RS-485 では数 Mbps 程度の通信レートであるが、Responsive Link では 800Mbps までの通信が可能となり、高精度なロボット制御が可能になる。

## ④ 優位比較

単純な軸出力においては、Boston Dynamics 社の油圧駆動系よりも劣るが、制御性においては本技術によるモータ駆動系に大きな優位性があり、介護現場等で必要とされる繊細な作業を行うことが可能である。また既存のモータ制御基板を用いた介護を想定したヒューマノイドは数多くあり(早稲田 Twendy、理研 RI-MAN)、一方で実際の介護現場においては、人を支えることのできる十分な関節トルクや咄嗟に人を支えられるだけの瞬間的な関節速度が不可欠であり、センサモジュールと組み合わせて状況に応じたフィードバックによるモータ駆動が不可欠である。

このように、こうした大出力モータ駆動系の実現はヒューマノイドの介護分野で大きなブレイクスルーとなりうる。現在用いられている RS-485 といった通信では力センサをフィードバックし柔らかな動作をするために必要な制御ループをヒューマノイド全身で実現することが困難である。ここで、通信速度が速くリアルタイム性がありディペンダブルな制御系が構築できる本技術が非常に優位であり、現場普及への重要なキーファクタであると考える。

## § 5 成果発表等

(1)原著論文発表 (国内(和文)誌 19 件、国際(欧文)誌 32 件) 〈慶大グループ〉

- 1. 千代 浩之, 武田 瑛, 船岡 健司, 山﨑 信行, "拡張インプリサイスタスクの固定優先度 スケジューリング", 第 21 回コンピュータシステムシンポジウム, pp. 67-74, つくば, 2009 年 11 月.

- 2. Yusuke Murata, Takuma Kogo, and Nobuyuki Yamasaki, "A SpaceWire Extension for Distributed Real-Time Systems," Proc. of the Third International SpaceWire Conference, pp. 349-355, St. Petersburg, June 2010.

- 3. Hiroyuki Chishiro and Nobuyuki Yamasaki, "Semi-Fixed-Priority Scheduling: New Priority Assignment Policy for Practical Imprecise Computation," Proc. of the 15th IEEE International Conference on Embedded and Real-Time Computing Systems and Applications, pp. 339-348, Macau, August 2010 (DOI: 10.1109/RTCSA.2010.30).

- 4. 稲垣文二, 山﨑信行, "リアルタイム実行のための優先度付きSMT プロセッサ用 IPC 制御機構", 情報処理学会論文誌, Vol. 51, No. 12, pp. 2206-2215, 2010 年 12 月.

- 5. 池田雄児, 山﨑信行, "SMT/CMP 向け固定優先度スケジューリング用動的電圧周波数制御の提案とRMT Processor を用いた実機評価", 情報処理学会論文誌, Vol. 51, No. 12, pp. 2216-2226, 2010 年 12 月.

- 6. 千代浩之, 山﨑信行, "優先度付き SMT Processor における準固定優先度スケジューリング", 情報処理学会論文誌, Vol. 51, No. 12, pp. 2227-2237, 2010 年 12 月.

- 7. Hiroyuki Chishiro and Nobuyuki Yamasaki, "Performance Evaluation of Semi-Fixed-Priority Scheduling on Prioritized SMT Processors," Proc. of the 10th IASTED International Conference on Parallel and Distributed Computing and Networks, pp. 75–82, Innsbruck, February 2011.

- 8. 千代浩之,山崎信行,"準固定優先度スケジューリング向けリアルタイムオペレーティングシステム",情報処理学会論文誌:コンピューティングシステム,4巻1号,2011年2月.

- 9. Rikuhei Ueda, Kei Fujii, Hiroyuki Chishiro, Hiroki Matsutani, and Nobuyuki Yamasaki, "An Extension of Real-Time OS for Multithreaded Processors," The 18th IEEE Real-Time and Embedded Technology and Applications Symposium, Work-In-Progress session, pp. 53-56, April, 2011.

- 10. 向後卓磨, 山﨑信行, "優先度付きオンチップネットワークのための VIX ルータとその評価", 第9回先進的計算基盤シンポジウム, pp. 381-390, 2011 年5月.

- 11. Shinpei Kato and Nobuyuki Yamasaki, "Global EDF-based Scheduling with Laxity-Driven Priority Promotion," J. Syst. Archit. Vol. 57, Issue 5, pp. 498-517, May, 2011.

- 12. 千代浩之, 武田瑛, 船岡健司, 山﨑信行, "Rate Monotonic に基づく拡張インプリサイス タスク用リアルタイムスケジューリング", 情報処理学会論文誌, 52巻8号, pp. 2365-2377, 2011年8月.

- 13. Kei Fujii, Hiroyuki Chishiro, Hiroki Matsutani, and Nobuyuki Yamasaki, "Dynamic Voltage and Frequency Scaling for Real-Time Scheduling on a Prioritized SMT Processor," Proc. of the 1st International Workshop on Cyber-Physical Systems, Networks, and Applications, pp. 9-15, Toyama, August 2011 (DOI: 10.1109/RTCSA.2011.78).

- 14. Kohei Matsumoto, Hiroyuki Umeo, and Nobuyuki Yamasaki, "A Thread Speed Control Scheme for Real-time Microprocessors," Proc. of the 1st International Workshop on Cyber-Physical Systems, Networks, and Applications, pp. 16-21, Toyama, August 2011 (DOI: 10.1109/RTCSA.2011.77).

- 15. Masakazu Taniguchi, Hiroki Matsutani, and Nobuyuki Yamasaki, "Design and Implementation of On-chip Adaptive Router with Predictor for Regional Congestion," Proc. of the 1st International Workshop on Cyber-Physical Systems, Networks, and Applications, pp. 22–27, Toyama, August 2011 (DOI: 10.1109/RTCSA.2011.61).

- 16. Hiroyuki Chishiro and Nobuyuki Yamasaki, "Global Semi-Fixed-Priority Scheduling on Multiprocessors," Proc. of the 17th IEEE International Conference on Embedded and Real-Time Computing Systems and Applications, pp. 218-223, Toyama, August 2011 (DOI: 10.1109/RTCSA.2011.32).

- 17. 山﨑信行, 松井俊浩, "分散制御用リアルタイム通信規格 Responsive Link", 情報処理 学会デジタルプラクティス, 2 巻 4 号, pp. 246-254, 2011 年 10 月. (招待論文)

- 18. Hiroyuki Chishiro and Nobuyuki Yamasaki, "RT-Est: Real-Time Operating System for Semi-Fixed-Priority Scheduling Algorithms," Proc. of the 2011 International Symposium on Embedded and Pervasive Systems, pp. 358-365, Melbourne, October 2011 (DOI: 10.1109/EUC.2011.60).

- 19. Kazutoshi Suito, Kei Fujii, Hiroki Matsutani, and Nobuyuki Yamasaki, "Dependable Responsive Multithreaded Processor for Distributed Real-Time Systems," Proc. of the 15th IEEE Symposium on Low-Power and High-Speed Chips (COOL Chips XV), Yokohama, April 2012.

- 20. Hiroyuki Chishiro and Nobuyuki Yamasaki, "Experimental Evaluation of Global and Partitioned Semi-Fixed-Priority Scheduling Algorithms on Multicore Systems," The 15th IEEE International Symposium on Object/Component/Service-Oriented Real-Time

- Distributed Computing, pp. 127-134, April, 2012.

- 21. 谷口将一, 松谷宏紀, 山崎信行, "予測を用いた NoC 向け混雑回避機構", 情報処理学会論文誌コンピューティングシステム, Vol.5, No.3, pp.112-123, 2012 年 5 月.

- 22. Hiroyuki Chishiro and Nobuyuki Yamasaki, "Distributed Real-Time Environment on Responsive Link," Proc. of the 18th International Conference on Parallel and Distributed Processing Techniques and Applications, pp. 151–157, Las Vegas, July 2012.

- 23. 川瀬大樹, 水頭一壽, 松谷宏紀, 山崎信行, "ヘテロジニアスなマルチコアプロセッサ向け分散 TLB 機構の実装と評価", DA シンポジウム 2012, pp.79-84, 2012 年 8 月.

- 24. 高須雅義, 上田陸平, 藤井啓, 千代浩之, 松谷宏紀, 山崎信行, "Dependable Responsive Multithreaded Processor の省電力機構の実機評価", 組込みシステムシンポジウム, pp.79-86, 2012 年 10 月.

- 25. Hiroyuki Chishiro and Nobuyuki Yamasaki, "Distributed Real-Time Systems on Responsive Link", Journal of Communication and Computer, Vol.9, No.12, pp.52-61, December 2012.

- 26. Kazutoshi Suito, Rikuhei Ueda, Kei Fujii, Takuma Kogo, Hiroki Matsutani, and Nobuyuki Yamasaki, "Dependable Responsive Multithreaded Processor for Distributed Real-Time Systems," IEEE Micro, Vol.32, No.6, pp.52-61, December 2012.

- 27. 水頭一壽, 向後卓磨, 松谷宏紀, 山﨑信行, "Responsive Link を用いた分散リアルタイムシステム向け高信頼な通信機構の設計と実装," 情報処理学会論文誌, Vol.53, No.12, pp.2728-2739, 2012 年 12 月.

- 28. 水頭一壽, 向後卓磨, 山崎大輝, 松谷宏紀, 山崎信行, "優先度付きオンチップルータ VIX", 情報処理学会論文誌コンピューティングシステム, Vol.6, No.1, pp.87-98, 2013 年 1 月.

- 29. Osamu Yoshizumi, Hiroki Matsutani, and Nobuyuki Yamasaki, "Packet Routing for Distributed Real-Time System on Real-Time Communication Link," Proc. of the 28th ISCA International Conference on Computers and Their Applications, pp. 197-204, March, 2013.

- 30. Kazutoshi Suito, Masayoshi Takasu, Rikuhei Ueda, Kei Fujii, Hiroki Matsutani, and Nobuyuki Yamasaki, "Experimental Evaluation of Low Power Techniques on Dependable Responsive Multithreaded Processor," Proc. of the 28th ISCA International Conference on Computers and Their Applications, pp. 281–288, March, 2013.

- 31. 上田陸平, 藤井啓, 千代浩之, 松谷宏紀, 山﨑信行, "ITRON 仕様 OS の RMT Processor 向け実装", 情報処理学会論文誌, Vol. 54, No. 7, pp. 1835-1848, 2013 年 7 日

- 32. 谷口将一, 山崎大輝, 笹川雄二郎, 松谷宏紀, 山崎信行, "優先度逆転を低減させる優先度付きオンチップネットワーク向けルータアーキテクチャ", 情報処理学会論文誌, 54巻, 7号, pp. 1861-1872, 2013 年 7月.

- 33. 溝谷圭悟, 上田陸平, 高須雅義, 千代浩之, 松谷宏紀, 山﨑信行, "インプリサイス計算モデルにおける Temperature-Aware DVFS", 組込みシステムシンポジウム 2013, pp. 17-26, 東京, 2013 年 10 月.

- 34. Hiroyuki Chishiro and Nobuyuki Yamasaki, "Semi-Fixed-Priority Scheduling with Multiple Mandatory Parts," The 16th IEEE International Symposium on Object/Component/Service-Oriented Real-Time Distributed Computing, Germany, pp. 1-8, Paderborn, June 2013.

- 35. Hiroyuki Chishiro, James H. Anderson (UNC-CH), and Nobuyuki Yamasaki, "An Evaluation of the RUN Algorithm in LITMUS RT," ACM SIGBED Review, Vol. 10, No. 2, p. 29, July 2013.

- 36. Yusuke Kumura, Kazutoshi Suito, Hiroki Matsutani, and Nobuyuki Yamasaki, "A Low-Power Link Speed Control Method on Distributed Real-time Systems," The 7th

- IEEE International Symposium on Embedded Multicore Systems-on-Chip, pp.49-54, Tokyo, September 2013.

- 37. Nobuyuki Yamasaki, "Co-Design of Dependable Responsive Multithreaded Processor II (DRMTP-II) SoC and SiP," The International Workshop on Innovative Architecture for Future Generation High-Performance Processors and Systems, Hawaii, March 2014.

- 38. Hiroyuki Chishiro and Nobuyuki Yamasaki, "Practical Imprecise Computation Model: Theory and Practice," The 17th IEEE International Symposium on Object/Component/Service-Oriented Real-Time Distributed Computing, pp. 198-205, Reno, June 2014.

- 39. 溝谷圭悟,上田陸平,高須雅義,千代浩之,松谷宏紀,山崎信行,"インプリサイス計算モデルにおける温度を考慮した動的電圧周波数制御の実機評価",情報処理学会論文誌,55巻,8号,pp. 1841-1855,2014年8月.

- 40. Keigo Mizotani, Yusuke Hatori, Yusuke Kumura, Masayoshi Takasu, Hiroyuki Chishiro, and Nobuyuki Yamasaki, "An Integration of Imprecise Computation Model and Real-Time Voltage and Frequency Scaling," The 30th International Conference on Computers and Their Applications, pp. 63-70, Hawaii, March 2015.

- 41. Hiroyuki Chishiro and Nobuyuki Yamasaki, "Zero-Jitter Technique for Semi-Fixed-Priority Scheduling with Harmonic Periodic Task Sets," The 30th International Conference on Computers and Their Applications, pp. 371-378, Hawaii, March 2015.

- 42. Yusuke Kumura, Keigo Mizotani, Masayoshi Takasu, Hiroyuki Chishiro, and Nobuyuki Yamasaki, "Overhead-Aware Schedulability Analysis on Responsive Multithreaded Processor," The 30th International Conference on Computers and Their Applications, pp. 379–386, Hawaii, March 2015.

- 43. Masayoshi Takasu, Keigo Mizotani, Yusuke Kumura, Hiroyuki Chishiro, and Nobuyuki Yamasaki, "Leakage-Aware Energy-Efficient Partitioning for Real-Time Tasks on Multiprocessor Systems," The 30th International Conference on Computers and Their Applications, pp. 393-400, Hawaii, March 2015.

### 〈NEC プラットフォームズグループ〉

- 44. 和田喜久男, 大須良二, 樋野滋一, 山﨑信行, "三次元実装パッケージ実現のためのハイブリッド FPC の提案, Vol. J93-C, No. 11, pp. 455-463, 2010 年 11 月.

- 45. Kikuo Wada, Shigekazu Hino (HINO Jisso Design), and Nobuyuki Yamasaki, "Three-dimensional packaging structure for 3D-NoC," The 2013 IEEE Electrical Design of Advanced Packaging & Systems Symposium, pp. 72-75, Dec. 2013.

# 〈東大グループ〉

- 46. 浦田順一, 中西雄飛, 岡田慧, 稲葉雅幸 (東大), "高速・高トルク動作のための大出力 2 脚ロボットの開発", 日本ロボット学会誌, vol.28, No.07, pp.91-97, 2010 年

- 47. Junichi Urata, Yuto Nakanishi, Kei Okada, Masayuki Inaba (Univ. of Tokyo), "Design of High Torque and High Speed Leg Module for High Power Humanoid", IEEE/RSJ 2010 International Conference on Intelligent Robots and Systems, Taipei, Taiwan, October 2010

- 48. Nobuyuki Ito, Junichi Urata, Yuto Nakanishi, Kei Okada, Masayuki Inaba (Univ. of Tokyo), "Development of Small Motor Driver Integrating Sensor Circuit and Interchengeable Communication Board", Journal of Robotics and Mechatronics, Vol.23, No.2, pp. 443-450, June 2011

- 49. Junichi Urata (Univ. of Tokyo), Koichi Nishiwaki (AIST), Yuto Nakanishi, Kei Okada (Univ. of Tokyo), Satoshi Kagami (AIST), Masayuki Inaba (Univ. of Tokyo), "Online Decision of

- Foot Placement using Singular LQ Preview Regulation", 2011 IEEE-RAS International Conference on Humanoid Robots, pp. 13–18, Bled, October 2011 (DOI: 10.1109/Humanoids.2011.6100894)

- 50. Junichi Urata (Univ. of Tokyo), Koichi Nishiwaki (AIST), Yuto Nakanishi (Univ. of Tokyo), Kei Okada (Univ. of Tokyo), Satoshi Kagami (AIST), Masayuki Inaba (Univ. of Tokyo), "Online Walking Pattern Generation for Push Recovery and Minimum Delay to Commanded Change of Direction and Speed", IEEE/RSJ International Conference on Intelligent Robots and Systems 2012, Portugal, October 2012

- 51. Yoshito Ito, Takuya Nakaoka, Junichi Urata, Yuto Nakanishi, Kei Okada, Masayuki Inaba (Univ. of Tokyo), "Design and Development of a Tendon-driven and Axial-driven Hybrid Humanoid Leg with High-Power Motor Driving System", IEEE-RAS International Conference on Humanoid Robots 2012, Osaka, November 2012

#### (3)国際学会発表及び主要な国内学会発表

- ① 招待講演 (国内会議 1件、国際会議 1件)

- ② 口頭発表 (国内会議 37 件、国際会議 3 件)

- ③ ポスター発表 (国内会議 8件、国際会議 2件)

# 〈慶大グループ〉

- 1. 向後 卓磨, 山﨑 信行, "低遅延リアルタイムオンチップネットワークのための先読みルータ の設計," 電子情報通信学会技術研究報告:組込み技術とネットワークに関するワークショップ, pp. 465-470, 八丈島, 2010 年 3 月

- 2. 笹川 雄二郎, 向後 卓磨, 山﨑 信行, "リアルタイムオンチップネットワーク向け先読みアービトレーション機構付ルータの設計と実装,"電子情報通信学会技術研究報告:組込み技術とネットワークに関するワークショップ, pp. 55-61, 八丈島, 2010 年 3 月

- 3. 稲垣 文二, 梅尾 寛之, 村田 裕介, 山﨑 信行, "Responsive Multithreaded Processor における IPC 制御機構の設計と実装,"電子情報通信学会技術研究報告:組込み技術とネットワークに関するワークショップ, pp. 295-302, 八丈島, 2010年3月

- 4. 藤井 啓, 千代 浩之, 山﨑 信行, "優先度付き SMT プロセッサ向け実時間動的電圧周波数制御,"電子情報通信学会技術研究報告:組込み技術とネットワークに関するワークショップ, pp. 433-440, 八丈島, 2010 年 3 月

- 5. 千代 浩之, 山崎 信行, "RT ミドルウェアのリアルタイム拡張," ロボティクス・メカトロニクス 講演会 2010, pp. 2P1-A19, 旭川, 2010 年 6 月.

- 6. 石川 洋輔, 山崎 信行, "マルチプロセッサ向け先読み同期プロトコル," 情報科学技術フォーラム, pp. 351-360, 福岡, 2010 年 9 月

- 7. 千代 浩之, 山﨑 信行, "リアルタイムオペレーティングシステム RT-Est におけるハイブリッド O(1)スケジューラ," 第 12 回 組込みシステム技術に関するサマーワークショップ, pp. 88-90, 豊橋, 2010 年 9 月.

- 8. 向後 卓磨, 山崎 信行, "優先度付きオンチップネットワーク向けのルータアーキテクチャ," 電子情報通信学会技術研究報告: デザインガイア 2010, pp. 13-18, 福岡, 2010 年 12 月

- 9. 向後 卓磨, 山崎 信行, "優先度制御を考慮したオンチップルータ VIX の設計及び実装(電子情報通 信学会 集積回路研究会 優秀若手講演賞)," 第 185 回計算機アーキテクチャ研究発表会, Vol. 193, No. 17, pp. 1-6, 2011 年 1 月

- 10. 利長 勇児, 村田 裕介, 山﨑 信行, "ベクトルデータのキャッシュ置き換え制御機構の設計と実装,"情報処理学会研究報告:組込み技術とネットワークに関するワークショップ, pp. 207-212, 宮古島, 2011 年 3 月

- 11. 吉住 修, 石川 洋輔, 山崎 信行, "RMT プロセッサにおける実行効率を向上するリアルタイムスケジューリング," 情報処理学会研究報告:組込み技術とネットワークに関するワ

- ークショップ, pp. 1-6, 宮古島, 2011年3月

- 12. 松本 康平, 梅尾 寛之, 山﨑 信行, "Responsive Multithreaded Processor におけるリアルタイム実行支援機構の設計と実装," 情報処理学会研究報告:組込み技術とネットワークに関するワークショップ, pp. 1-6, 宮古島, 2011年3月

- 13. 谷口 将一, 向後 卓磨, 山﨑 信行, "局所的な混雑を予測する オンチップアダプティブルータの設計と実装," 情報処理学会研究報告:組込み技術とネットワークに関するワークショップ, pp. 201-206, 宮古島, 2011 年 3 月

- 14. \* Nobuyuki Yamasaki, "Embedded Real-Time Processor for Massively Distributed Robot Control," Proceedings of 2011 VLSI Circuits Workshop Program, No.7, pp.1-35, Oct, 2011. (招待講演)

- 15. 吉住 修, 山崎 信行, "優先度付き SMT プロセッサ用リアルタイムスケジューリング," 組込みシステムシンポジウム 2011, pp. 1, 代々木, 2011 年 10 月

- 16. 水頭 一壽, 吉住 修, 松谷 宏紀, 山崎 信行, "Responsive Link をベースにした高信頼なリアルタイム通信機構の設計と評価," 第 189 回 ARC・第 132 回 HPC 合同研究発表会, pp. 1-8, 札幌, 2011 年 11 月

- 17. 笹川 雄二郎, 松谷 宏紀, 山﨑 信行, "優先度逆転問題を軽減する優先度付きオンチップネットワークルータ," 電子情報通信学会技術研究報告, pp. 41-46, 宮崎, 2011 年 11 月

- 18. 山崎 大輝, 松谷 宏紀, 山崎 信行, "トラフィック解析によるオンチップルータのバンド 幅制御," 電子情報通信学会技術研究報告: FPGA 応用および一般, pp. 61-66, 日吉, 2012年1月

- 19. 金田 健佑, 松本 康平, 山﨑 信行, "優先度付き SMT プロセッサにおけるリアルタイム 処理用 IPC 制御機構,"電子情報通信学会技術研究報告: FPGA 応用および一般, pp. 37-42, 日吉, 2012 年 1 月

- 20. 上田 陸平, 藤井 啓, 千代 浩之, 松谷 宏紀, 山﨑 信行, "TRON 仕様 OS のマルチ スレッドプロセッサ拡張,"電子情報通信学会技術研究報告: FPGA 応用および一般, pp. 43-48, 日吉, 2012 年 1 月

- 21. 吉住 修, 松谷 宏紀, 山崎 信行, "Responsive Link を用いた分散リアルタイムシステム におけるルーティ ング手法," 情報処理学会研究報告 2012-EMB-24, pp. 1-6, 宮城, 2012 年 3 月

- 22. 伊藤 康人,千代 浩之,松谷 宏紀,山崎 信行,"マルチスレッドプロセッサ向け組込み Java VM の実装,"電子情報通信学会技術研究報告:組込み技術とネットワークに関するワークショップ,pp. 181-186,宮城,2012年3月

- 23. 川口 雄輝, 水頭 一壽, 松谷 宏紀, 山﨑 信行, "ヘテロジニアスなマルチコアプロセッサ向け I/O 制御機構の設計と実装,"電子情報通信学会技術研究報告:組込み技術とネットワークに関するワークショップ, pp. 91-96, 宮城, 2012 年 3 月

- 24. 川瀬 大樹, 水頭 一壽, 松谷 宏紀, 山﨑 信行, "ヘテロジニアスなマルチコアプロセッサ向け分散 TLB 機構の設計と実装,"電子情報通信学会技術研究報告:組込み技術とネットワークに関するワークショップ, pp. 85-90, 宮城, 2012 年 3 月

- 25. 川瀬 大樹, 水頭 一壽, 松谷 宏紀, 山﨑 信行, "ヘテロジニアスなマルチコアプロセッサ向け分散 TLB 機構の設計および実装,"組込みシステム技術に関するサマーワークショップ, pp. 90-93, 下呂, 2012年8月

- 26. 水頭 一壽, 松谷 宏紀, 山﨑 信行, "Responsive Link を用いた分散リアルタイムシステム向け高信頼な通信機構,"組込みシステム技術に関するサマーワークショップ, pp. 109-112, 下呂, 2012年8月

- 27. 川口 雄輝, 水頭 一壽, 松谷 宏紀, 山崎 信行, "ヘテロジニアスなマルチコアプロセッサ向け I/0 制御機構の実装と評価,"組込みシステム技術に関するサマーワークショップ, pp. 86-89, 下呂, 2012 年 8 月

- 28. 千代 浩之, 山崎 信行, "マルチコアプロセッサにおけるインプリサイス計算向け

- リアルタイムスケジューリングの実機評価,"第 14 回 組込みシステム技術に関するサマーワークショップ, pp. 94-97, 下呂, 2012年8月

- 29. 久村 雄輔, 吉住 修, 水頭 一壽, 松谷 宏紀, 山崎 信行, "分散リアルタイムシステム における消費電力量を抑えるパケット転送手法," 電子情報通信学会技術研究報告 CPSY2012-75, Vol.112, No.376, pp.111-116, 日吉, 2013 年 1 月

- 30. 石田 匠, 山崎 大輝, 谷口 将一, 水頭 一壽, 松谷 宏紀, 山崎 信行, "優先度逆転 を考慮した優先度付きオンチップネットワークの設計と実装," 電子情報通信学会技術研究 報告 CPSY2012-73, Vol.112, No.376, pp.99-104, 日吉, 2013 年 1 月

- 31. 高橋昌裕, 久村雄輔, 吉住修, 水頭一壽, 松谷宏紀, 山崎信行, "Responsive Link における伝送路符号化方式の動的切替手法," 電子情報通信学会技術研究報告 CPSY2012-91, Vol.112, No.481, pp.235-240, 対馬, 2013年3月

- 32. 溝谷圭悟, 上田陸平, 高須雅義, 千代浩之, 松谷宏紀, 山崎信行, "インプリサイス計算モデルにおける温度を考慮した DVFS 制御,"電子情報通信学会技術研究報告 CPSY2012-88, Vol.112, No.481, pp.217-222, 対馬, 2013年3月

- 33. 萩原秀磨, 久村雄輔, 山﨑信行(慶大), "Responsive Link を用いたスループット向上のためのルーティング手法," 電子情報通信学会技術研究報告 CPSY2013-112, pp. 259-264, 沖縄, 2014年3月16日

- 34. 羽鳥雄介, 上田陸平, 溝谷圭悟, 久村雄輔, 山﨑信行(慶大), "Responsive Link における TCP/IP プロトコルスタックの実装," 電子情報通信学会技術研究報告 CPSY2013-113, pp. 265-270, 沖縄, 2014 年 3 月 16 日

- 35. 大沢幸平, 萩原秀磨, 久村雄輔, 溝谷圭悟, 高須雅義, 山﨑信行, "Responsive Link を用いた通信遅延を考慮したパケットスケジューリング," 電子情報通信学会技術研究報告 CPSY2014-159, Vol. 114, No. 427, pp. 233-238, 日吉, 2015 年 1 月.

- 36. 大槻周平, 溝谷圭悟, 高須雅義, 山崎大輝, 山﨑信行, "優先度に基づくパケット追い越しとリソース制御を付加したNoCアーキテクチャ," 電子情報通信学会技術研究報告 CPSY2014-126, Vol. 114, No. 427, pp. 25-30, 日吉, 2015年1月.

- 37. 溝谷圭悟, 羽鳥雄介, 久村雄輔, 高須雅義, 千代浩之, 山﨑信行, "Dependable Responsive Multithreaded Processor における低遅延リアルタイム実行," 電子情報 通信学会技術研究報告 CPSY2014-158, Vol. 114, No. 427, pp. 227-232, 日吉, 2015年1月.

- 38. 山﨑信行, "並列分散リアルタイム処理用 Dependable Responsive Multithreaded Processor ~ロボット制御用 SoC/SiP/OS のコデザイン~," 電子情報通信学会技術研究報告 ICD2014-114, Vol. 114, No. 436, pp. 21-26, 日吉, 2015 年 1 月. (招待講演)

- 39. 村田太郎, 金田健佑, 高須雅義, 溝谷圭悟, 羽鳥雄介, 山﨑信行, "RMT Processor における資源利用率を考慮したスループット向上手法," 電子情報通信学会技術研究報告 CPSY2014-166, Vol. 114, No. 506, pp. 25-30, 奄美, 2015 年 3 月.

- 40. 松井司,萩原秀磨,溝谷圭悟,山﨑信行, "RMT Processor における優先度に応じた動的誤り訂正符号,"電子情報通信学会技術研究報告 CPSY2014-167, Vol. 114, No. 506, pp. 31-36, 奄美, 2015年3月.

- 41. 山田賢治,羽鳥雄介,萩原秀磨,溝谷圭悟,高須雅義,山﨑信行, "RMT Processor における IPC 制御を用いたリアルタイム静的電圧周波数制御," 電子情報 通信学会技術研究報告 CPSY2014-179, Vol. 114, No. 506, pp. 101-106, 奄美, 2015 年 3 月.

#### 〈東大グループ〉

42. 伊東信之,浦田順一,中西雄飛,岡田慧,稲葉雅幸(東大), "ヒューマノイドの為の超小型センサ統合大出力モータドライバの開発,"日本機械学会ロボティクス・メカトロニクス講演会,旭川,2010年6月

- 43. 浦田順一, 伊東信之, 中西雄飛, 岡田慧, 稲葉雅幸 (東大), 山崎信行 (慶大), "ヒューマノイドロボットのための実時間プロセッサ: D-RMTP搭載大出力モータドライバモジュールの設計,"第 28 回日本ロボット学会学術講演会, 名古屋, 2010 年 9 月

- 44. 中岡卓也, 浦田順一, 伊東信之, 中西雄飛, 岡田慧, 稲葉雅幸 (東大), 山﨑信行 (慶大), "実時間プロセッサ RMTP 搭載モータドライバモジュールの開発およびモータの制御,"第 29 回日本ロボット学会学術講演会, 東京, 2011 年 9 月

- 45. 浦田順一(東大),西脇光一(産総研),中西雄飛,岡田慧(東大),加賀美聡(産総研),稲葉雅幸(東大),"最適レギュレータの入力重み0とした極限を用いた二足歩行におけるオンライン着地位置・時刻最適化の実現,"第29回日本ロボット学会学術講演会,東京,2011年9月

- 46. 中岡卓也, 浦田順一, 伊藤佳人, 小林一也, 中西雄飛, 岡田慧, 稲葉雅幸 (東大), 山 崎信行 (慶大), "小型大出力モータドライバ系による駆動力・即応性を備えた等身大ヒュー マノイド用アームの設計と実装,"第30回日本ロボット学会学術講演会, 北海道, 2012 年 9 月

- 47. 中岡卓也, 浦田順一, 柚木崎創, 伊藤佳人, 小林一也, 中西雄飛, 岡田慧, 稲葉雅幸 (東大), "全身大出力ヒューマノイドのための液冷ダブルモータユニットを備えた二脚ロボット の設計と実装,"第31回日本ロボット学会学術講演会, 東京, 2013年9月4日

- 48. 白井拓磨, 浦田順一, 中西雄飛, 垣内洋平(東大), 上田陸平, 久村雄輔, 山崎信行(慶大), 稲葉雅幸(東大), "実時間プロセッサ RMTP と実時間通信 Responsive Link によるモータの2軸同期制御,"第31回日本ロボット学会学術講演会, 東京, 2013年9月5

- 49. 垣内洋平, 白井拓磨, 菅井文仁, 大久保壮一, 熊谷伊織, 永松祐弥, 岡田慧, 稲葉雅幸(東大), 和田喜久男(NEC プラットフォームズ), 山崎信行(慶大), "ディペンダブルなロボット用組込プロセッサ系の開発,"第32回日本ロボット学会学術講演会, 福岡, 2014年9月4日

- 50. 永松祐弥, 白井拓磨, 大久保壮一, 熊谷伊織, 菅井文仁, 垣内洋平, 岡田慧, 稲葉雅幸(東大), 溝谷圭悟, 久村雄輔, 山崎信行(慶大), "実時間通信 Responsive Link 付き I/O Core を用いた大出力脚制御システムの構成と評価," 第 15 回計測自動制御学会システムインテグレーション部門講演会, 東京, 2014 年 12 月

- 51. 大久保壮一, 白井拓磨, 永松祐弥, 熊谷伊織, 菅井文仁, 垣内洋平, 岡田慧, 稲葉雅幸(東大), 溝谷圭悟, 久村雄輔, 山崎信行(慶大), "分散制御システム向け実時間通信 Responsive Link を備えた I/O Core SiP 基板による多自由度ヒューマノ イド制御システムの構成と評価," 第 15 回計測自動制御学会システムインテグレーション部門講演会, 東京, 2014 年 12 月

- 52. 永松祐弥, 白井拓磨, 大久保壮一, 熊谷伊織, 菅井文仁, 垣内洋平, 岡田慧, 稲葉雅幸 (東大), 大沢幸平, 山崎信行(慶大), "実時間通信 Responsive Link 型体内通信系を備えた大出力ヒューマノイドにおける衝撃反射応答行動の実現," 日本機械学会ロボティクス・メカトロニクス講演会,京都, 2015 年 5 月

#### (4)知財出願

## ①国内出願(3件)

- 1. 半導体装置 増田靜昭 NEC アクセステクニカ(株) 2014/02/26 特願 2014-035284

- 2. 3 次元実装型半導体装置および電子機器 増田靜昭 NEC アクセステクニカ(株) 2011/01/17 特願 2011-006890

- 3. ディジタル通信の伝送路符号の変換方法及びこの変換方法を行う符号の生成方法、山﨑信行、学校法人 慶應義塾、2012/01/26、特願 2012-14181

### ②海外出願(2件)

- 1. THREE-DIMENSIONALLY INTEGRATED SEMICONDUCTOR DEVICE AND ELECTRONIC DEVICE INCORPORATION BY REFERENCE 增田靜昭 NECAccess Technica Ltd 2010/10/07 PCT/IP2010/068104

- 2. 半導体装置及びそれを用いた電子機器 増田靜昭 NEC アクセステクニカ(株) 2012/01/17 13/351409

#### (5)受賞•報道等

# ① 受賞

- 1. 向後卓磨 (慶大),優秀若手研究賞,第9回先進的計算基盤シンポジウム,2011年5月

- 2. 伊東信之, 浦田順一, 中西雄飛, 岡田慧, 稲葉雅幸 (東大), JSME Fellow Award for Outstanding Young Engineers, ROBOMEC2010, 2011 年 6 月 (ヒューマノイドの為の超小型センサ統合大出力モータドライバの開発)

- 3. 笹川雄二郎 (慶大), 優秀若手講演賞, 電子情報通信学会 コンピュータシステム研究会, 2011 年 11 月

- 4. 川口雄輝 (慶大), 優秀発表学生賞, 情報処理学会 システム LSI 設計技術研究会, 2012年3月

- 5. 川瀬大樹 (慶大), 優秀発表学生賞, 情報処理学会 システム LSI 設計技術研究会, 2012年3月

- 6. K.Mizotani, Y.Hatori, Y.Kumura, M.Takasu, H.Chishiro, and N.Yamasaki, Best Paper Award, 30<sup>th</sup> ISCA International Conference on Computers and Their Applications (CATA2015), 2015 年 3 月

- ② マスコミ(新聞・TV等)報道(プレス発表をした場合にはその概要もお書き下さい。)

- 1. IEEE spectrum にて、大出力脚の転倒回避デモンストレーションを発表(2012年5月8日) <a href="http://spectrum.ieee.org/automaton/robotics/humanoids/japanese-high-power-humanoid-robot-hrp31-jsk">http://spectrum.ieee.org/automaton/robotics/humanoids/japanese-high-power-humanoid-robot-hrp31-jsk</a>

なお、埋め込まれた youtube 動画は 2015 年 3 月現在、30 万 PV を達成し、世界へ技術成果を発信している。

2. IEEE spectrum にて、分散検証プラットフォーム筋骨格ヒューマノイド小次郎を発表(2010 年 3 月 4 日)

http://spectrum.ieee.org/automaton/robotics/humanoids/kojiro-musculoskele

tal-humanoid-robot

なお、埋め込まれた youtube 動画は 2015 年 3 月現在、87 万 PV を達成し、世界へ技術成果を発信している。

### ③その他

## (6)成果展開事例、出口活動

#### ①実用化に向けての展開

(1) エラー訂正付きラインコード 4b10b の標準化

エラー訂正付きのラインコードである 4b10b を新規に研究開発したが、ISO/IEC 標準になるべく、まずは国内において情報処理学会試行標準として標準化を開始した。標準化することによって、本通信規格の普及を促進する。

## (2)評価キットの配布による普及促進

名刺サイズの小型の D-RMTP 評価キットを設計・実装した。D-RMTP Iの豊富な I/O を全てユーザが利用できるように拡張基板と合わせて 2 枚構成とし、ホストとのインタフェースは PC 等で広く採用されている USB2.0 を採用し、更に Host と Device の両方の機能を搭載した。評価キットの外部電源は USB バスパワーか 5V 単一電源を採用し、ユーザが使いやすい評価キット)した。その評価キットを研究開発者に配布し、普及の促進を図っている。ET 展示会に出展し、研究成果のアピールを実施した。その結果、FFCSP での LSI の多段実装のサンプル作成の商談の引き合いや D-RMTPの応用に関する申し込みなどがあった。

さらに、より一般層への普及に向けて、入門的な I/O Core SoC/SiP、拡張基板を研究開発し、現在、これらを用いて普及を促進しているところである。

(3) ヒューマノイド開発・実用化へ向けたベンチャ企業の設立 「大出力脚プラットフォーム」に基づくベンチャ企業「株式会社 SCHAFT」を 2012 年 5 月に 設立した。

# ② 社会還元的な展開活動

- 本成果を慶應義塾大学山崎研 Web ページ(<a href="http://www.ny.ics.keio.ac.jp/">http://www.ny.ics.keio.ac.jp/</a>)で公開し、一般に情報提供している。

- 慶應義塾大学の矢上オープンキャンパスやK2オープンキャンパス等を通じて、CRESTにおける研究成果を一般向けに分かりやすく広報している。

## §6 研究期間中の活動

### 6. 1 主なワークショップ、シンポジウム、アウトリーチ等の活動

| 年月日        | 名称               | 場所    | 参加人数     | 概要                |

|------------|------------------|-------|----------|-------------------|

| 2010年3月    | 高校生見学対応          | 東大    | 20 人     | ロボット研究の見学、取材学     |

| 30 日       | (広島女学院高等学校)      |       |          | 習                 |

| 2010年7月8   | 高校生見学対応          | 東大    | 13 人     | ロボット研究の見学、取材学     |

| 日          | (仙台一高)           |       |          | 習                 |

| 2010年8月4   | オープンキャンパス        | 東大    | 多数       | 一般参加者の方へのロボ       |

| 日          |                  |       |          | ット研究室見学、稲葉教授      |

|            |                  |       |          | による公開講義           |

| 2010/12/1~ | ET2010           | パシフィコ | 21,988 人 | ET2010 のブースに出展し、研 |

| 12/3       |                  | 横浜    |          | 究内容の公開と見学者との      |

|            |                  |       |          | 研究の方向に関する議論       |

| 2010年12月   | KEIO TECHNO-MALL | 東京国際フ | 約 1000 人 | 研究内容のデモ展示とディ      |

| 10 日       | 2010             | オーラム  |          | スカッション            |

| 2011年7月    | 高校生見学対応          | 東大    | 2 人      | ロボット研究の見学、取材学     |

| 22 日       | (三重県高田高等学校)      |       |          | 꿤                 |

| 2011/11/16 | ET2011           | パシフィコ | 22,349 人 | ET2011 のブースに出展し、研 |

| ~11/18     |                  | 横浜    |          | 究内容の公開と見学者との      |

|            |                  |       |          | 研究の方向に関する議論       |

| 2011年12月9日           | KEIO TECHNO-MALL 2011                       | 東京国際フォーラム     | 約 1000 人 | 研究内容のデモ展示とディ<br>スカッション                   |

|----------------------|---------------------------------------------|---------------|----------|------------------------------------------|

| 2012 年 3 月 18 日      | 高校生アカデミックフィ<br>ールドワーク企業訪問<br>対応<br>(西京高等学校) | 東大            | 4人       | 大学における研究活動(ロボット研究)についての見学、学習             |

| 2012 年 8 月 6,7 日     | 高校生見学対応<br>(新潟南高等学校)                        | 東大            | 20 人     | ロボット研究についての見学、小型ロボットNAOを用いた実習、講義         |

| 2012/11/14<br>~11/16 | ET2012                                      | パシフィコ<br>横浜   | 28,419 人 | ET2011 のブースに出展し、研究内容の公開と見学者との研究の方向に関する議論 |

| 2012年12月<br>7日       | KEIO TECHNO-MALL<br>2012                    | 東京国際フ<br>ォーラム | 約 1000 人 | 研究内容のデモ展示とディ<br>スカッション                   |

| 2013 年 3 月 18 日      | 高校生アカデミックフィ<br>ールドワーク企業訪問<br>対応<br>(西京高等学校) | 東大            | 4人       | 大学における研究活動(ロボット研究)についての見学、学習             |

| 2013年11月<br>20日~22日  | ET2013                                      | パシフィコ<br>横浜   | 23,984 人 | ET2013のブースに出展し、研究内容の公開と見学者との研究の方向に関する議論  |

| 2013年12月<br>13日      | KEIO TECHNO-MALL<br>2013                    | 東京国際フォーラム     | 約 1000 人 | 研究内容のデモ展示とディ<br>スカッション                   |

| 2014年11月<br>19日~21日  | ET2014                                      | パシフィコ<br>横浜   | 22,507 人 | ET2014のブースに出展し、研究内容の公開と見学者との研究の方向に関する議論  |

| 2014年12月5日           | KEIO TECHNO-MALL<br>2014                    | 東京国際フォーラム     | 約 1000 人 | 研究内容のデモ展示とディ<br>スカッション                   |

# §7 最後に

研究中に領域総括並びにアドバイザーの先生方から多くの貴重な意見を頂き、我々の研究にフォードバックをすることができた。そのため、特に研究の出口を強く意識した研究開発をすることができたと考えている。例えば、研究開始当初には想定していなかった以下のような各種技術(IP、方式、SoC、SiP等)を出口として提供することができるようになった。

- ・組込み用途のディペンダビリティの評価指標

- ・各種評価キットによる IP 等の普及促進

- •D-RMTP SoC

- ・リアルタイム処理用プロセッサ

- -RMT PU IP

- -RMT 実行(優先度付 SMT 実行)方式

- -IPC 制御方式:スレッド(プログラム)の実行速度制御

- •D-RMTP SiP

- 分散リアルタイム処理用通信リンク (ISO/IEC 24740)

- -Responsive Link IP

- -Responsive Link 搭載チップ (D-RMTP、IO Core)

-4b10b コーデック(エラー訂正機能付きラインコード)

- ・RT-DVFS (リアルタイム動的電圧周波数制御)

- •各種リアルタイムスケジューラ

- •NoC アーキテクチャ

- -NoC コンパイラ

- -NoC の汎用シミュレーション環境

- -RT-NoC アーキテクチャ

- ·3 次元 SiP 実装方式

研究費の大部分を試作(SoC 試作、SiP 試作、評価基板試作、制御基板試作等)に費やすことによって、効率よく上記の研究開発を行い成果を達成することができたと考えている。この際、週に 1回のペースでチーム全体のミーティングを行っていることも功を奏したと思われる。今後は、本CREST をベースとした研究を継続的に続けるとともに、研究成果を広く普及したいと考えている。