戦略的創造研究推進事業 SPPEXA(CREST) 研究領域「ポストペタスケール高性能計算に資するシステムソフトウェア技術の創出」 研究課題「進化的アプローチによる超並列複合システム向け開発環境の創出」

# 研究終了報告書

研究期間 平成28年 1月~平成30年 3月

研究代表者:滝沢 寛之 (東北大学サイバーサイエンスセンター、 教授)

## §1 研究実施の概要

#### (1) 実施概要

現在、HPCシステムの大規模化、複雑化、多様化が進んでおり、HPCアプリケーションが多様なシステムにおいて高い性能を達成する性質である性能可搬性の重要性が高まっている。このような背景から、研究代表者らは JST CREST 採択課題「進化的アプローチによる超並列複合システム向け開発環境の創出」(以下、CREST 課題)でアプリケーションコードをシステム依存の情報とシステム非依存の情報に分離する研究を行い、その実現のための基盤整備を進めてきた。一方、独国シュツットガルト大学 Miriam Mehl 教授らの第 1 期 ExaFSA プロジェクトでは、次世代システムを対象として流体・構造体・音響の連成シミュレーションコードを開発してきた。このため本研究課題(以下、第 2 期 ExaFSA)では、CREST 課題で研究開発されてきたXevolver コード変換フレームワークやそのアプローチの有効性や一般性を、第 1 期 ExaFSA からの研究者にとっても、開発コードの性能可搬性の向上は重要な課題であり、双方にとって有用な共同研究となったことから、研究期間終了後にも継続的に国際共同研究を計画する関係を築くことができた。

本研究課題では、初めに独国ジーゲン大学で開発されている高階不連続 Galerkin ソルバー(high-order discontinuous Galerkin solver)である Ateles の性能解析を行い、性能最適化すべきコードの範囲を特定した。Xevolver フレームワークの事例研究として、主に x86 システムを想定して開発されてきた Ateles を東北大学の NEC SX システム向けに最適化する作業を行った。NEC SX システムでの性能を高めるためには、ループー重化や NEC SX コンパイラ向けの指示行の挿入を複数のループに対して行う必要がある。このため、そのような性能最適化をコード変換として表現し、その変換が性能に与える影響を定量的に評価した。その結果として、コードの保守性を維持しつつ、Intel Xeon プロセッサと比べ約 18%の速度向上を達成できることを示した。これにより、特定のシステム向けの性能最適化をコード変換として表現する手法の有効性を実アプリケーションを用いて確認することができた。また、今後は Xevolver によるコード変換の存在を前提として Ateles のコード開発を行うことが決まり、Xevolver の実アプリケーション開発における有用性を明確に示すことができた。

ただし、Xevolver フレームワークを用いて Ateles のコードを変換するためには、事前に Ateles のコードを手動で修正する必要があることも判明した。この問題への対応方針を Ateles 開発者と議論した結果、将来のアプリケーション開発を考えた場合に Fortran 2003 対応は避けられないという結論に至った。このため、Fortran 2003 対応の Xevolver フレームワークの開発にすでに着手しており、研究期間内の実装完了を目指している。

また、Ateles には3次元高速フーリエ変換(FFT)を用いるバージョンや、高速ルジャンドル変換を用いるバージョンがあり、性能や精度の観点からどの実装が優れているのかは自明ではない。そのため、それぞれのアルゴリズムを専門とする研究者が参加し、それぞれの優位性について議論した。その結果として、Ateles における用途に関して、広く用いられている FFTW よりも高速な FFT を実装することができた。

さらに、ExaFSA で開発されている別のシミュレーションコードである FASTEST の性能解析も行い、x86とは異なるアーキテクチャの例として NEC SX-ACE システム上での性能向上のために効果的な最適化の方針を検討した。その結果として、NEC SX-ACE のようなベクトル型システムで高い性能を達成するためにはカーネルループのベクトル化が必要不可欠であり、コンパイラによるベクトル化に配慮したコード最適化手法はある程度のパターン化できること、およびそれらのパターンを Xevolver を使って簡潔に表現できることを示した。

CREST 課題で構築したコード最適化手法のデータベースである「HPC リファクタリングカタログ」の英語化も行い、ExaFSA プロジェクトに参加している計算科学分野の研究者からのフィードバックを集めつつ、データベースとしての完成度を高める体制を整えることができた。

ExaFSA では、Ateles、FASTEST、および OpenFOAM といった複数のシミュレーションコードを preCICE というフレームワークを使って連携させることを目指している。 それぞれのシミュレ

ーションコードの性能特性が異なることから、それらを効率よく実行できる計算システムも異なる可能性がある。その場合には、それぞれのコードに適したシステムへの最適化を行い、連成シミュレーション全体としての性能向上について議論した。

また、エクサスケール時代に必要となる技術の一つとして耐障害性の向上が挙げられることから、代表的な耐障害性の実現手法であるチェックポイントリスタートについても研究を進めた。その結果として、性能の観点から最適なチェックポイント間隔と消費エネルギの観点から最適なチェックポイント間隔は異なることを明らかにし、その後者を推定するためにシステムのモデル化を行い、それに基づいて最適なチェックポイント間隔を推定する方法を提案した。さらには、そのようなチェックポイントリスタート技術を既存のアプリケーション資産からも利用できるようにするための検討も進めている。

#### (2)顕著な成果

### <優れた基礎研究としての成果>

1. Hiroshi Maeda and Daisuke Takahashi, "Parallel Sparse Matrix-Vector Multiplication Using Accelerators," Proc. 16th International Conference on Computational Science and Its Applications (ICCSA 2016), Part II, Lecture Notes in Computer Science, Vol. 9787, pp. 3--18, Springer International Publishing (2016).

#### 概要:

本論文は、ポストペタ時代に多用される NVIDIA GPU と Intel Xeon Phi での疎行列ベクトル積の効果的な実装方法を議論している。性能評価結果に基づき、Intel Xeon Phi は単一ノードでは比較的高い性能を達成できるものの、複数ノードでの MPI 実行時には通信レイテンシの影響で高性能の達成が難しいことを明らかにした。この成果は NVIDIA Best Paper Award を獲得し、学術的に高く評価されている。

#### <科学技術イノベーションに大きく寄与する成果>

Reiji Suda, Hiroyuki Takizawa, Shoichi Hirasawa, "Xevtgen: Fortran code transformer generator for high performance scientific codes," International Journal on Networking and Computing (special issue on CANDAR'16), Vol. 6, No. 2, pp. 263-289, Aug. 2016.

#### 概要:

変換前後のコードパターンをFortranと指示行を組み合わせて記述することで、相当するコード変換ルールを自動生成する Xevtgen を設計、実装し、その有効性と限界を議論している。実アプリケーションを含むいくつかのコードに対する適用事例から、Xevtgen の有用性を示しており、本研究課題のアプローチの実用性を飛躍的に高めることに成功した。 Xevtgen の利用を前提とした事例研究も数多く行われており、今後のさらなる利用拡大を期待できる。

2. 西尾渉, 小寺紗千子, 平田晃正, 佐々木大輔, 山下毅, 江川隆輔, 小林広明, 曽根秀昭, "太陽光および暑熱同時ばく露に対する熱中症リスク評価シミュレータの開発," 電子情報通信学会論文誌 C,VolJ100-C, No.5, pp.208--216, 2017.

#### 概要:

体温解析に重要な役割を果たす発汗モデルを改良し、妥当性評価を行うとともに、通常のワークステーションでは1ケースあたり16時間を要する解析コードをベクトルスーパーコンピュータ SX-ACE に実装することで飛躍的な高速化を達成した。本研究課題で収集・蓄積してきた最適化技法を高速化支援に有用であることを明確に示した事例であり、その高速化は熱中症リスク評価システムの実現に大きく貢献した。その成果は注目を集め、広く報道された。

# § 2 研究実施体制

- (1)研究チームの体制について

- ① 滝沢グループ

#### 研究参加者

| 氏名             | 所属                     | 役職           | 参加時期   |

|----------------|------------------------|--------------|--------|

| 滝沢 寛之          | 東北大学 サイバーサイエンスセンター     | 教授           | H29.4∼ |

| 江川 隆輔          | 東北大学 サイバーサイ<br>エンスセンター | 准教授          | H29.4∼ |

| 小松 一彦          | 東北大学 サイバーサイエンスセンター     | 助教           | H29.4∼ |

| 南部光江           | 東北大学 サイバーサイエンスセンター     | 産学官連携研究員     | H29.4∼ |

| 伊野 文彦          | 大阪大学 大学院情報科学研究科        | 教授           | H29.4∼ |

| 須田 礼仁          | 東京大学 大学院情報理工学系研究科      | 教授           | H29.4∼ |

| 高橋 大介          | 筑波大学 計算科学研究<br>センター    | 教授           | H29.4∼ |

| 肖 熊            | 東北大学 大学院情報学 研究科        | D3           | H29.4∼ |

| 板倉憲一           | 海洋研究開発機構 地球 情報基盤センター   | グループ<br>リーダー | H29.5∼ |

| 林 康晴           | 日本電気株式会社               | 技術エキスパー<br>ト | H29.9∼ |

| Alfian Amrizal | 東北大学 サイバーサイエンスセンター     | 産学官連携研究員     | H29.9∼ |

#### 研究項目

- ・ 性能最適化情報のアプリケーションコードからの分離

- ・ 大規模シミュレーションの高速化

# (2)国内外の研究者や産業界等との連携によるネットワーク形成の状況について

米国テキサス大学の Ritu Arora ともお互いの成果物の試用を通じた連携を始め、SIAM PP18 では共同提案でミニシンポジウムを開催することを計画している。性能プロファイラの専門家である Sameer Shende や、性能最適化分野でも活躍している Gerhard Wellein ともネットワークを形成し、高性能計算アプリケーション開発における高速化支援の効果的な方法について今後も継続的に協力、意見交換していく予定である。

#### §3 研究実施内容及び成果

3.1 大規模並列カップリングシミュレーションの高速化(東北大学 滝沢グループ)

(1)研究実施内容及び成果

性能改善のために必要な情報をアプリケーションコードから切り離して表現するため、研究代表者らは Xevolver フレームワークを研究開発してきた。本研究課題(第2期 ExaFSA)では、大規模な実アプリケーションに対する Xevolver フレームワークの有用性を実証した。

具体的には、第2期 ExaFSA で開発されている大規模並列カップリングシミュレーションの 主要コードである Ateles と FASTEST の性能を解析し、オリジナルコードの保守性や可読性 を損なうことなく、他のシステムに移植して高性能を実現する事例研究を進めた。また、オリ ジナルコードの修正を最低限に抑えつつ GPU や KNL 等を効率的に利用するための研究 も行った。さらには、エクサスケール時代には耐障害性も必要になることから、効率的なチ エックポイントリスタートについても検討した。

#### Ateles の性能解析と性能最適化

独国ジーゲン大学で開発されている高階不連続 Galerkin ソルバー(high-order discontinuous Galerkin solver)である Ateles の性能解析を行い、性能最適化すべきコード の範囲を特定した。Xevolver フレームワークの事例研究として、主に x86 システムを想定し て開発されてきた Ateles を東北大学の NEC SX システム向けに最適化する作業を行った。 NEC SX システムでの性能を高めるためには、ループー重化や NEC SX コンパイラ向けの 指示行の挿入を複数のループに対して行う必要がある。このため、そのような性能最適化 をコード変換として表現し、その変換が性能に与える影響を定量的に評価した。

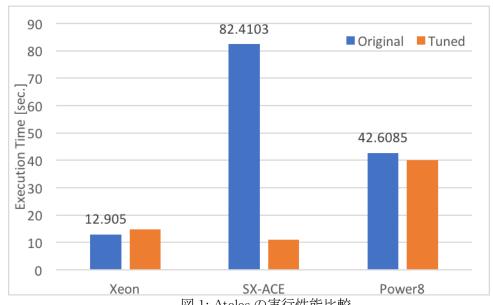

同様のループに対して適用する必要があるループー重化および NEC SX コンパイラ向け の指示行の挿入を変換ルールとして表現し、コード変換で実現した。これにより、熟練のチ ューナーが必要だと判断した4種類18回の性能最適化を1つの汎用的な変換ルールで表 現することができた。これにより、ソースコードの保守性を損なうことなく、また性能最適化の 際の人的ミスを抑えつつ、NEC SX システム向けの性能最適化を実現することができた。図 1に性能最適化の効果を示す。主に x86 システムを想定して開発されてきたため、オリジナ ルコードをそのまま他のシステムで実行するだけでは大幅に実行時間が低下してしまう。 NEC SXシステム向けの性能最適化を行うことで、SXにおいてはオリジナルコードに比べ約 7.5 倍、Xeon E5-2695v2 に比べ約 18%の速度向上を達成できることを確認した。この速度 向上の要因としては、SX-向けベクトル性能最適化により、ベクトル化率が約 71.35%から約 96.72%で大幅に向上したことと、平均ベクトル長77から158と約2倍に向上したことが挙げ られる。また、SX 向けの性能最適化により、Xeon や IBM Power8 においては、オリジナルコ ードに比べ、それぞれ約 14%の速度低下、約 6%の速度向上となった。特定のシステム向け の性能最適化が必ずしも他のシステムには有効でなく、このようなシステム依存の性能最 適化はコードから切り離すことが有効であることが分かる。これらの結果により、性能最適化 をコード変換として表現することで、性能とコード保守性を両立できることを確認できた。

図 1: Ateles の実行性能比較

性能解析の結果、AtelesのカーネルをSX-ACEでこれ以上高速化するのは困難であることがわかっている。今後は、他のプラットフォーム、例えば Knights Landing (KNL)やGraphics Processing Unit (GPU)におけるAtelesのカーネルの性能解析を研究期間内に行い、高速化の可能性について議論する予定である。

Ateles におけるカーネルの一つに離散 Cosine 変換(Discrete Cosine Transform, 以下 DCT)がある。現在の Ateles のソースコードでは FFTW ライブラリの DCT ルーチンが呼ばれているが、KNL などのメニーコア環境においては高い性能を発揮させることは容易ではない。そこで、KNL 等を効率的に利用するアルゴリズムおよび実装に関する研究を行った。DCT は対称性を用いることで実数データに対する高速 Fourier 変換(Fast Fourier Transform, 以下 FFT)に帰着できることが知られている。そこで、まずは KNL における実数 FFT の実装を行った。KNL の AVX-512 命令を用いた SIMD 化を行うと共に、OpenMP による並列化を行った。KNL における性能評価の結果、実装した FFT は FFTW よりも性能が高いことが明らかになった。この研究成果を活用して平成 29 年度末までに FFTW と同様の API を持つ DCT ルーチンの実装を行い、Ateles に組み込んで性能評価を行う予定である。

#### FASTEST の性能解析と性能最適化

独国ダルムシュタット工科大学で開発されている非圧縮流体ソルバーの FASTEST の性能解析と性能最適化を行った。通常の x86 とは異なるアーキテクチャの例として NEC SX-ACEシステムを移植先として考え、SX-ACEでの性能向上のために効果的な最適化の方針を検討した。

FASTEST は1990年代から開発・保守されてきた歴史を持っており、重要カーネルの一部は過去にベクトル型システム向けに最適化されたことがある。いくつかの重要カーネルでは、ifdefとCプリプロセッサのマクロ定義を使って標準版とベクトル版をコンパイル時に切り替えられるようになっている。しかし、その後x86の標準システムを対象とした開発が中心となり、ベクトル版はあまり保守されていない。また、標準版とベクトル版を1つのソースコード内に共存させているため、コードが必要以上に長くなるばかりか可読性も低下していた。

そこで本研究では FASTEST のコード内にあるベクトル版を削除し、その代わりに標準版からベクトル版への変換をユーザ定義のコード変換ルールとして記述する事例研究を行った。標準版とベクトル版の主な違いは、主要ループが一重化されているか否かである。両者の違いをコード変換ルールとして記述するためには、標準的なループー重化の変換ルールに加えて、それぞれのループに合わせて特殊化したルールが必要になる。元のFASTEST のコード内に標準版とベクトル版を持つループは 22 個あり、それらを 10 個のルールとして表現することができた。いくつかのルールは複数のループに対して適用可能である。各ルールが適用されたループ数を表 1 に示す。これらのルールを Xevolver では簡潔に記述することが可能であり、その大半は標準的なループー重化のルールの再利用と軽微なカスタマイズで実現できることが事例研究から明らかになった。その結果から、SX-ACE のようなベクトル型システムで高い性能を達成するためにはカーネルループのベクトル化が必要不可欠であり、コンパイラによるベクトル化に配慮したコード最適化手法はある程度のパターン化できること、およびそれらのパターンを Xevolverを使って簡潔に表現できることを示した。

表 1: 事例研究で定義されたコード変換ルールと適用回数

| name   | calcdp | calcp | celp2 | flxc | vint | flxcoa | sipsol1 | sipsol2 | sipsol4 | celuvw1 |

|--------|--------|-------|-------|------|------|--------|---------|---------|---------|---------|

| # loop | 1      | 5     | 2     | 3    | 1    | 3      | 1       | 1       | 1       | 1       |

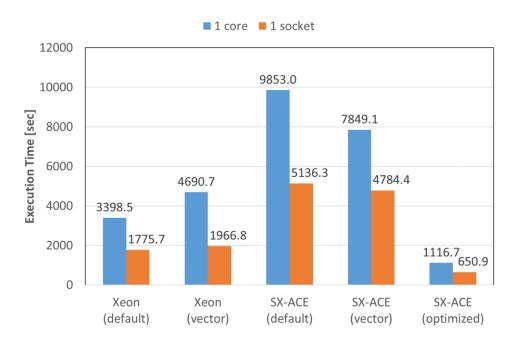

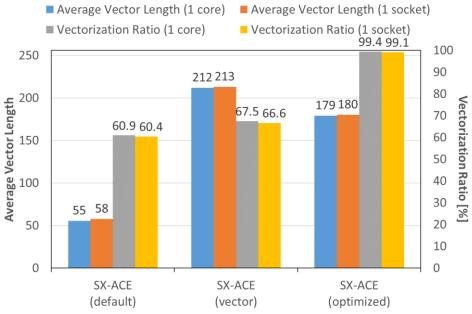

また、FASTESTでは一部のカーネルにしかベクトル版がないために、そのほかのカーネルではベクトル化率が低いことも性能解析の結果から明らかになった。このため、その他のカーネルに関しても、可読性、保守性や標準システムでの性能を低下させない範囲でベクトル化率を高める修正を行った。その結果として、本事例研究で用いたテストケースに対して、SX-ACEプロセッサ(4 コア)は Xeon E5-2695v2 プロセッサ(12 コア)よりも 2 倍以上高い性能を達成することができた。図 2 に性能評価結果を、図 3 に性能最適化によるベクトル化率と平均ベクトル長の変化を示す。これらの結果は、ともに ExaFSA に参加しているダルムシュタット工科大学の研究者からも高く評価されており、今後もアプリケーション開発と特定のシステム向け最適化の記述を分離する共同研究を行うことを計画している。

図 2: FASTEST の実行性能の比較

図 3:最適化による FASTEST のベクトル化率と平均ベクトル長の変化

#### HPC リファクタリングカタログ

CREST 課題で構築したコード最適化手法のデータベースである「HPC リファクタリングカタログ」の英語版の公開も行い、ExaFSAプロジェクトに参加している研究者との連携体制を整備した。また、現在公開している最適化事例を用いた実アプリケーションのコード最適化に関する事例研究にも取り組み、カタログで公開している最適化事例と本事例に関するコード変換規則を用いる事で、次に示す様に少ない労力で速やかなコード最適化が可能なことを明らかにしている。

図 4 はカタログにおいて公開している最適化事例を示している。この最適化ではループ中の変数xがイタレーション毎に変化することからベクトル化が阻害されている。そこで、スカラ変数xを配列x()に置き換えイタレーション毎の値を配列xに格納することでベクトル化を促進している。図 5 左手に示すコードは、熱中症リスクを評価するために開発されたコードのメインルーチンの一つである。本コードは、図 4 に示す事例と 1 重ループ、3重ループの違いはあるものの変数 BCOEFの値がイタレーション毎に変化するためベクトル化がされずに、ベクトル化率は 15.4%に留まっている。そこで、図 4 の事例を参考にスカラ変数BCOEFを三次元配列 BCOEF(I, J, K)に置き換えイタレーション毎の値を格納、読み出すことで依存関係を解消しベクトル化を促進した。このように事例を参考にコード最適化を本コードに適用することで、ベクトル化率は99.1%まで上昇し、約20倍の実行時間短縮を実現している。また、カタログでは図 4 のコード変換規則を提供しており、プログラマはこの変換規則をひな形に、コード変換規則を記述することができる事から、Xevolver を用いたコードの保守性と性能可搬性双方を両立することが出来る。

```

[Before]

[After]

59: integer :: x

77: integer::x(MAX)

78:

60:

61: x = 0

79: x = 0

62: do i=1 MAX

80: do i=1 MAX

if(a(i) < 5000) then

if(a(i) < 5000) then

81:

x = 100

x(i) = 100

82:

65: end if

end if

83:

66: b(i) = a(i) + c(i)*x

84.

b(i) = a(i) + c(i)*x(i)

67: end do

85: end do

```

図4 スカラ変数の配列への置き換えによるベクトル化の促進

```

(Before)

65: DO K=1,MODELZ

67: DO J=1 MODELY

DO I=1,MODELX

68:

111:

IF(UOLD(I,J,K).GE.US(I,J,K))THEN

112:

BCOEF=2**((UOLD(I,J,K)-US(I,J,K))/6)

TEMP_DIFF=UOLD(I,J,K)-US(I,J,K)

113:

114:

TEMP_DIFF=0E0

117:

ENDIF

126:

IF(UOLD(I,J,K).LT.39E0)THEN

127:

128:

FLSE IF(UOLD(I.J.K).LT.44F0)THEN

129:

BCOEF=1E0+0.8E0*(UOLD(I,J,K)-39E0)

130:

132:

BCOEF=1E0+(5E0*0.8E0)

133:

ENDIF

134:

135:

ENDIF

136:

137:

138:

ELSE

139:

BCOEF=1F0

TEMP_DIFF=0E0

141:

U(LJ.K)=UOLD(LJ.K)+(DT*SAR(LJ.K)/CP(LK(LJ.K))&

148:

&+DT*A(LK(I,J,K))*storetemp2(i,j,k)/(ROU(LK(I,J,K))*CP(LK(I,J,K)))&

150:

&-(DT*BCOEF*B(LK(I,J,K))*(UOLD(I,J,K)-henkaTB))/(ROU(LK(I,J,K)) •

```

```

[After]

65: DO K=1,MODELZ

67: DO I=1 MODELY

DO I=1,MODELX

68:

111:

IF(UOLD(I,J,K).GE.US(I,J,K))THEN

112:

BCOEF (I,J,K)=2**((UOLD(I,J,K)-US(I,J,K))/6)

TEMP_DIFF=UOLD(I,J,K)-US(I,J,K)

113:

114:

TEMP_DIFF=0E0

117:

ENDIE

126:

IF(UOLD(I,J,K).LT.39E0)THEN

128:

ELSE IF(UOLD(I.J.K).LT.44E0)THEN

129

BCOEF_(I,J,K)=1E0+0.8E0*(UOLD(I,J,K)-39E0)

130:

133:

BCOEF (I,J,K)=1E0+(5E0*0.8E0)

ENDIF

134:

135:

ENDIE

137:

138:

FLSE

BCOEF (I,J,K)=1E0

139:

TEMP_DIFF=0E0

141:

ENDIF

148:

U(IJ.K)=UOLD(IJ.K)+(DT*SAR(IJ.K)/CP(LK(IJ.K))&

&+DT*A(LK(I,J,K))*storetemp2(i,j,k)/(ROU(LK(I,J,K))*CP(LK(I,J,K)))&

149:

150:

&-(DT*BCOEF_(I,J,K)*B(LK(I,J,K))* •

```

Vector Opertation Ratio: 15.4%Vector Opertation Ratio: 99.1%Ave. Vector Length: 216.5Ave. Vector Length: 196.4Execution Time: 3,208 secExecution Time: 149 sec

図 5 最適化事例の実アプリケーション(熱中症リスク評価シミュレーション)への適用例

今後は、ExaFSA の研究協力者からのフィードバックを集約することで、事例の容易・簡易な集約と蓄積を可能とするユーザインターフェースの検討を推し進めながら、データベースとしての完成度を高めることを予定している。

#### (開発ソフトウェア)

#### 公開予定のもの

Xevolver フレームワーク (Omni コンパイラ版)

- ・ 性能最適化に関する情報をユーザ定義コード変換としてアプリケーションコードから 分離して記述するためのフレームワーク

- ・ 変換前後のコードパターンを記述することにより、コード変換に関する特別な知識がなくてもコード変換ルールを生成できる

- 標準的な x86 Linux システム

- 情報基盤センター等で他人が開発したアプリケーションコードの高速化支援を行っている人たち

- ・ エクサスケール時代にはシステム構成が複雑になり、特に計算ノードのアーキテクチャの多様化が進むことが確定的である。このため、ノード性能を高めるためにアプリケーションコードのさらなる複雑化が予想される。Xevolverフレームワークにより、そのような複雑な最適化情報をアプリケーション開発者からは見えないところに記述することが可能になり、エクサスケール時代に計算科学者と計算機科学者が適切な役割分担をするための基盤としての貢献を期待できる。

# § 4 成果発表等

(1)原著論文発表 (国内(和文)誌 2件、国際(欧文)誌32件)

Kei Ikeda, Fumihiko Ino, and Kenichi Hagihara, "An OpenACC Optimizer for Accelerating Histogram Computation on a GPU," Proceedings of the 24th Euromicro International Conference on Parallel, Distributed and Network-Based Computing (PDP 2016), pp.466-477, Heraklion, Greece, Feb. 17, 2016.

Nobuhiro Miki, Fumihiko Ino, and Kenichi Hagihara, "Applying Temporal Blocking to Out-of-Core Stencil Computation with OpenACC," Proceedings of the Work in Progress Session held in connection with the 24th Euromicro International Conference on Parallel, Distributed and Network-Based Computing (PDP 2016), Heraklion, Greece, 2 pages, Feb. 19, 2016.

Yuta Sakaguchi, Kenryo Kataumi, Hiroshi Matsuoka, Osamu Watanabe, Akihiro Musa, Kazuhiko Komatsu, Ryusuke Egawa, Hiroaki Kobayashi, Satoru Yamamoto, "Performance Optimization of Numerical Turbine for Supercomputer SX-ACE," the 28th International Conference on Parallel Computational Fluid Dynamics, May 9-12, 2016.

Daisuke Takahashi, "Implementation of Multiple-Precision Floating-Point Arithmetic on Intel Xeon Phi Coprocessors," Proc. 16th International Conference on Computational Science and Its Applications (ICCSA 2016), Part II, Lecture Notes in Computer Science, Vol. 9787, pp. 60--70, Springer International Publishing (2016).

Hiroshi Maeda and Daisuke Takahashi, "Parallel Sparse Matrix-Vector Multiplication Using Accelerators," Proc. 16th International Conference on Computational Science and Its Applications (ICCSA 2016), Part II, Lecture Notes in Computer Science, Vol. 9787, pp. 3—18, Springer International Publishing (2016). (NVIDIA Best Paper Award)

Takuya Ikuzawa, Fumihiko Ino, and Kenichi Hagihara, "Reducing Memory Usage by the Lifting-based Discrete Wavelet Transform with a Unified Buffer on a GPU," Journal of Parallel and Distributed Computing, Vol. 93/94, pp. 44--55, (2016-07).

Kazuhiko Komatsu, Ryusuke Egawa, Shoichi Hirasawa, Hiroyuki Takizawa, Ken'ichi Itakura, Hiroaki Kobayashi, "Translation of Large-Scale Simulation Codes for an OpenACC Platform Using the Xevolver Framework," International Journal on Networking and Computing (special issue on CANDAR'16), Vol. 6, No. 2, pp. 167-180, Aug. 2016.

Raghunandan Mathur, Hiroshi Matsuoka, Osamu Watanabe, Akihiro Musa, Ryusuke Egawa and Hiroaki Kobayashi, "A Memory-Efficient Implementation of a Plasmonics Simulation Application on SX-ACE, "International Journal on Networking and Computing (special issue on CANDAR' 16), Vol. 6, No. 2, pp. 243-262, Aug. 2016.

Reiji Suda, Hiroyuki Takizawa, Shoichi Hirasawa, "Xevtgen: Fortran code transformer generator for high performance scientific codes," International Journal on Networking and Computing (special issue on CANDAR'16), Vol. 6, No. 2, pp. 263–289, Aug. 2016.

Daisuke Takahashi, "Automatic Tuning of Computation-Communication Overlap for Parallel

1-D FFT (SP), "19th IEEE International Conference on Computational Science and Engineering (CSE 2016), Paris, France, August 24-26, 2016.

Cui Hang, Shoichi Hirasawa, Hiroyuki Takizawa, Hiroaki Kobayashi, "A Code Selection Mechanism Using Deep Learning," IEEE 10th International Symposium on Embedded Multicore/Many-core Systems-on-Chip (MCSoC-16), Lyon, France, September 21-23, 2016.

Xiong Xiao, Shoichi Hirasawa, Hiroyuki Takizawa, and Hiroaki Kobayashi, "The Importance of Dynamic Load Balancing among OpenMP Thread Teams for Irregular Workloads," The Fourth International Symposium on Computing and Networking, Hiroshima, Japan, November 22–25, pp. 529–535, 2016.

Yasuharu Hayashi, Hiroyuki Takizawa and Hiroaki Kobayashi, "A User-Defined Code Transformation Approach to Overlapping MPI Communication with Computation," The Fourth International Symposium on Computing and Networking, Hiroshima, Japan, November 22–25, pp. 508–514, 2016.

Reiji Suda and Hiroyuki Takizawa, "A software system supporting XML-based source-to-source code transformations on Fortran programs," The Fourth International Symposium on Computing and Networking, Hiroshima, Japan, November 22–25, pp. 522–528, 2016.

Kazuhiko Komatsu, Ryusuke Egawa, Hiroyuki Takizawa, and Hiroaki Kobayashi, "A Directive Generation Approach Using User-defined Rules," The Fourth International Symposium on Computing and Networking, Hiroshima, Japan, November 22–25, pp. 515–521, 2016.

角川拓也, 平澤将一, 滝沢寛之, 小林広明, "ディレクティブに基づくステンシル計算の性能パラメータ自動設定", 情報処理学会論文誌コンピューティングシステム(ACS), Vol.9, No. 4, pp. 25-37, 2016.

Nobuhiro Miki, Fumihiko Ino, and Kenichi Hagihara, "An Extension of OpenACC Directives for Out-of-Core Stencil Computation with Temporal Blocking," In Proceedings of the 3rd Workshop on Accelerator Programming Using Directives (WACCPD 2016), pp. 36-45, Salt Lake City, UT, USA, (2016-11).

Ryotaro Sakai, Fumihiko Ino, and Kenichi Hagihara, "Towards Automating Multi-dimensional Data Decomposition for Executing a Single-GPU Code on a Multi-GPU System," In Proceedings of the 4th International Symposium on Networking and Computing (CANDAR 2016), pp. 408-414, Hiroshima, Japan, (2016-11). Presented at the 4th International Workshop on Computer Systems and Architectures (CSA 2016).

Yuki Takeuchi, Yoshihide Yoshimoto, and Reiji Suda, "Second order accuracy finite difference methods for space-fractional partial differential equations," Journal of Computational and Applied Mathematics, Vol. 320, pp. 101–119, 2017.

Ryusuke Egawa, Kazuhiko Komatsu, Shintaro Momose, Yoko Isobe, Akihiro Musa, Hiroyuki Takizawa, Hiroaki Kobayashi, "Potential of a Modern Vector Supercomputer for Practical Applications – Performance Evaluation of SX-ACE -," Journal of Supercomputing, pp. 1 - 29, 2017, DOI: 10.1007/s11227-017-1993-y.

西尾渉, 小寺紗千子, 平田晃正, 佐々木大輔, 山下毅, 江川隆輔, 小林広明, 曽根秀昭, "太陽光および暑熱同時ばく露に対する熱中症リスク評価シミュレータの開発," 電子情報通信学会論文誌 C,VolJ100-C, No.5, pp.208-216, 2017.

Yuta Sakaguchi, Kenryo Kataumi, Hiroshi Matsuoka, Osamu Watanabe, Akihiro Musa, Kazuhiko, Komatsu, Ryusuke Egawa, Hiroaki Kobayashi, Satoru Yamamoto, "A Case Study of Performance Optimization on Numerical Turbine for Supercomputer SX-ACE", Computers & Fluids, 2017 (to appear).

Xiong Xiao, Shoichi Hirasawa, Hiroyuki Takizawa, Hiroaki Kobayashi, "Toward Dynamic Load Balancing across OpenMP Thread Teams for Irregular Workloads," International Journal on Networking and Computing (special issue on CANDAR'17), Vol. 7, No. 2, pp. 397–404, Jul. 2017.

Kazuhiko Komatsu, Ryusuke Egawa, Hiroyuki Takizawa, and Hiroaki Kobayashi, "A Directive Generation Approach to High Code-Maintainability for Various HPC Systems", International Journal on Networking and Computing (special issue on CANDAR'17), Vol. 7, No. 2, pp. 405-418, Jul. 2017.

Muhammad Alfian Amrizal, Atsuya Uno, Yukinori Sato, Hiroyuki Takizawa, "Energy-Performance Modeling of Speculative Checkpointing for Exascale Systems," IEICE Transactions, Vol. E100-D, No. 12, 2017.

Daisuke Takahashi, "An Implementation of Parallel 1-D Real FFT on Intel Xeon Phi Processors", Proc. 17th International Conference on Computational Science and Its Applications (ICCSA 2017), Part I, Lecture Notes in Computer Science, Vol. 10404, pp. 401-410, Springer International Publishing, 2017.

Nobuhiro Miki, Fumihiko Ino, and Kenichi Hagihara, "PACC: A Directive-based Programming Framework for Out-of-Core Stencil Computation on Accelerators", International Journal of High Performance Computing and Networking, accepted.

Hiroyuki Takizawa, Daichi Sato, Shoichi Hirasawa and Daisuke Takahashi, "A Customizable Auto-Tuning Scenario with User-defined Code Transformations," 32nd IEEE International Parallel & Distributed Processing Symposium Workshops (IPDPSW), The Twelfth International Workshop on Automatic Performance Tuning, 2017.

Muhammad Alfian Amrizal and Hiroyuki Takizawa, "Optimizing Energy Consumption on HPC Systems with a Multi-level Checkpointing Mechanism," The 12th International Conference on Networking, Architecture, and Storage (NAS 2017), 2017.

Ryusuke Egawa, Kazuhiko Komatsu, Yoko Isobe, Toshihiro Kato, Souya Fujimoto, Hiroyuki Takizawa, Akihiro Musa and Hiroaki Kobayashi, "Performance and Power Analysis of SX-ACE using HP-X Benchmark Programs," REV-A Workshop (Re-Emergence of Vector Architectures), 2017.

Hiroyuki Takizawa, Thorsten Reimann, Kazuhiko Komatsu, Takashi Soga, Ryusuke Egawa, Akihiro Musa and Hiroaki Kobayashi, "Vectorization-aware Loop Optimization with User-defined Code Transformations," REV-A Workshop (Re-Emergence of Vector

Architectures), 2017.

Hiroyuki Takizawa, Muhammad Alfian Amrizal, Kazuhiko Komatsu and Ryusuke Egawa, "An Application-Level Incremental Checkpointing Mechanism with Automatic Parameter Tuning," The Fifth International Symposium on Computing and Networking, International Workshop on Legacy HPC Application Migration (LHAM2017), pp. 1-9, 2017.

Ryusuke Egawa, Kazuhiko Komatsu and Hiroyuki Takizawa, "Designing an Open Database of System-aware Code Optimizations," The Fifth International Symposium on Computing and Networking, International Workshop on Legacy HPC Application Migration (LHAM2017), pp. 1-8, 2017.

Mulya Agung, Muhammad Alfian Amrizal, Kazuhiko Komatsu, Ryusuke Egawa, and Hiroyuki Takizawa, "A Memory Congestion-aware MPI Process Placement for Modern NUMA Systems," The 24<sup>th</sup> International Conference on High-Performance Computing, Data, and Analytics (HiPC 2017), pp. 1-9, 2017.

Ryusuke Egawa, Kazuhiko Komatsu, Yoko Isobe, Toshihiro Kato, Souya Fujimoto, Hiroyuki Takizawa, Akihiro Musa and Hiroaki Kobayashi, Performance and Power Analysis of SX-ACE using HP-X Benchmark Programs, Proceedings of IEEE International Conference on Cluster Computing 2017, pp. 693 - 700, Sep. 2017.

Hiroyuki Takizawa, Thorsten Reimann, Kazuhiko Komatsu, Takashi Soga, Ryusuke Egawa, Akihiro Musa and Hiroaki Kobayashi, "Vectorization-aware Loop Optimization with User-defined Code Transformations, Proceedings of IEEE International Conference on Cluster Computing 2017, pp. 685 - 692, Sep. 2017.

#### (2)その他の著作物(総説、書籍など)

Hiroyuki Takizawa, Takeshi Yamada, Shoichi Hirasawa, and Reiji Suda, "A Use Case of a Code Transformation Rule Generator for Data Layout Optimization," Sustained Simulation Performance 2016, Springer-Verlang, (2016).

Shoichi Hirasawa, Hiroyuki Takizawa, and Hiroaki Kobayashi, "An Automatic Performance Tracking System for Large-scale Numerical Applications," Sustained Simulation Performance 2016, Springer-Verlang, (2016).

Kazuhiko Komatsu, Ryusuke Egawa, Hiroyuki Takizawa, and Hiroaki Kobayashi, "Directive Translation for Various HPC Systems Using the Xevolver Framework," Sustained Simulation Performance 2016, Springer-Verlang, (2016).

### (3)国際学会発表及び主要な国内学会発表

① 招待講演 (国内会議 1 件、国際会議 17 件)

\* Kazuhiko Komatsu, "Migration of an HPC Code to an OpenACC Platform Using a Code Translation Framework," 2016 Conference on Advanced Topics and Auto Tuning in High-Performance Scientific Computing (ATAT in HPSC 2016), Feb. 2016.

- \* Daisuke Takahashi, "Automatic Tuning for Parallel FFTs on Intel Xeon Phi Clusters," 2016 Conference on Advanced Topics and Auto Tuning in High-Performance Scientific Computing (ATAT in HPSC 2016), Feb. 2016.

- \* Reiji Suda, "Semi-Automatic Construction of Performance Modeling Software for Autotuning," 2016 Conference on Advanced Topics and Auto Tuning in High-Performance Scientific Computing (ATAT in HPSC 2016), Feb. 2016.

- \* Hiroyuki Takizawa, Takeshi Yamada, Shoichi Hirasawa, and Hiroaki Kobayashi, "Data Layout Optimization Using User-Defined Code Transformations," 2016 Conference on Advanced Topics and Auto Tuning in High-Performance Scientific Computing (ATAT in HPSC 2016), Feb. 2016.

- \* Shoichi Hirasawa, Hiroyuki Takizawa and Hiroaki Kobayashi, "Streamlining Empirical Tuning of Large-scale HPC Applications," 2016 Conference on Advanced Topics and Auto Tuning in High-Performance Scientific Computing (ATAT in HPSC 2016), Feb. 2016.

- \* Daisuke Takahashi, "Implementation of Parallel FFTs on Knights Landing Cluster," SIAM Conference on Computational Science and Engineering (CSE17), February 28, 2017.

- \* Kazuhiko Komatsu, Ryusuke Egawa, Hiroyuki Takizawa, Hiroaki Kobayashi. "User-defined Directive Translation using the Xevovler Framework," 2017 SIAM Conference on Computer Science and Engineering (CSE17), Hilton Atlanta, Altanta, USA, February 27 March 3, 2017.

- \* Daisuke Takahashi, "Automatic Tuning for Parallel FFTs on Cluster of Intel Xeon Phi Processors," 2017 Conference on Advanced Topics and Auto Tuning in High-Performance Scientific Computing (ATAT in HPSC 2017), March 11, 2017.

- \* Kazuhiko Komatsu, "Directive Translation Approach in Keeping a Code Clean," 2017 Conference on Advanced Topics and Auto Tuning in High-Performance Scientific Computing (ATAT in HPSC 2017), March 11, 2017.

- \*Ryusuke Egawa, "An HPC Refactoring Catalog Accumulating Know-Hows of Sytem Specific Optimization and its Practical Usage," 2017 Conference on Advanced Topics and Auto Tuning in High-Performance Scientific Computing (ATAT in HPSC 2017), March 12, 2017.

- \*Reiji Suda, "Generation of Math Library for Multi-Parameter Autotuning," 2017 Conference on Advanced Topics and Auto Tuning in High-Performance Scientific Computing (ATAT in HPSC 2017), March 12, 2017.

- \* Hiroyuki Takizawa, "Combining Autotuning and Code Transformations," 2017 Conference on Advanced Topics and Auto Tuning in High-Performance Scientific Computing (ATAT in HPSC 2017), March 12, 2017.

- \*Hiroyuki Takizawa, Hang Cui and Shoichi Hirasawa, "Performance Tuning

with Machine Learning, "25th Workshop on Sustained Simulation Performance, Sendai, March 13, 2017.

滝沢寛之, "Xevolver プロジェクト: 計算科学と計算機科学をつなぐ架け橋を目指して," 平成 28 年度高速化ワークショップ, March 24, 2017.

Hiroyuki Takizawa, "Performance Engineering with User-defined Code Transformations," Joint Workshop on High-Performance Computing with NSCC-Wuxi and Tohoku University, Wuxi, China, September 21, 2017.

\*Hiroyuki Takizawa, Reiji Suda, Daisuke Takahashi, Ryusuke Egawa, and Fumihiko Ino, "Expressing performance—awareness as user—defined code transformations," International Symposium on Post Petascale System Software, Tokyo, Japan, December 12, 2017.

\*Hiroyuki Takizawa, "A User-defined Code Transformation Approach to Separation of Performance Concerns," First Workshop on Software Challenges to Exascale Computing, Jaipur, India, December 17, 2017.

Kazuhiko Komatsu, "Performance Analysis and Tuning of ExaFSA Codes," SIAM Conference on Prallel Processing for Scientific Computing 18, MS4, March 7, 2018.

Ryusuke Egawa, "HPC Benchmarking; Perspective from Power and Sustained Performance," SIAM Conference on Prallel Processing for Scientific Computing 18, MS101, March 10, 2018.

Hiroyuki Takizawa, "User-De ned Code Transformation for Separation of Performance-Awareness from Application Codes," SIAM Conference on Prallel Processing for Scientific Computing 18, March 10, 2018.

#### ② 口頭発表 (国内会議 17 件、国際会議 8 件)

石田 翔太郎, 須田 礼仁, "丸め関数を用いて浮動小数点数へと離散化された実数一様乱数", 情報処理学会第 153 回ハイパフォーマンスコンピューティング研究発表会, 3 月, 2016 年.

熊谷洋佑, 野地優希, 藤井昭宏, 田中輝雄, 須田礼仁, "通信削減 Jacobi 法を前処理とした共役勾配法の性能評価", 情報処理学会第 153 回ハイパフォーマンスコンピューティング研究発表会, 3 月, 2016 年.

Hiroyuki Takizawa, Takeshi Yamada, Takuya Tsunogawa, Shoichi Hirasawa, and Hiroaki Kobayashi, "Performance Engineering of HPC Applications Based on Pattern Matching," The 23rd Workshop on Sustained Simulation Performance, Mar. 16-17, 2016.

Shoichi Hirasawa, Hiroyuki Takizawa, and Hiroaki Kobayashi, "A Correctness Verification Framework for Empirically Tuning Large-scale HPC Applications,"

The 23rd Workshop on Sustained Simulation Performance, Mar. 16-17, 2016.

五味歩武,高橋大介, "最適化手法を自動化する Xevolver フレームワーク用定義ファイルの実装",情報処理学会研究報告,2016-HPC-155,6 pages,8月,2016.

酒井亮太郎,伊野文彦,萩原兼一, "単一 GPU コードをマルチ GPU 環境で実行するための多次元データ分割手法の検討,"情報処理学会研究報告,2016-HPC-155,(2016-08).7 pages.

須田礼仁, "一般化菱形行列冪カーネルのための領域分割アルゴリズム", 情報処理学会研究報告, 2016-HPC-155, 9 pages, 8月, 2016.

三木脩弘,伊野文彦,萩原兼一,"アウトオブコア・ステンシル計算に対する自動 テンポラルブロッキングのためのアクセラレータ向けディレクティブ",情報処理学会研究報告,2016-HPC-155,7 pages,8月,2016.

須田礼仁, "複合的自動チューニングのための数理とソフトウェア", 計算工学講演会論文集, Vol. 21, F-1-4, 2016.

川原畑勇希,平澤将一,滝沢寛之,小林広明,"機械学習を用いたコード変換に関する研究",平成28年度電気関係学会東北支部連合大会,8月30日-31日,2016.

Reiji Suda, "Diamond Tiling Extended to General Sparse Matrix Powers Kernel", First International Workshop on Deepening Performance Models for Automatic Tuning (DPMAT), Sep. 7th, 2016, Nagoya University.

Hiroyuki Takizawa, "Autotuning meets Code Transformations - A case study of Xevolver framework --," The 24th Workshop on Sustained Simulation Performance, Stuttgart, December 6, 2016.

Ryusuke Egawa, Yoko Isobe, Soya Fujimoto, Power and Performance Analysis of SX-ACE, The 24th Workshop on Sustained Simulation Performance, Stuttgart, December 6, 2016.

Kazuhiko Komatsu, "A Directive Generation Using A Code Translation Framework," The 24th Workshop on Sustained Simulation Performance, Stuttgart, December 6, 2016.

山下毅,山崎国人,江川隆輔,吉岡匠哉,土浦宏紀,小林広明,曽根秀昭,"『2 バンドモデルに対する揺らぎ交換近似』コードの SX-ACE 向け最適化,"大学 ICT 推 進協議会年次大会 HPC テクノロジーセッション,2016 年 12 月 14 日.

滝沢寛之, 須田礼仁, 高橋大介, 江川隆輔, "Xevolver プロジェクトの概要," ポストペタワークショップ, 12月15日, 2016.

Hirokazu Honda, Yoshinori Tamada, Reiji Suda, "Efficient Parallel Algorithm for Optimal DAG Structure Search on Parallel Computer with Torus Network", Proc. ICA3PP 2016: Algorithms and Architectures for Parallel Processing, Dec. 14-16, 2016, Granada, Spain, LNCS 10048, pp. 483-502,

DOI:10.1007/978-3-319-49583-5\_37, Dec. 2016

Hiroyuki Takizawa, "Performance Tuning with Machine Learning," The 25th Workshop on Sustained Simulation Performance, Sendai, March 13, 2017.

山本堅太郎、松本正晴、須田礼仁、「遺伝的アルゴリズムに基づく疎行列解法のパラメタに関するオンライン自動チューニング」(Online Autotuning of Parameters of Genetic Algorithm-based Sparse Linear Solver), 情報処理学会 第159回 HPC 研究会、April 17, 2017, 東京大学柏の葉キャンパス.

須田礼仁、「複合的自動チューニングのための数理ライブラリの構築」、計算工学講演会論文集 vol. 22, May 31st, 2017, 大宮市 ソニックシティ.

高橋大介, "Xeon Phi クラスタ上の並列 FFT における通信隠蔽の自動チューニング", 計算工学講演会論文集, Vol. 22, C-01-3, 2017.

Ryusuke Egawa, Masayuki Sato, Ryoma Saito, Hiroaki Kobayashi, A Multiple-layer Bypass Mechanism for Energy Efficient Computing, In 26th Workshop on Sustained Simulation Performance, Stuttgart, Germany, Oct. 2017.

Kazuhiko Komatsu, Performance tuning of Ateles using Xevolver, In 26th Workshop on Sustained Simulation Performance, Stuttgart, Germany, Oct. 2017.

Ryusuke Egawa, "Job Run-time Estimation toward Energy-aware System Operation," In 27th Workshop on Sustained Simulation Performance, Sedai, Japan, Mar. 2018.

Hiroyuki Takizawa, "Towards prediction of effective optimizations in performance engineering," In 27th Workshop on Sustained Simulation Performance, Sedai, Japan, Mar. 2018.

③ ポスター発表 (国内会議 1件、国際会議 5件) 小林英敏,平澤将一,滝沢寛之,小林広明,"プロファイラと連携する自動性能追 跡システム",2016年ハイパフォーマンスコンピューティングと計算科学シンポジ ウム(HPCS2016),2016.(ポスター)

Hiroyuki Takizawa, Daichi Sato, Shoichi Hirasawa, and Hiroaki Kobayashi, "Making a Legacy Code Auto-tunable without Messing It Up," ACM/IEEE Supercomputing Conference 2016 (SC16), 2016. (poster, abstract review)

Keiichiro Fukazawa, Ryusuke Egawa, Yuko Isobe and Ikuo Miyoshi, "Performance Evaluation of MHD Simulation Code on SX-ACE and FX100," Poster presentation at International Symposium on High-Performance Parallel and Distributed Computing (HPDC 2016), Kyoto Japan, June 2016. (abstract review)

Florian Lindner, Miriam Mehl, Thorsten Reimann, Sabine Roller, Dörte C. Sternel, Hiroyuki Takizawa, and Sander van Zujilen, "ExaFSA - Exascale Simulation of Fluid-Structure-Acoustics Interactions," Poster presentation at ISC High Performance 2017, Frankfurt, Germany, June 18-22, 2017.

Zhen Wang, Ryusuke Egawa, Reiji Suda, and Hiroyuki Takizawa, "Auto-tuning of Hyperparameters of Machine Learning Models," accepted for poster presentation at HPC Asia 2018, Tokyo, January 29-30, 2018.

Pei Li, Mulya Agung, Muhammad Alfian Amrizal, Ryusuke Egawa, and Hiroyuki Takizawa, "Thermal-aware Dynamic Checkpoint Interval Tuning for High Performance Computing," accepted for poster presentation at HPC Asia 2018, Tokyo, January 29-30, 2018.

#### (4)知財出願

- ①国内出願(0件)

- ②海外出願(0件)

- ③その他の知的財産権

#### (5)受賞・報道等

- ①受賞

- \* NVIDIA Best Paper Award, Hiroshi Maeda and Daisuke Takahashi, ICCSA2016 Program Committee, Beijing, China, 2016/7/6

#### ②マスコミ(新聞·TV等)報道

- 2017年4月15日 河北新報(11面) 研究室探訪で取り上げられました. 「高速・高精度で模擬実験 東北大学サイバーサイエンスセンター 准教授 江川隆輔」 (概要)計算科学者と計算機科学者の協業によるシミュレーションコードの高速化と,これらの成果を社会に還元する取り組みが取り上げられた.

- 2017 年 4 月 25 日 プレスリリース「パーソナルデータに基づき熱中症対策を提示するコンテンツ「熱中症セルフチェック」がスタート」 (概要)名古屋工業大学平田教授が開発した「熱中症リスク評価シミュレーション」コードに江川の研究グループが高速化を施し、実時間の熱中症リスク評価を可能にした。この技術に基づき、日本気象協会が熱中症発症を抑えるサービスの提供を開始した。

#### ③その他

- (6)成果展開事例

- ①実用化に向けての展開

特になし

# ②社会還元的な展開活動

本研究成果をインターネット(http://xev.sc.cc.tohoku.ac.jp/)で公開し、一般に情報提供している。 SPPEXA による支援により主催した国際ワークショップでの関係等が元となり、大阪大学の伊野研究室は欧州の主要な研究拠点の一つである Barcelona Supercomputing Center との研究交流を開始し、2018年度より学生の海外インターンシップを予定している。

# § 5 研究期間中の活動

# 5. 1 主なワークショップ、シンポジウム、アウトリーチ等の活動

| 年月日       | 名称                     | 場所     | 参加人数 | 概要               |

|-----------|------------------------|--------|------|------------------|

| 2016 年 11 | 0 1 11                 |        | 40 人 | 国際会議             |

| 月 23 日    | Migration 2016         | 文化ホール  |      |                  |

| 2016年12月  | 第8回 自動チューニン            | 東京大学   | 32 人 | 他の科研費等と合同で成      |

| 26 日      | グ技術の現状と応用に             |        |      | 果を発信             |

|           | 関するシンポジウム              |        |      |                  |

| 2017年3月   | ExaFSA 研究者滞在           | 東北大学   | 1名   | ExaFSA 研究者を招聘し研  |

| 5-15 日    |                        |        |      | 究打合せ             |

| 2017年3月   | ExaFSA 開発ミーティン         | 東北大学   | 4名   | ExaFSA シミュレーション打 |

| 15 目      | グ                      |        |      | 合せ               |

| 2017年3月   | SPPEXA Annual Meeting  | ドイツ ミュ | 50 人 | SPPEXA 全体研究発表会   |

| 20 日      | 2017                   | ンヘン    |      |                  |

| 2017 年 11 | Legacy HPC Application | 青森県観光  | 40 人 | 国際会議             |

| 月 20 日    | Migration 2016         | 物産館アス  |      |                  |

|           |                        | パム     |      |                  |