# 研究終了報告書

「信頼性を持つ量子コンピュータ・アーキテクチャの研究」

研究期間: 2020年10 月~2024年3月

研究者: 谷本 輝夫

#### 1. 研究のねらい

量子ゲート方式コンピュータは量子ビットによる超並列計算が可能であり、ポストムーア時代における計算基盤の有力な候補の一つである。しかしながら、量子コンピュータを計算基盤として利用するためのシステム設計や、性能および信頼性に関する検討はあまり行われておらず、計算基盤として成熟していくためにはシステム構築の観点で統合的に検討可能なフレームワークが不可欠である。

本研究では信頼性を有する量子コンピュータ・アーキテクチャの開発を目的とする。そのため、システムレベルで量子コンピュータ設計を検討できるフレームワークを構築する。本研究で対象とするのはまずは NISQ (Noisy Intermediate-Scale Quantum) コンピュータ規模とし、現実的な量子ビットデバイスのモデル化とシミュレーション環境を基盤に、VQE (Variational Quantum Eigensolver)や QAOA (Quantum Approximate Optimization Algorithm)などの NISQ 向け古典・量子ハイブリッドアルゴリズムに対してアルゴリズムの特徴と、極低温環境を含む実装を考慮したシステム・アーキテクチャの確立と、トレードオフ探索を行う。フレームワークの主要コンポーネントについては、既存技術の活用や各専門家との共同で進める。

また、NISQ コンピュータに対する取り組みと並行して、誤り耐性量子コンピュータ(FTQC)のシステム設計、また高信頼化に取り組む。FTQC は誤り訂正により、量子ビットにおけるノイズに耐性を持つことができる。FTQC の実現には、より多くの物理ビットを収容可能なシステム設計による大規模化や、誤り訂正に必要な量子ビット数の削減が必要である。極低温環境を考慮したシステム・レベル検討及び現実的な状況を想定した適応的な制御によりFTQCの大規模化、省物理量子ビット化を目指す。

本研究は、計算基盤としての量子コンピュータ・システムの構築に直接的に貢献することが期待できる。また、本研究で構築する、現実的な量子ビットの振る舞いを反映可能なシミュレーション基盤は量子ビットデバイス研究者にとってはハードウェアパラメータのソフトウェアへの影響調査に、量子アルゴリズム研究者にとっては現実的な実行結果の検証に用いることができる。そのため、要素技術研究にも有用なフレームワークの構築が期待できる。近未来に実現の見込みのある NISQ コンピュータ、長期的展望を見据えた FTQC それぞれに対しシステム設計の観点でアプローチすることにより、量子コンピュータの計算基盤としての成熟に資する取り組みを行う。

### 2. 研究成果

#### (1)概要

本課題は、当初は Noisy-Intermediate Scale Quantum (NISQ) コンピュータを対象とし、デバイスからアプリケーションまでを考慮したシステム・レベル最適化を行うことを予定していた。しか

しながら、さきがけ研究期間中に誤り耐性量子計算機(Fault-tolerant Quantum Computer; FTQC)関連の研究が大きく進展したことや、本さきがけ領域から生じた共同研究を通して FTQC にも注目し、そのシステム・アーキテクチャ検討に取り組んだ。

NISQ コンピュータを対象とした取り組みとしては、Quantum Approximate Optimization Algorithm (QAOA) を対象としたシステム・アーキテクチャを提案し、IEEE Computer Architecture Letters で発表した。これは、計算結果が確率的に出力される量子コンピュータの特徴と、それを利用した古典量子ハイブリッドアルゴリズムである QAOA の構造を考慮し、超伝導量子コンピュータを大規模化する上での課題である、冷凍機内外の配線を削減するためのシステム・アーキテクチャの工夫を提案し、その効果を定量的に評価したものである。より具体的には、超伝導量子プロセッサを収容する希釈冷凍機の 4 Kelvin ステージに量子古典インタフェースが設置されている前提で、追加の古典デジタル回路で構成する二進カウンタを導入し、NISQ 計算におけるショットごとの出力(ビットストリング)から、古典最適化処理に必要な情報のみを取り出してカウンタで集計する。これにより、ビットストリングをすべて冷凍機外に出力する場合に比べて、搭載するビット数に対し指数的な必要バンド幅削減が可能であることを示した。特定のアルゴリズムに焦点を当てて具体的なシステム・アーキテクチャを提案したという観点で、世界初の試みである。

FTQC に関しては、具現化に向けてその全体像を描く取り組みと、現実的に生じる可能性のある問題の解決に取り組んだ。前者については、それまで FTQC の構成要素に対する各論が進められていた中、FTQC 全体に含まれる古典情報処理を含む構造を明らかにし、物理ビット数を大規模化する上で障害となる要素を洗い出し、解決することを試みた。この取り組みは、ソウル国立大学(韓国)、名古屋大学との共同研究であり、コンピュータ・アーキテクチャ分野のトップレベル会議である International Symposium on Computer Architecture (ISCA) に採択され発表した。後者については、超伝導量子プロセッサに宇宙線が当たった場合の影響が、古典デジタル回路に用いられる CMOS 回路と比較して深刻であることに着目し、誤り訂正符号におけるエラー推定の枠組みを発展させることでその影響を緩和することに取り組んだ。この取り組みは、本さきがけ領域から生まれた NTT、東京大学との共同研究であり、コンピュータ・アーキテクチャ分野のトップレベル会議である International Symposium on Microarchitecture (MICRO) に採択され発表した。

## (2)詳細

# 2(2)-1. Noisy-Intermediate Scale Quantum (NISQ) コンピュータを対象とした取り組み

NISQ コンピュータは、FTQC よりも早期の実現が見込まれており、有用なアプリケーションが NISQ コンピュータ上で実行可能になることは重要である。そこで、本課題では、アプリケーション (アルゴリズム) の特徴理解に基づくシステム・アーキテクチャの確立を目指して研究に取り組んだ。まずは、組合せ最適化問題の近似解法である Quantum Approximate Optimization Algorithm (QAOA) に着目し、その潜在的な課題を解決するシステム・アーキテクチャ上の工夫を提案した。図 1 にその全体像を示す。左側は前提とするシステムとアルゴリズムの構造、右側は提案 (Counter-based architecture の追加) とその効果 (Result read-out に要する通信バン

ド幅削減)を記載している。 QAOA で **CMOS CMOS** は、古典パラ Judge convergence 300 K Device **Device** メータを更新 111 1111111 Ш するために、 Bandwidth 1 (1) Instruction 2 Result Reduction transfer read-out コストハミルト 4 K nstruction Convert to ニアンの期 assical bits OC issue Counter-based Interface 待値計算を

その際に量 子プロセッサ

必要とする。

20 mK

**QPU**

図 1温度ステージ間バンド幅削減アーキテクチャの全体像

**Gate operation**

and measurement

を用いてサンプルを多数取得して平均を計算する。この時、どの計算をどの温度ステージで行 うかによって、温度ステージ間に生じる通信量が決まる。温度ステージ間の通信は異なる熱雑 音環境の観点から信号の増幅・減衰が必要であったり、より高音のステージから配線を通じて 熱流入が生じたりすることから、可能な限り避けるのが望ましい。そこで、本研究では、どの計 算をどの温度ステージで行うべきか検討した上で、温度ステージ間の要求通信バンド幅を削 減する手法を考案した。コスト値の計算や古典パラメータの計算には実数制度の計算が必要 となるため室温で行うことが適当であると考え、また、量子古典インタフェースが4 Kelvinステー ジに設置されることを装置して、4 Kelvin ステージで計算に必要な情報の圧縮を考えた。

OAOA で計算する期待値は、1ショットから得られるビットストリングごとにコスト値を評価しなく ても、1 つまたは 2 つの量子ビットの観測結果から得られる値が 1 になった回数を計数し、所定 のショット数の実行後、カウンタ値を使った実数計算で置き換えることができる。このことに着目 して、4 Kelvin ステージに小さな 2 進力ウンタを多数  $(O(n^2), n$ は量子ビット数) 搭載すること で指数的な通信量削減を実現した。カウンタ導入と通信バンド幅の関係を考えるためには、カ ウンタ値の読み出し方法について考える必要がある。本提案では、導入した小さなカウンタが

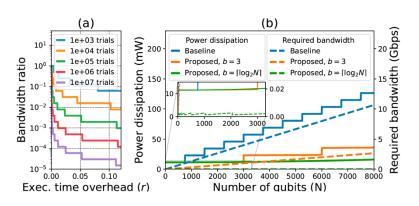

タイミングで定期的 に MSB を読み出し てクリアするとした。 提案アーキテクチャ の評価結果を図 2 に示す。(a)はカウン タ導入の実行時間へ の影響を評価したも のである。精度を変 えずに期待値を計算

溢れる可能性がある

図 2 極低温カウンタ・アーキテクチャの評価

するためには、実行後にカウンタに残った値を読み出す必要がある。これに要する時間は隠 蔽できないため、その分実行時間が長くなる。そのため、許容する実行時間オーバヘッド(横 軸)と必要バンド幅(縦軸)はトレードオフの関係になる。 全体のショット数に応じて相対的オー

architecture

**QPU**

バヘッドは変わるため、ショット数(trials)を変えて評価を行った。(b)は量子ビット数(横軸)に対して、必要バンド幅(右縦軸)と熱散逸(左縦軸)の変化を示している。カウンタは、Single-Flux Quantum (SFQ) デバイスを用いたデジタル回路を用いて構成するものとした。ベースライン (青)に対して、現実的パラメータ(橙)と理想的パラメータ(緑)について要求バンド幅と熱散逸を削減可能であることを示している。本評価では、750 量子ビット以上ではカウンタを導入する方が良いという結果が得られた。また、QAOAのみならず、VQEを対象としたアーキテクチャについても検討を行った。

当初計画からの変更点として、ショット数を必要十分な回数に限定する手法の確立を掲げていたが、一般的な議論と特定の問題インスタンスに限定される経験的な議論の中間的な落とし所を見出すことができず未達となった。また、理化学研究所超伝導量子コンピュータを用いた量子コンピュータ・シミュレータの検証はマシンタイムの関係でIBM-Qを用いた検証を行った。

#### 2(2)-2. Fault-tolerant Quantum Computer (FTQC) を対象とした取り組み

量子計算による加速の恩恵をより多く受けるには、誤り耐性のある量子コンピュータの実現が必要である。そのためには、50万程度の物理量子ビットが必要であると試算されている。これは現在達成されている規模と大きなギャップがあり、FTQCによる量子加速に向けて解決すべき課題は多岐にわたる。そのため、どの要素がどの程度潜在的な課題を抱えているかを早期に特定することを

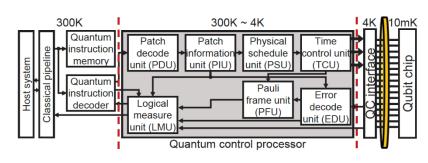

目的として、FTQC のシステム・レベル・分析と、大規模 化に向けた提案を 行った。本取り組 みで前提とする FTQC の構成を図 3 に示す。中でも、

図 3 FTQC の全体構成

本取り組みでは、古典情報処理を担う Quantum control processor (QCP) を対象に、スケーラビリティの評価と改善について検討した。極低温環境を要する超伝導量子コンピュータでは QCP は室温から 4 Kelvin に跨って構成されると想定し、大規模化を制限しうる要素として温度ステージ間通信バンド幅、極低温ステージ熱散逸、エラー推定処理遅延を抽出した。これらについて、各処理の適切な温度ステージへの配置、SFQ 回路の活用、エラー推定器の改善などを組み合わせて、単一希釈冷凍機で 10 万以上の物理量子ビットを収容できる可能性を示した。ただし、この試算では量子古典インタフェースの熱散逸は考慮しない。

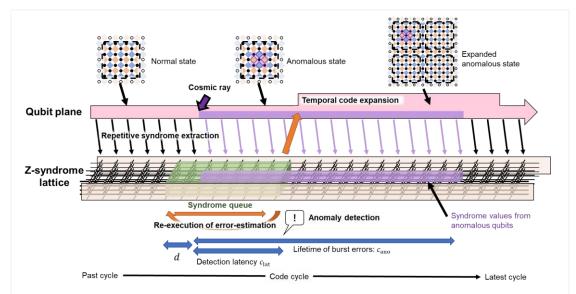

現実的な状況における FTQC についての検討も重要である。量子ビットに宇宙線が当たると、時空間的な広がりのある物理エラーレートの高まりが生じ、従来の誤り訂正符号の前提が崩れる問題があった。そこで、統計処理により宇宙線が当たったことを検出し、符号サイズ拡張と、エラー推定の再計算を行うことで論理エラーレートを向上できることを示した(図 4)。

図 4 宇宙線によるマルチビットバーストエラーに耐性のある FTQC の概要

本取り組みの効果をコンピュータの観点で評価した のが図 5 である。 論理エラーレートの改善が量子コ ンピュータにどのように寄与するかに着目した評価を 行っている。(a)では、物理量子ビット数が量子チップ 面積と量子ビットの実装密度の積で与えられるとした 場合に、本提案によって宇宙線が当たっていない期 間のコードサイズを小さくできる効果が非常に大きい ことを示している。(b)では、表面符号状での論理演 算にかかるサイクル数がコードサイズに依存すること や、格子手術に必要な物理ビットを考慮して命令ス ループットを評価したものである。

これらの取り組みを通して、信頼性を持つ量子コン ピュータの実現に一歩近づくことができた。

図 5 コンピュータとしての評価

#### 3. 今後の展開

量子コンピュータ関連技術の進展は著しく、本課題の提案時からこれまでの間に研究開発の 潮流が大きく変化したと考えている。 当初は NISQ コンピュータを対象とした研究を実施する計画 であったが、本領域での議論や共同研究を通してFTQCを含めて取り組むことができた。今後も、 直近で必要となるNISQコンピュータを対象としたシステム・アーキテクチャの改善と、FTOCによる 量子加速の早期実現に向けたシステム・アーキテクチャの確立に向けて邁進したいと考えている。 特に、FTQC においては、表面符号や、より符号効率の良い符号を高精度かつ高電力効率にエ ラー推定するエラー・デコード・システムや、演算と記憶というコンピュータの根幹をなす機能をより 低コスト、すなわちより簡単に実現するためのシステム構成などに対して、本課題で実施した内容

#### 4. 自己評価

当初計画からの変更はあったものの、より長期的かつ本質的に挑戦すべき FTQC の理解を進め、研究を展開することができたことは想像を超えたものであった。かねてから目標としていた、トップレベル会議である ISCA、MICRO に論文を発表できたことは個人的な業績としてだけではなく、国内のコンピュータ・アーキテクチャ分野を見ても顕著な業績であり、当該分野における量子コンピュータ・アーキテクチャ研究の素地を作ることができたと自負している。実際、本課題の取り組みの中で、東京大学でコンピュータ・アーキテクチャに取り組んでいる中村宏教授に量子コンピュータ・アーキテクチャ研究に参入いただき、IEEE Computer Architecture Letters に採録されるなど、計算機工学分野に対して量子計算研究を広めることができたと言える。

また、海外研究者とのネットワークを確立するという観点でも、本課題での取り組みが果たした役割は非常に大きいと感じている。Prof. Fred Chong(米国・シカゴ大学)、Prof. Gokul Ravi(米国・ミシガン大学)、Prof. Martin Shultz(ドイツ・ミュンヘン工科大学)、Prof. Jangwoo Kim(韓国・ソウル国立大学)などとは特に議論を深めながら研究に取り組むことができた。

本課題を進めるにあたっては、領域会議やサイトビジットでいただくコメントにより、機動的に研究を進めることができた。さらに、藤井アドバイザーには個別にお時間をいただき議論をさせていただくなど大変貴重なご指導をいただいた。さきがけ領域の中で研究できたことは非常に有意義であったと感じている。

予算執行にあたっては、主に、シミュレーションや回路設計に使用する計算資源、シミュレータ 実装等をするテクニカルスタッフ、成果発表及びネットワーキングのための旅費に当てさせていた だいた。個人型研究としては十分な予算を配分いただき、成果創出のために有効に執行できたと 考えている。

#### 5. 主な研究成果リスト

(1)代表的な論文(原著論文)発表

研究期間累積件数: 8件

1. Yosuke Ueno, Yuna Tomida, Teruo Tanimoto, Masamitsu Tanaka, Yutaka Tabuchi, Koji Inoue, Hiroshi Nakamura, "Inter-temperature Bandwidth Reduction in Cryogenic QAOA Machines," IEEE Computer Architecture Letters, Vol. 23, No. 1, Jan-June 2023.

The bandwidth limit between cryogenic and room temperature environments is a critical bottleneck in superconducting noisy intermediate-scale quantum computers. This paper presents the first trial of algorithm-aware system-level optimization to solve this issue by targeting the quantum approximate optimization algorithm. Our counter-based cryogenic architecture using single-flux quantum logic shows exponential bandwidth reduction and decreases heat inflow and peripheral power consumption of inter-temperature cables, which contributes to the scalability of superconducting quantum computers.

2. Ilkwon Byun, Junpyo Kim, Dongmoon Min, Ikki Nagaoka, Kosuke Fukumitsu, Iori Ishikawa, Teruo Tanimoto, Masamitsu Tanaka, Koji Inoue, and Jangwoo Kim, "XQsim: Modeling Cross-Technology Control Processors for 10+K Qubit Quantum Computers," In Proceedings of ACM/IEEE International Symposium on Computer Architecture (ISCA '22), 2022, pp. 366-382.

10+K qubit quantum computer is essential to achieve a true sense of quantum supremacy. With the recent effort towards the large-scale quantum computer, architects have revealed various scalability issues including the constraints in a quantum control processor, which should be holistically analyzed to design a future scalable control processor. However, it has been impossible to identify and resolve the processor's scalability bottleneck due to the absence of a reliable tool to explore an extensive design space including microarchitecture, device technology, and operating temperature. In this paper, we present XQsim, an open-source cross-technology quantum control processor simulator. XQsim can accurately analyze the target control processors' scalability bottlenecks for various device technology and operating temperature candidates. To achieve the goal, we first fully implement a convincing control processor microarchitecture for the Fault-tolerant Quantum Computer (FTQC) systems. Next, on top of the microarchitecture, we develop an architecture-level control processor simulator (XQsim) and thoroughly validate it with post-layout analysis, timing-accurate RTL simulation, and noisy quantum simulation. Lastly, driven by XQsim, we provide the future directions to design a 10+K qubit quantum control processor with several design guidelines and architecture optimizations. Our case study shows that the final control processor architecture can successfully support ~59K qubits with our operating temperature and technology choices.

3. Yasunari Suzuki, Takanori Sugiyama, Tomochika Arai, Wang Liao, Koji Inoue, and Teruo Tanimoto, "Q3DE: A fault-tolerant quantum computer architecture for multi-bit burst errors by cosmic rays," In Proceedings of the 55th IEEE/ACM International Symposium on Microarchitecture (MICRO-55), 2022, pp. 1110-1125.

Demonstrating small error rates by integrating quantum error correction (QEC) into an architecture of quantum computing is the next milestone towards scalable fault tolerant quantum computing (FTQC). Encoding logical qubits with superconducting qubits and surface codes is considered a promising candidate for FTQC architectures. In this paper, we propose an FTQC architecture, which we call Q3DE, that enhances the tolerance to multi-bit burst errors (MBBEs) by cosmic rays with moderate changes and overhead. There are three core components in Q3DE: in-situ anomaly DEtection, dynamic code DEformation, and optimized error DEcoding. In this architecture, MBBEs are detected only from syndrome values for error correction. The effect of MBBEs is immediately mitigated by dynamically increasing the encoding level of logical qubits and re-estimating probable recovery operation with the rollback of the decoding process. We investigate the performance and overhead of the Q3DE architecture with quantum-error

simulators and demonstrate that Q3DE effectively reduces the period of MBBEs by 1000 times and halves the size of their region. Therefore, Q3DE significantly relaxes the requirement of qubit density and qubit chip size to realize FTQC. Our scheme is versatile for mitigating MBBEs, i.e., temporal variations of error properties, on a wide range of physical devices and FTQC architectures since it relies only on the standard features of topological stabilizer codes.

### (2)特許出願

研究期間全出願件数: 0件(特許公開前のものは件数にのみ含む)

- (3) その他の成果(主要な学会発表、受賞、著作物、プレスリリース等)

- プレスリリース 1 件:「バーストエラーに耐性のある量子コンピュータのアーキテクチャを世界で初めて提案~量子コンピュータの動作状況に合わせ機能する誤り訂正機構を実現~」、九州大学ホームページ、2022 年 10 月

https://www.kyushu-u.ac.jp/ja/researches/view/814

- 研究会発表等 計 16 件

- 学生の受賞 1件:中村徹舟、Outstanding Undergraduate Student Award、cross-disciplinary workshop on computing Systems, Infrastructures, and programming (xSIG2023)

- 国際会議での Tutorial 開催 1 件:55th IEEE/ACM International Symposium on Microarchitecture (MICRO-55),

https://snu-hpcs.github.io/cryogenic\_tutorial\_micro22/