#### 研究課題別評価

- 1 研究課題名:実時間マルチタスク処理を支援するプロセッサアーキテクチャ

- 2 研究者氏名:田中清史

### 3 研究の狙い:

近年LSIの集積度が上がり、従来のプロセッサよりも大規模な回路が1チップに搭載可能となってきた。このことから、オンチップマルチプロセッサ化、システムオンチップ化が次世代のキーテクノロジーとして注目されている。また、シングルプロセッサの機構としても、特別な付加ハードウェアを必要とする各種機構が現実的に可能になってきた。しかし、従来の高速化を達成するための研究では、シングルタスクの高速化に重点が置かれてきた。本研究では、実時間(リアルタイム)汎用マルチタスク環境におけるプロセッサの有効実行性能を向上させるための機構をターゲットとする。

計算機はマルチタスク環境で使用されているが、これは各実行タスクが時分割でプロセッサを使用することにより実現されている。1つのタスクが一定時間プロセッサを使用した後、あるいは外部からの割り込みが発生した時、プロセッサコンテキストが入れ換えられ、他のタスクによるプロセッサ使用に移行する。現状のプロセッサにおいてプロセッサコンテキストを入れ換える際、入れ換え前の汎用レジスタおよびプログラムカウンタ、状態レジスタなどの専用レジスタの内容をメモリに退避し、入れ換え後のタスクのために汎用レジスタおよび専用レジスタの内容をメモリから読み出してセットするといった、メモリベースでの手続きが実行される。このような方式ではキャッシュミスなどの要因により、コンテキスト切り替えに要する時間が各タスクの有効実行時間に対して無視できない大きさになる。更には、リアルタイム性が要求されるタスクの場合には、コンテキスト切り替えの時間を含んだ最悪実行時間によってそのリアルタイム性を保障するため、このコンテキスト切り替えの処理時間を削減することによりタスク実行に余裕を持たせることが可能となる。また、組み込みシステムをターゲットとした場合、敏速な割り込み応答が要求されるため、割り込み処理への高速なコンテキスト切り替えが重要となる。

本研究では、従来のマルチスレッドアーキテクチャを拡張することによりタスク切り替えの際のレジスタ値やアドレス空間などのプロセッサコンテキストを入れ換える時間をゼロにするアーキテクチャ、およびキャッシュメモリを再構成することによりメモリアクセス時間を削減する方法を提案し、実際にプロセッサの回路を設計し、LSIを開発・評価してきた。

#### 4 研究成果:

近年、インテルの Pentium 4、IBM の POWER5 など、マルチスレッド型のプロセッサが出現してきた。マルチスレッドアーキテクチャは複数のスレッド(タスク)の実行コンテキストを内蔵し、それらを瞬時に切り替えて実行することにより、メモリアクセスレイテンシの隠蔽および命令実行ユニットの稼働率を向上させる。本研究で提案するプロセッサは基本的に block-multithreading 方式を利用し、スレッドの優先度を考慮した切り替えを行う。

### (1) プロセッサコンテキストバッファ

大規模データを対象とするアプリケーションの普及により、メモリアクセスの待ち時間はプログラムの全実行時間の75%にもおよぶとされている。このことはスレッド実行が頻繁にキャッシュミスを発生させることを意味する。したがって、数個のスレッドコンテキストを内蔵していても、メモリアクセスの全ての待ち時間を隠蔽することは困難である。一つのスレッドコンテキストを格納する領域を本研究ではプロセッサコンテキストセット(PCS)と呼ぶが、これを多数用意することはハードウェアのサイズおよびコストの面から困難であり、また実行ユニットに接続するための選択器(セ

レクタ)の規模が大きくなるため動作速度が低下する要因となる。そこで本研究では、小規模のハードウェアで仮想的に切り替え対象のスレッドコンテキスト数を増加させる"プロセッサコンテキストバッファ(PCB)"を提案した。

#### (2) 高速割り込み応答機構

割り込みが発生した際には、一般に割り込みハンドラは実行中のタスクのコンテキストをメモリに保存し、割り込み処理終了時に保存したコンテキストをメモリから読み出すことによって元のタスク実行に復帰する。このメモリベースの保存・復帰はキャッシュミスの原因となり、特に割り込みに対する応答時間が重要であるリアルタイムシステムでは問題となる。本研究ではマルチスレッドアーキテクチャを応用し、割り込み専用 PCS を用意することにより上記のオーバヘッドを削除する。すなわち、あるタスクの実行中に割り込み要求が発生した場合、そのタスクの PCS の内容はそのままにしておき、割り込み専用 PCS に切り替えて割り込み処理を行う。同様に割り込み処理終了時には、単に元の PCS に切り替えることによって元のタスク実行を再開する。

#### (3) 再構成可能キャッシュメモリ

従来のキャッシュメモリは、アプリケーションの参照するデータの時間的・空間的局所性にその効率が依存していた。今日の大規模数値計算やデータベース、メディアプロセッシングなどではデータ参照に局所性が無いものが多く、高速なキャッシュメモリの有効利用が困難になっている。またマルチスレッド型プロセッサにおいてスレッド同士でキャッシュを共有する場合、スレッド間でキャッシュ内の使用領域の競合が頻発し、キャッシュミスが増加、すなわちキャッシュ効率が低下する傾向がある。そこで本研究では、キャッシュメモリ管理法を動的に再構成することにより、データ参照効率を向上させることを提案した。提案した動的再構成により、優先度ベースパーティショニングおよびキャッシュメモリを利用した FIFO バッファの使用が可能となる。

### (4) プロトタイププロセッサ: PRESTOR-1

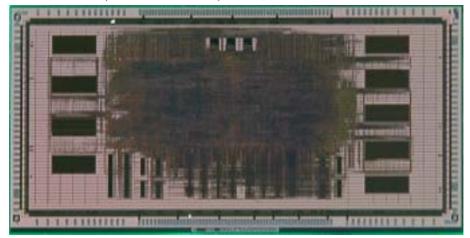

本研究では、提案する各種機構を持つプロセッサを実際に設計し、LSI として研究開発した。本プロセッサを PRESTOR-1 (PRESTO RISC-1) と呼ぶ。 開発した LSI チップの写真を図1に示す。

図1 PRESTOR-1 チップ写真

#### (5) 基本性能評価

ハードウェア記述言語 VHDL で記述された PRESTOR-1 の RTL シミュレーションにより各種機能の評価を行った。高速割り込み応答機構の評価において、割り込み発生 / 処理終了で毎回コンテキストの入れ替えを行う従来手法に対して、一回の割り込みあたり 230 サイクルを削減可能であることがわかった。これは主に、コンテキストの退避 / 復帰のためのストア / ロード命令実行

のオーバヘッドとキャッシュミス削減の効果である。また、再構成可能キャッシュメモリが提供する FIFO バッファの使用に関する RTL シミュレーションにおいて、FIFO バッファへのプリフェッチ効果 により、最大 83%のプログラム実行時間の削減が確認された。

## 5 自己評価:

本研究では、マルチタスク環境でリアルタイムアプリケーションを効率良く実行するプロセッサアーキテクチャの確立を目指した。このため、プロセッサコンテキストバッファ、高速割り込み応答機構および再構成キャッシュメモリなどの各種新機構を提案し、その有効性の評価を行った。また、最大の目標である、これらの新機構を搭載したプロセッサ LSI の開発・製造・評価を実施した。

一方、研究開発したプロセッサ LSI 上で基本性能評価などは実施できたが、時間の関係で実用 規模のアプリケーションを用いた評価が残った。また、評価の結果、キャッシュメモリの動的再構 成に関して、実行プログラムのメモリアクセスの振る舞いを考慮した更なる効率化を行う余地があ ることが判明した。更に、提案した高速化機構を最大限利用するためのプログラミングインタフェ ースを確立する必要がある。

今後の課題としては、提案するプロセッサアーキテクチャを用いた並列・分散環境の構築および、リアルタイム OS との連携により、リアルタイム性を向上させるシステムの実現が挙げられる。

# 6 研究総括の見解:

田中氏の研究は、マルチタスク環境でリアルタイムアプリケーションを効率よく実行するプロセッサアーキテクチャに関して、プロセッサコンテキストバッファ、高速割り込み応答機構、再構成キャッシュメモリなどの機構を提案し、その有効性の評価を行ったものである。具体的には、PRESTOR-1 と呼ばれるプロセッサーチップを開発した、基本性能に関しては、RTL シミュレーションにより評価を行い、予定された性能が得られることを確認している、実用的には、効率化に関しては改善点があることが判明しているが、限られた研究期間のなかで、構想から実装までを行い、一定の成果をあげたことは大いに評価できる。個人研究のなかでかなりの規模のものを構築した力量は評価に値する。

### 7 主な論文等:

- 1. Khairuddin Khalid and Kiyofumi Tanaka, Implementation of FIFO Buffer Using Cache Memory, 情報処理学会 計算機アーキテクチャ研究会, Vol.2002, No.150, pp.83 88, 2002 年.

- 2. Kiyofumi Tanaka, Fast Context Switching by Hierarchical Task Allocation and Reconfigurable Caches, Proc. of International Workshop on Innovative Architecture for Future Generation High-Performance Processors and Systems 2003, IEEE Computer Society Press, pp.20 29, 2003.

- 3. Khairuddin Khalid and KiyofumiTanaka, Evaluation of Cache Memory as FIFO Buffer, 情報処理学会 計算機アーキテクチャ研究会, Vol.2003, No.27, pp.91 96, 2003 年.

- 4. Kiyofumi Tanaka and Tomoharu Fukawa, Highly Functional Memory Architecture for Large-Scale Data Applications, Proc. of International Workshop on Innovative Architecture for Future Generation High-Performance Processors and Systems 2004, IEEE Computer Society Press, pp.109 118, 2004.

- 5. 今井俊晴, 田中清史, 高速フィルタリングを支援する高機能メモリコントローラ, 情報処理学会 計算機アーキテクチャ研究会, Vol.2004, No.123, pp.89 94, 2004 年.

- 6. Kiyofumi Tanaka, PRESTOR-1: A Processor Extending Multithreaded Architecture, International Workshop on Innovative Architecture for Future Generation High-Performance Processors and Systems, 2005.