# 東北大学大学院工学研究科 教授 小柳 光正

「脳型情報処理システムのための視覚情報処理プロセッサの開発」

## 1. 研究実施の概要

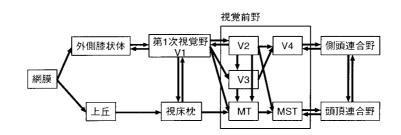

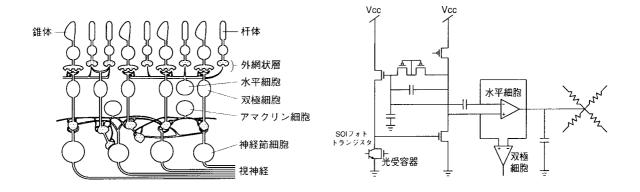

人間の作った情報処理システムであるコンピュータは集積回路技術の進歩に支えられて 飛躍的に性能が向上してきた。しかし、数値計算や記号処理の処理速度がいくら速くなっ ても画像や音声、図形や文字に対する認識能力は人間に比べるとまだ格段に劣っている。 人間の認識能力に匹敵するような情報処理能力を有するコンピュータを実現するためには、 これまでの計算論理やアルゴリズムに従ってハードウェア性能を改善して行くだけでは難 しく、人間の思考や認識のメカニズムに学んだ新しいアルゴリズムの導入が欠かせない。 このような情報処理システムを実現するためには新しいアルゴリズムやアーキテクチャの 研究と併せてそのための新しいハードウェア技術、特にシステム集積化技術に関する研究 が重要となる。そこで、本研究では人間のもつしなやかな情報処理システムを実現するた めの新しいアーキテクチャとハードウェア技術の両方を併せて開発し、実際にプロトタイ プのシステムを構築することを目的として研究を進めた。実際に構築するシステムは脳型 情報処理システムのプリプロセッサともなる視覚情報処理プロセッサである。脳における 高次の領野の機能の一部を実現することも目指した。具体的には本研究では図1に示すよ うな人間の視覚情報処理機能に近い機能をもつシステムをアナログ/デジタル混在回路技 術、システム集積化技術を駆使して構築する。図1のシステムは大きく分けると、光受容 器としての網膜、基本的な視覚情報処理を行う第一次視覚野、より高度の視覚情報処理を 行う視覚前野、パターン認識・学習に関係した側頭連合野、空間認知を行う頭頂連合野に 分けられ、それぞれが階層的な構成をしている。システム集積化技術はこのような階層構 造のシステムの構築に効力を発揮する。図1の構成の中の網膜について更に詳細な構造を

階層化されており、機能分化の進んだ細胞が層状構造をしている。神経節細胞から出力された視覚データは外側膝状体を介して第一次視覚野に送られる。本

示すと、図2のように

図1 人における視覚情報処理のブロック図

研究では先ず、網膜の部分をアナログ/デジタル CMOS 技術を用いて集積回路化する。 図3にこのような網膜細胞の回路モデルを示す。

図2 網膜の構造

図3 網膜の機能を模擬したアナログ CMOS 回路

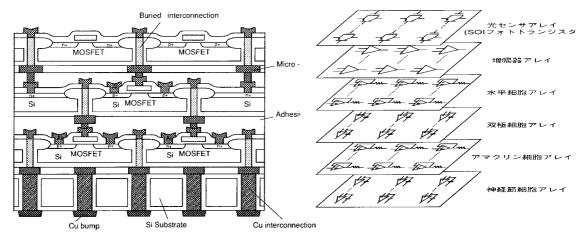

図4 3次元集積回路の概念図

図5 3次元集積化技術による人工網膜チップの構成

このような視覚情報処理システムを実際に構築するためには、図4に示すような3次元積層型集積回路を用いる必要がある。3次元積層型集積回路では、LSI チップを複数個積み重ねて、チップを貫通する垂直配線によってチップ間を電気的に接続する。このような構造は網膜や脳の層状構造と非常に似ており、特に、光受容器や各種の細胞が3次元的に密に詰まった網膜をシリコンチップで形成する場合には3次元積層型集積回路は必須となる。また、システムを3次元集積回路で構成するとシステムを小型化できるのでシステムの集積度が向上し、長距離配線も減って配線負荷が減少し、高速で低消費電力のシステムを実現できる。3次元集積化技術を用いて人工網膜を構築する場合の概念図を図5に示す。この図からも3次元集積回路が人工網膜の実現に最適であることがわかる。

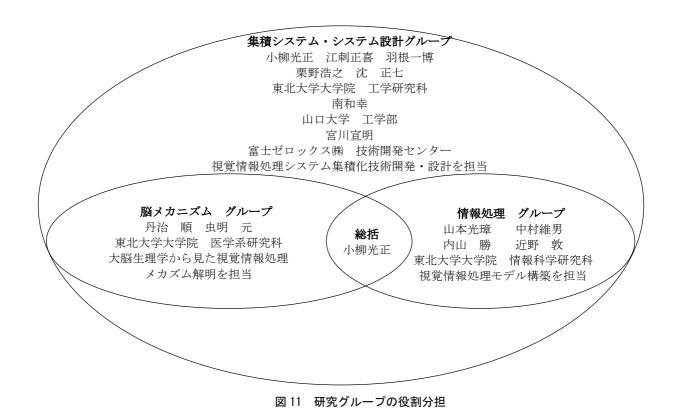

以上に述べたような視覚情報処理システムを構築するために、研究組織全体を集積システムグループ、情報処理モデルグループ、脳メカニズムグループ、システム設計グループの4つのグループに分け、緊密な連携を取りながら研究を進めた。このような研究体制のもとに得られた主要研究成果の概要を以下にまとめる。

#### 3次元集積化技術の開発(集積システムグループ)

研究期間を通じて、3次元集積化技術のための主要技術の開発とその改良を行なった。

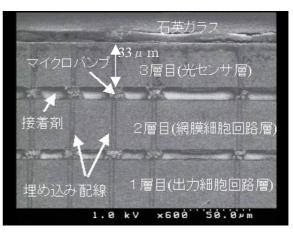

その技術を用いて、図6に示すように、フォトダイオード層と2層の CMOS 回路層からなる3層積層型のイメージセンサの試作に成功した。

また、より高性能で低電力の脳型視覚情報処理システムを構築するために、金属垂直配線技術、SOI による3次元集積回路、極微細トランジスタのための基盤技術(SiGe 選択成長、シリサイド、浅い接合の形成など)、さらには3次元集積回路チップ間を高速に接続するための光インターコネクション技術などに関する研究も行った。

図 6 試作した 3 次元積層型集積回路チップの SEM 断面観察写真図

# 3次元積層型人工網膜チップ(システム設計/集積システム/脳メカニズムグループ)

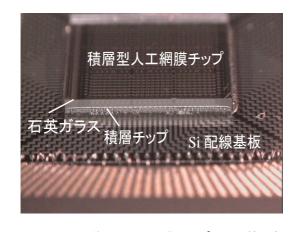

システム設計グループと集積システムグループが協力して、従来にない3次元積層型集積回路を用いたアナログ/デジタル CMOS 集積回路設計のための基礎技術検討を行い、その結果をもとにして網膜、第一野視覚野、MT 野、上丘の生体モデルに基づく網膜回路、V1 野回路、MT 野回路、上丘回路を設計した。生体モデルの構築には脳メカニズムグループが指導的役割を果たした。チップ試作は集積システムグループが担当した。試作した3次元積層型人工網膜チップのチップ写真を図7に示す。写真からわかるように、石英ガラス基板に3層積層構造をもつ人工網膜チップが貼り付けられている。視覚情報となる光信号は石英ス基板を通して入力される。この石英基板はパッケージの役割も果たしている。チップ裏面には出力端子として働く多くのマイクロ電極(バンプ)が形成されており、人工網膜チップはこのマイクロ電極アレイを介してシリコン配線基板に実装されている。し

図7 3次元積層型人工網膜チップの顕微鏡写真

出力画像

図8 3次元積層型人工網膜チップからの出力画像

たがって、従来のLSI チップで用いられているようなボンディングパッドやワイヤーボンディング、パッケージが不要であり、チップ面積と実装面積を著しく低減できる。このチップはパッケージ技術の点からみると、世界初の3次元積層型チップサイズパッケージであると言える。

#### 視覚情報処理システム(情報処理モデル/集積システムグループ)

人の網膜は解像度の高い中心視の部分(中心 高)と解像度の低い周辺視の部分より構成され る。このような構造は人の視覚情報処理にとっ て根源的なものであり、高次の視覚情報処理機 構を理解する上でも重要なものである。また、 3次元空間的な視覚情報を中心窩構造を有する センサーで収集、処理するためには注視点の移 動が必要不可欠である。そこで我々は、図9に 示す注視点移動ビジョンシステムを製作し、こ のような機能や構造を有する視覚情報処理シス テムを実現するための基礎検討を行った。

図9 注視点移動ビジョンシステム

# 2. 研究構想

人間の作った情報処理システムであるコンピュータは集積回路技術の進歩に支えられて飛躍的に性能が向上してきた。しかし、数値計算や記号処理の処理速度がいくら速くなっても画像や音声、図形や文字に対する認識能力は人間に比べるとまだ格段に劣っている。人間の認識能力に匹敵するような情報処理能力を有するコンピュータを実現するためには、これまでの計算論理やアルゴリズムに従ってハードウェア性能を改善して行くだけでは難しく、人間の思考や認識のメカニズムに学んだ新しいアルゴリズムの導入が欠かせない。このような情報処理システムを実現するためには新しいアルゴリズムやアーキテクチャ研究と併せてそのための新しいハードウェア技術、特にシステム集積化技術に関する研究が重要となる。そこで、本研究では人間のもつしなやかな情報処理システムを実現するための新しいアーキテクチャとハードウェア技術の両方を併せて開発し、実際にプロトタイプのシステムを構築することを目的として研究を進める。実際に構築するシステムは脳型情報処理システムのプリプロセッサともなる視覚情報処理プロセッサである。脳における高次の視覚情報処理部の機能の一部を実現することも目指す。

<u>研究のアプローチ</u>:本研究では、これまで解明されている視覚情報処理メカニズムに合うような回路モデルを提案し、その回路モデルの実現に適したシステム集積化技術を開発して、人間のもつ視覚情報処理機能に近い機能を有する新しい視覚情報処理システムを実現

するという研究のアプローチをとる。

#### 主要研究項目:

- ・網膜のもつ機能を記述するためのアナログ・デジタル CMOS 集積回路モデルの構築

- ・CMOS イメージセンサによる光受容器の形成と光学特性の評価

- ・集積回路微細加工技術とマイクロマシン技術を融合したシステム集積化技術の開発と 3次元集積回路および3次元集積システムの実現

- ・低電力アナログ・デジタル回路技術

- ・視覚情報処理のための新しいコンピュータ・アーキテクチャの検討

- ・視覚情報処理システムの設計および試作

具体的手法: 本研究では図1に示すような人間の視覚情報処理機能に近い機能をもつシス テムをニューラルネットワーク技術、アナログ/デジタル混在回路技術、システム集積化 技術を駆使して構築する。図1のシステムは大きく分けると、光受容器としての網膜、基 本的な視覚情報処理を行う第一次視覚野、より高度の視覚情報処理を行う視覚前野、パタ ーン認識・学習に関係した側頭連合野、空間認知を行う頭頂連合野に分けられ、それぞれ が階層的な構成をしている。システム集積化技術はこのような階層構造のシステムの構築 に効力を発揮する。図1の構成の中の網膜について更に詳細な構造を示すと、図2のよう な階層構造になっている。本研究では先ず、この網膜の部分をアナログ/デジタル CMOS 技術を用いて集積回路に焼き直す。網膜の機能の一部を模擬したアナログ CMOS 集積回路 を図3に示す。この回路は光受容部と水平細胞及び双極細胞からなる部分のみを表してい るが、アマクリン細胞と神経節細胞に関しても水平細胞や双極細胞と同様の回路で構成で きる。双極細胞、神経節細胞にはそれぞれオン型とオフ型があり、オン型どうし、オフ型 どうしが接続されてオン型チャネルとオフ型チャネルが形成される。オン型チャネルの興 奮によって明刺激が、オフ型チャネルの興奮によって暗刺激が検知される。水平細胞とア マクリン細胞は注目している錐体の周辺の情報を集める役割をする。図3の回路ではこの ような役割を可変抵抗とトランスコンダクタンス・アンプで表している。このような水平 細胞とアマクリン細胞の存在により、明暗のコントラストや色のコントラストが強調され 検知できるようになる。但し、これらを検知する受容野の大きさは細胞によって異なるの で、最適となるように回路設計を行う必要がある。

神経節細胞から出力された視覚データは外側膝状体を介して第一次視覚野に送られる。 第一次視覚野に送られたデータは線分抽出などの処理が施され、さらに高次の領野に送られ、形や動き、色などに関する情報処理が行われる。高次の視覚野に行くほど複雑な処理がなされて、側頭連合野や頭頂連合野ではパターン認識や記憶、空間認識が行われる。これら高次の視覚情報処理に関しては、ニューラルネットワークをベースとした新しい機能モデルを構築するとともに、それを用いた機能シミュレーションを高速に行なうための専 用並列プロセッサシステムを開発する。また、このシステムの高速化に必要な高速ネット ワークを構築するための光インターコネクション技術についても研究する。

以上に述べたような視覚情報処理システムを実際に構築するためには低雑音化と低消費電力化が鍵となる。そのためには、それを妨げる大きな要因である配線負荷を極力減らす必要がある。本研究では、システムを小型化し、システムとしての集積度を上げることによって長距離配線を減らし、配線負荷を低減しようとしている。複数のLSI チップ積み重ねて、チップを貫通する垂直配線によってチップ間を電気的に接続する3次元集積回路は、チップ当たりの集積度を上げて長距離配線を減らすのに特に効果がある。また、3次元積層型集積回路の構造は網膜や脳の層状構造と非常に似ており、光受容器や各種の細胞が3次元的に密に詰まった網膜をシリコンチップで形成する場合には3次元集積化は必須と考えられる。3次元集積化技術を用いて人工網膜を構築する場合の概念図を図5に示す。この図からも3次元集積回路が人工網膜の実現に最適であることがわかる。

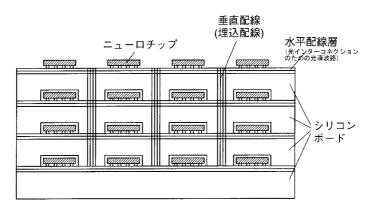

これまで、3次元集積回路はその製作技術の複雑さから実現が難しかったが、研究代表者等はウェーハ張り合わせに基づく新しい3次元集積化技術を提案し、これによって始めて3次元集積回路の試作が可能となった。また、図10に示すように、研究代表者等はこの

ような3次元集積化技術を更に 発展させて、シリコンボード上 に3次元集積回路チップを多数 搭載した3次元マルチチップモ ジュールのチップ間を高速の光 インターコネクションで接続し、 これを多層に積層する新しい3 次元システム集積化技術も提案 している。この技術を用いると、 高次の視覚情報処理機能を模擬 するためのニューラルネットワ

図 10 3 次元システム集積化技術を用いた 視覚情報処理システムの断面構造

一クの動作を高速にシミュレーションするための専用並列プロセッサの小型化が可能となる。高次の視覚情報処理機能に対するシミュレーションの精度を上げるためには、ニューラルネットワークのニューロン数を大幅に増やす必要があるが、ニューロン数が増えるとそれをシミュレーションするためのシステムも大型化する。そのため、システムを小型化できる3次元システム集積化技術はこのような専用並列プロセッサの実現に有用な技術である。本研究では、このような視覚情報処理システムや専用並列プロセッサ実現の鍵を握る3次元集積化技術および3次元システム集積化技術の開発も行なう。

研究の進め方:本研究では実際のシステムの製作まで行うため、研究期間を5年とする。 最初の2年間は人間の視覚情報処理や認識、学習などに関する生理学的データや心理学的 データを基に、基本となるアルゴリズムやアーキテクチャの検討を行う。それに基づいた テスト回路の設計・試作と3次元集積化技術、システム集積化技術の確立も行う。3年目 から実際のシステムの設計を始め、4年目に人工網膜チップ試作と視覚情報処理システム の構築を行う。5年目は修正、改良を加えてシステムを完成し、研究の総括を行う。

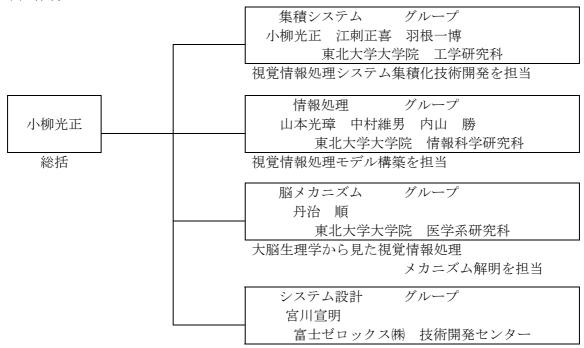

研究の役割分担: それぞれの役割を考慮して、研究組織全体を集積システムグループ、情報処理モデルグループ、脳メカニズムグループ、システム設計グループの4つに分け、緊密な連携を取りながら研究を進める。以下に各グループのおよその役割を示す。

①集積システムグループ (主要研究機関 東北大学大学院 工学研究科)

· 主要構成員

小柳光正 東北大学大学院 工学研究科 教授

江刺正喜 東北大学大学院 工学研究科 教授

羽根一博 東北大学大学院 工学研究科 教授

栗野浩之 東北大学大学院 工学研究科 助教授

南 和幸 山口大学大学院 工学研究科 助教授 (東北大学より移動)

・研究題目

システム集積化技術とそれを用いた視覚情報処理システムの開発

・目的および内容

集積回路微細加工技術とマイクロマシン技術を融合した新しいシステム集積化技術を用いて人間の視覚情報処理機能に近い機能をもつ視覚情報処理システムを構築することを目的とし、主導的立場で研究を遂行する。まず、3次元集積回路技術を用いて3次元積層型の人工網膜チップを開発する。そのためのアナログ・デジタル CMOS 集積回路モデルの構築も行う。さらに、高次視覚野の機能を実現するための技術開発も行う。

②情報処理モデルグループ(主要研究機関 東北大学大学院 情報科学研究科/工学研究科)

・主要構成員

中村維男 東北大学大学院 情報科学研究科 教授 山本光璋 東北大学大学院 情報科学研究科 教授 内山 勝 東北大学大学院 工学研究科 教授 近野 敦 東北大学大学院 工学研究科 助教授

• 研究題目

視覚情報処理モデルと視覚情報処理アーキテクチャに関する研究

・目的および内容

視覚情報処理モデルの構築とそれを視覚情報処理システムに組み上げるためのシステム・アーキテクチャを提案することを目的とする。人の網膜は解像度の高い中心視の部分

(中心窩)と解像度の低い周辺視の部分より構成される。このような構造は人の視覚情報処理にとって根源的なものであり、高次の視覚情報処理機構を理解する上でも重要なものである。また、3次元空間的な視覚情報を中心窩構造を有するセンサーで収集、処理するためには注視点の移動が必要不可欠である。そのための機械的な駆動機構の研究と中心窩を有するセンサーによる視覚情報処理技術の開発を行う。

③脳メカニズムグループ (主要研究機関 東北大学大学院 医学系研究科)

・主要構成員

丹治 順 東北大学大学院 医学系研究科 教授 虫明 元 東北大学大学院 医学系研究科 助教授

・研究題目

大脳生理学から見た視覚情報処理メカニズムに関する研究

・目的および内容

大脳生理学という広い立場から、脳における情報処理機能を記述するモデルや他のグループが研究を進める回路・アーキテクチャモデルの妥当性について考察することを目的とする。運動と視覚情報処理という観点から視覚情報処理メカニズムに関する研究を行い、視覚情報処理のための基礎となる基本メカニズムの考察を行う。

- ④システム設計グループ (主要研究機関 富士ゼロックス㈱ 技術開発センター) (構成員の移動に伴い、研究期間途中から集積システムグループと合流した。)

- ・主要構成員 宮川宣明 富士ゼロックス (株) 技術開発センター 技術主幹

- ・研究題目 視覚情報処理システムのためのシステム設計に関する研究

- ・目的および内容

視覚情報処理システムを実際に試作するためのシステム設計技術を構築することを目的とする。新しいニューラルネットワーク・モデルや回路モデル、システム・アーキテクチャ等を取り入れた視覚情報処理システムを設計するための設計ライブラリーを作成して回路およびシステムの計算機シミュレーションを行い、システム性能を評価する。

## 3. 研究実施体制

#### (1) 体制

#### 4. 研究期間中の主な活動

(1) ワークショップ・シンポジウム等

| 年月日              | 名称                                  | 場所                 | 参加人数 | 概要                                                                                                                     |

|------------------|-------------------------------------|--------------------|------|------------------------------------------------------------------------------------------------------------------------|

| 平成 15 年 1 月 29 日 | マイクロ・ナノマシニング・セミナー 脳型情報処理システムと 医工学応用 | 東北大学工学 部 機械系第一講 義室 |      | 5年間にわたる各チーム<br>の研究成果の発表を行う。<br>また我々の開発した視覚<br>情報処理プロセッサの有<br>力な応用である人に移植<br>可能な人工眼に関してカ<br>リフォルニア大の Liu 教授<br>に講演いただく。 |

| 平成 12 年 3 月 22 日 | マイクロ・ナノマシニング・セミナー 生体情報処理と知能集積システム   | 東北大学工学部青葉記念会館      | 105名 | 脳の原理に基づくコンピュータ開発と題して理化学研究所市川道教氏によりでのでは、その後、大頭脳数学的モデルンリ視覚情報処理プロセッサ視覚情報処理で研究を明発状況まで研究をあるの成果の外部発表とチーム内の議論を行う。             |

## 5. 主な研究成果

- (1) 論文発表(国内 9件、海外 27件)

- 1. 栗野浩之、小柳光正"ウェーハレベル3次元集積化技術"表面技術第 53 巻第4号 (2002.4)

- 2. K.W. Koh, H.J. Oh, H. Choi, H, Kurino, M. Koyanagi "A novel atomic doping technology for ultra-shallow junction of SOI-MOSFETs" Materials Science and Engineering B89 (2002) 435-438

- 3. Hiroyuki KURINO, Yoshihiro NAKAGAWA, Tomonori NAKAMURA, Yusuke YAMADA, Kang-Wook LEE and Mitsumasa KOYANAGI "Biologically Inspired Vision Chip with Three Dimensional Structure" IEICE Transactions on Electronics, E84-C (12), 1717-1722, (2001)

- 4. H. Kurino, Y. Nakagawa, K.W. Lee, T. Nakamura, Y. Yamada, K.T. Park, M. Koyanagi "Smart Vision Chip Fabricated Using Three Dimensional Integration Technology" ADVANCES IN NEURAL INFORMATION PROCESSING SYSTEMS 13 (MIT Press) 720-726(2001)

- 5. 栗野浩之、中川源洋、李 康旭、中村共則、山田裕介、諸岡 哲、稲村 清、朴 起台、 小柳光正 "三次元集積化技術を使ったビジョンチップ"社団法人 電子情報通信学会 信学技報、101 (85), 29 35 (2001)

- 6. 小柳光正 "新しい共有メモリを用いた並列処理システム"(社) 電子情報通信学会 信 学技報、(2001), 59 65

- 7. Wang Y, Shima K, Sawamura H, Tanji J. "Spatial distribution of cingulate cells rojecting to the primary, supplementary, and pre-supplementary motor areas: a retrograde multiple labeling study in the macaque monkey." Neuroscience Research 39:39-49 (2001)

- 8. Mushiake H, Saito N, Sakamoto K, Sato Y, and Tanji J "Visually based path-planning by

- Japanese monkeys" Brain Research Cognitive Brain Research 2001 11: 165-169 (2001)

- Mushiake H, Saito N, Furusawa Y, Izumiyama M, Sakamoto K, Shamoto H, Shimizu H, and Yoshimoto T "Orderly activations of human cortical areas during path-planning task" Neuroreport 13 423-426 (2001)

- 10. Tanji J. "Sequential organization of multiple movements: involvement of cortical motor areas." Annu Rev Neurosci 2001; 24:631-51

- 11. N. Katayama, M. Nakao, M. Yamamoto "Computation in Single Neuron with Dendritic Trees" Brainware: Bio-inspired Architecture and Its Hardware Implementation, World Scientific, 179-205, (2001)

- 12. Ki-Seon Kim, Yun-Heub Song, Ki-Tae Park, Hiroyuki Kurino, Takashi Matsuura, Kazuhiro Hane, Mitsumasa Koyanagi "A Novel Doping Technology for Ultra-shallow Junction Fabrication: Boron Diffusion from Boron-adsorbed Layer by Rapid Thermal Annealing" Thin Solid Films, 369, (2000), 207 212

- 13. Kang Wook Lee, Tomonori Nakamura, Katsuyuki Sakuma, Ki Tae Park, Hiroaki Shimazutsu, Nobuaki Miyakawa, Ki Yoon, Kim, Hiroyuki Kurino and Mitsumasa Koyanagi "Development of Three-Dimensional Integration Technology for Highly Parallel Image-Processing Chip" Jpn.J.Appl.Phys., 39, (2000), 2473 2477

- 14. Y.H. Song, K.T. Park, H. Kurino, M. Koyanagi "Ultrashallow Junction Formation by Rapid Thermal Annealing of Arsenic-Adsorbed Layer" Japanese Journal of Applied Physics Vol.39, (2000), pp26-30

- 15. 朴 起台、裵 志哲、高 光旭、栗野浩之、小柳光正、原子層吸着拡散法による極浅接合の形成とサブ $0.1\mu$  m MOSトランジスタの試作、(社)電子情報通信学会 信学技報、ED2000-132, SDM2000-114 ICD2000-68, (2000-08), 57-64

- Y.H. Song, J.C. Bae, M. Oonishi, T. Honda, H. Kurino and M. Koyanagi, "Ultra-shallow junction technology by atomic layer doping from arsenic adsorbed layer", ELECTRONICS LETTERS, 35 (5), (1999), 431-433

- 17. Yasuhiro Kuwana, Akinori Hirose, Hiroyuki Kurino and Mitsumasa Koyanagi "Signal Propagation Characteristics in Polyimide Optical Wave-guide with Micro-Mirrors for Optical Multichip Module" Japanese Journal of Applied Physics Vol.38, (1999), pp2660-2663

- 18. M. Sasaki, Xiaoyu Mi, K. Hane "Standing Wave Detection and Interferometer Application Using a Photodiode Thinner Than Optical Wavelength" Applied Physics Letters, 75, (1999), 2008-2010

- 19. N. Katayama, M. Shimakata, M. Nakao, M. Yamamoto "Nonlinear synaptic integration in hippocampal CA1 pyramidal neurons" Neuroscience Research (Suppl.), 23, S259, 1999

- 20. 嶋方克好、片山統裕、中尾光之、山本光璋 "海馬 CA1 錐体ニューロンにおける非線形シナプス統合"信学技報、MBE99-111, 61-68, 1999

- 21. M. Nakao, H. Nishiyama, D. McGinty, R. Szymusiak, M. Yamamoto "Model-based Interpretation of Biphasic Daily Pattern of Sleepiness" Biol. Cybernetics, 81, (1999), 403-414

- 22. H. Sakai, M. Nakao, M. Yamamoto "A Circle Map Model of Human Circadian Systems" Frontiers of Medical and Biological Engineering, 9, (1999), 75-92

- 23. M. Nakao, M. Yamamoto "Modeling Neuronal Dynamics-Transition during Sleep" IEEE Eng. Med. & Biol. Magazine, 17, (1999), 99-107

- 24. M. Yamamoto, K. Suzuki, K. Nakamura, M. Nakao, N. Katayama and T. Ueno "Novel

- Polygraphic Observations in High Frequency Range during Rapid Eye Movement Sleep" Interdisciplinary Information Sciences, 5 (2), (1999), 99-108

- 25. M. Nakao, D. McGinty, R. Szymusiak, M. Yamamoto "Thermoregulatory Model of Sleep Control: Losing the Heat Memory" J. Biol. Rhythms, 14 (6), (1999), 547-556

- 26. Mushiake H, Fujii N, Tanji J "Microstimulation of the lateral wall of the intraparietal sulcus compared with the frontal eye field during oculomotor tasks" J Neurophysiol 81(3): 1443-1448, 1999

- 27. Sakai ST, Inase M, Tanji J "Pallidal and cerebellar inputs to thalamocortical neurons projecting to the supplementary motor area in Macaca fuscata: a triple-labeling light microscopic study" Anat Embryol(Berl) 199(1): 9-19, 1999

- 28. 丹治 順 "脳と運動ーアクションを実行させる脳" 共立出版

- 29. 虫明 元、丹治 順 "大脳による行動と運動の認知的制御"実験医学 17 巻 2198-2204 1999

- 30. 丹治 順、五味裕章 "運動制御と学習" 科学 69(2): 114-124 1999

- 31. 丹治 順 "脳と運動 In. 脳を知る・創る・守る"(「脳の世紀」推進会議編 伊藤 正男、養老孟司、小田 稔 他) クバプロ 71-84 1999

- 32. Hiroyuki Kurino, Kang Wook Lee, Katsuyuki Sakuma, Tomonori Nakamura and Mitsumasa Koyanagi "A New Wafer Scale Chip-on-Chip (W-COC) Packaging Technology Using Adhesive Injection Method" Jpn. J. Appl. Phys. Vol.38 (1999) pp2406-2410

- 33. T. Matsumoto, M. Sato, K. Sakuma, H. Kurino, N. Miyakawa, H. Itani and M. Koyanagi "New Three-Dimensional Wafer Bonding Technology Using the Adhesive Injection Method" Jpn.J.Appl.Phys.Vol.37 pp1217-1221 (1998 March)

- 34. M. Koyanagi, H. Kurino, K-W. Lee, K. Sakuma, N. Miyakawa, H. Itani "Future System-on-Silicon LSI Chips" IEEE MICRO (1998) Vol.18 No.4 pp17-22

- 35. H. Kurino, K. Hirano, T. Ono and M. Koyanagi, Evaluation of Shared DRAM for "Parallel Processor System with Shared Memory", IEICE Transactions on Fundamentals of Electronics, Communications and Computer Sciences, E81-A (12), (1998), 2655-2660

- 36. M. Yamamoto, M. Nakao, N. Katayama, M. Waku, K. Suzuki, K. Irokawa, M. Abe, T. Ueno "Nighit-day-night sleep-wakefulness monitoring by ambulatory integrated circuit memories" Psychiatry and Clinical neurosciences, 53, 171-173, 1999

- (2) 特許出願(国内 1件、海外 0件)

1. 発明者 : 小柳光正 栗野浩之

発明名称: 3次元半導体集積回路装置の製造方法

出願番号:特開平 11-261001 出願日: 平成 10 年 3 月 13 日

## (3) 受賞等

①受賞

研究代表者(小柳): 文部科学大臣賞(科学技術功労者) 平成 13 年

#### ②新聞報道

- 1. 日経産業新聞 平成 13 年 6 月 29 日 「脳を創る」研究活発 東北大 人工の目を試作

- 日本工業新聞 平成13年3月14日 人工網膜チップ開発

- 3. 日刊工業新聞 平成13年3月13日 立体積層で画像高速処理

- 4. 日経新聞 平成13年3月10日 網膜チップ 東北大が開発

- 5.毎日新聞 平成13年3月10日立体人工網膜 3層構造のチップを開発

- 6. 日経マイクロデバイス 平成 13 年 3 月 具体化する ASET の 3 次元積層接続技術、LSI 配線長を大幅短縮

- 日経マイクロデバイス 平成13年2月

ISSCC 速報: 3次元実装に新しい展開

- 8. 日経産業新聞 平成13年1月16日 3次元メモリー試作 複数の計算機で情報共有

- 9. 日経マイクロデバイス 平成 12 年 7 月 LSI 技術で脳型情報処理の実現へ視覚、学習・連想の各チップを試作

- 10. 日刊工業新聞 平成12年1月19日 3次元集積化技術を確立

- 11. 日本経済新聞 平成 12 年 11 月 20 日 高性能並列コンピューター

- 12. 日本経済新聞 平成 12 年 4 月 12 日高性能並列コンピューター 複数 MPU 同時活用

- 13. 日刊工業新聞 平成 12 年 4 月 17 日 演算性能 10 ギガ FLOPS スパコン並みの高速処理

- 14. 河北新報 平成12年4月3日複数コンピューター結合 スパコン並み能力

- 15. 毎日新聞 平成 10 年 8 月 8 日 情報処理システム研究最前線 科学計算の時間短縮へ