東京工業大学

量子ナノエレクトロニクス研究センター

教授

小田 俊理

「ネオシリコン創製に向けた

構造制御と機能探索」

研究期間：平成 11 年 1 月 1 日～平成 16 年 10 月 31 日

## 目次

|                                                                      |    |

|----------------------------------------------------------------------|----|

| 1. 研究実施の概要 ······                                                    | 1  |

| 2. 研究構想 ······                                                       | 5  |

| 3. 研究成果                                                              |    |

| 3-1. チーム全体の成果 ······                                                 | 9  |

| 3-2. ネオシリコン作製グループ                                                    |    |

| 3-2-1. ネオシリコン構造制御 ······                                             | 10 |

| 3-2-2. ナノ結晶シリコン量子ドット単電子デバイス ······                                   | 23 |

| 3-2-3. ナノ結晶シリコン平面型電子放出素子 ······                                      | 31 |

| 3-2-4. NEMSメモリデバイス ······                                            | 38 |

| 3-3. 微細構造電気特性評価グループ                                                  |    |

| 3-3-1. Introduction ······                                           | 45 |

| 3-3-2. SETs in polycrystalline silicon ······                        | 46 |

| 3-3-3. SETs in nanocrystalline silicon ······                        | 47 |

| 3-3-4. Electron coupling effects in nanocrystalline silicon SETs ··· | 51 |

| 3-3-5. Conclusion and assessment of results ······                   | 54 |

| 3-4. 少数電子デバイスグループ                                                    |    |

| 3-4-1. ネオシリコンにおける電子輸送・電子放出の理論解析 ······                               | 63 |

| 3-4-2. ナノ結晶シリコン薄膜における粒界制御と単電子帶電効果 ···                                | 80 |

| 3-4-3. 研究成果のまとめ、評価及び今後期待される効果 ······                                 | 92 |

| 3-5. 発光・電子放出検討グループ                                                   |    |

| 3-5-1. ねらい ······                                                    | 95 |

| 3-5-2. 研究実施方法・体制 ······                                              | 95 |

| 3-5-3. 成果の概要 ······                                                  | 95 |

| 3-5-4. 当該分野における位置づけと産業技術上のインパクト ······                               | 95 |

| 3-5-5. 研究項目ごとの成果 ······                                              | 96 |

| 3-5-6. 今後の研究の方向と見通し ······                                           | 97 |

|                               |     |

|-------------------------------|-----|

| 3－6. 素子応用検討グループ               |     |

| 3－6－1. はじめに                   | 105 |

| 3－6－2. 弹道電子放出素子               | 106 |

| 3－6－3. 超低消費電力不揮発性スイッチング素子     | 108 |

| 3－6－4. 得られた研究成果の評価及び今後期待される効果 | 114 |

| 4. 研究実施体制                     |     |

| (1) 体制                        | 117 |

| (2) メンバー表                     | 118 |

| 5. 研究期間中の主な活動                 |     |

| (1) ワークショップ・シンポジウム等           | 122 |

| (2) 招聘した研究者等                  | 123 |

| 6. 主な研究成果物、発表等                |     |

| (1) 発表論文                      | 124 |

| (2) 口頭発表                      |     |

| ① 招待、口頭講演                     | 129 |

| ② ポスター発表                      | 138 |

| (3) 特許出願                      | 139 |

| (4) 新聞報道等                     | 139 |

| (5) その他特記事項                   | 140 |

| 7. 結び                         | 141 |

## 1. 研究実施の概要

### 1. 1 基本構想

半導体ナノ構造の量子効果に基づく特異物性の研究が盛んであるが、今後はナノ構造の間隔を制御して、粒子間の相互作用を究明することが重要である。

本研究では、粒径 3-5nm のナノ結晶シリコン量子ドットを、間隔 1-2nm に制御して配列させる新材料「ネオシリコン」を提案し、独自のアイデアによりこれを形成して、その機能を探索することを目的とした。ネオシリコンは従来の結晶シリコンやアモルファスシリコンの中間的性質を持つのではなく、何れとも全く異なる新物性が室温で期待できる新材料として捕えた。ナノ結晶シリコンの粒径は、量子サイズ効果によりネオシリコンのバンドギャップエネルギーを決定する。ドット間隔は、ネオシリコンの電気伝導度を決定する。ドット間のトンネル過程は帶電エネルギーによっても制御される。

要求される構造制御性は原子スケールが必須である。本研究は、デジタルプラズマプロセスのアイデアにより、核形成と結晶成長を時間分離してシリコン量子ドットの粒径(3-5nm)を均一に制御する技術、化学アニーリング法により粒子間の中距離構造を制御する技術、直接窒化により超薄(1-2nm)絶縁膜を形成する技術など、オリジナル技術を相乗的に用いて形成したネオシリコン特有の機能を探索した。機能探索のため、ナノメートルレベルのネオシリコンの局所電子輸送特性、ネオシリコンからの光放出、電子放出特性など、独自評価技術と計算機利用物性予想技術を駆使した。ネオシリコンの材料新機能面では、バリスティック電子伝導・放出、室温单電子チャージング効果、ナノシリコン粒間の静電的・量子力学的相互作用、などを観測・制御することに成功した。

ネオシリコンは従来の材料にはない量子効果物性を人工的に顕在化した第三のシリコン材料と位置付けている。そのため、従来の延長上に無い全く新しい応用を見出せる可能性がある。もちろん、ヘテロ接合、単一電子トンネリング、共鳴トンネリング、高効率可視光発光、高輝度電子放出などの機能は、従来のデバイスの限界を超えた超大規模集積化、超高速化、超低消費電力化などへの大きな波及効果が期待できる。また、これら新しい機能を従来シリコン集積回路に組み込むことにより、幅広いシステムオンチップ、システムオンディスプレイへの展開が期待できる。また、産業技術として確立しているシリコンプロセスを最大限活用することができ、既存の集積回路との結合性も良いので、実用化される時期は比較的早い段階と考えられる。そのため、電子産業の新たなハネムーン時代を築くべく、デバイス応用の提案にも注意を払ってきた。ネオシリコンの新機能に着目した、高効率表示素子、超低消費電力不揮発性情報記録素子、室温单電子デバイス、ナノメカニカル不揮発性メモリなど、新たな応用研究分野の可能性を広く開拓した。

### 1. 2 実施・研究成果概要

本研究の実施・成果概要は、(1) ネオシリコン作製と構造制御、(2) ネオシリコン電気特性制御、(3) ネオシリコン発光・電子放出特性制御、(4) ネオシリコンの素子応用検討、に大別される。以下に、それぞれのタスクの実施・成果の概要を記載とともに、表 1. 1 で全体をまとめた。

## 1. ネオシリコン構造作製・制御

ナノ結晶シリコンの粒径と粒子間隔を原子スケールで制御した新材料「ネオシリコン」を提案し、デジタルプラズマプロセスやラジカル窒化などユニークな材料制御技術を導入することによりネオシリコンの作製・構造制御技術開発を推進した。研究代表者が開発したVHFプラズマCVD技術において、原料ガスの種類やパルス供給時間、プラズマセル圧力など粒子形成条件の総合的制御を行うことによってシリコンナノ粒子の粒径の均一化を図った。その結果、最小粒径5nm、分散±1nmの極めて均一性の高いシリコン粒子の作製に成功した。また、ナノ結晶シリコンドットの周囲に形成される酸化膜のストレス効果による酸化速度の自己停止機構を利用した寸法制御法を検討した。750°Cで酸化を行うと、酸化速度の飽和が起こり、初期の寸法10nmの粒子は4nmで安定することをTEM観察により確認した。低温ラジカル窒化技術を開発して、薄くて均一な窒化膜をシリコン量子ドットの表面に形成する方法を開発した。更に、ナノ結晶シリコンドットの高密度化・高集積化を図るために、弗酸、純水、メタノール等、種々の溶液中にナノ結晶シリコンドットを分散させ、その濃縮溶液を基板上に滴下・蒸発させる手法を検討した。その結果、メタノールを溶媒とした分散液により、面密度で約 $7 \times 10^{11} \text{ cm}^{-2}$ の高密度化に成功した。

## 2. ネオシリコン電気特性評価

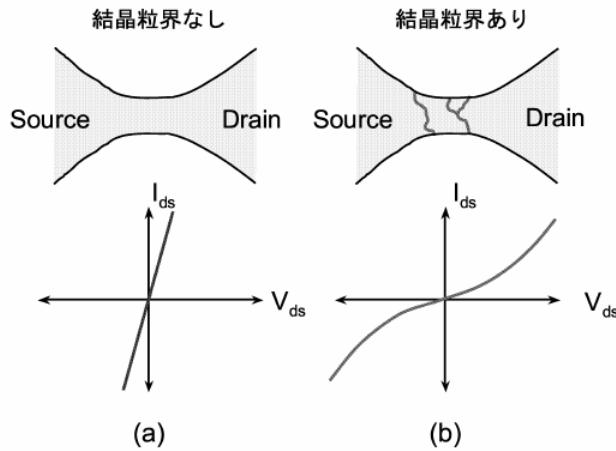

シリコンナノ構造間のトンネル過程に着目して、ネオシリコンの電気特性を調べると同時に、単電子デバイス応用を検討した。種々の大きさのポイントコンタクトトランジスタを形成し、シリコンナノ構造の電子輸送特性を系統的に調べた。特にポイントコンタクト中に結晶粒界が0個の場合はパリスティック伝導を観測し、1個の場合には非線形電流電圧特性を、複数個の場合には単電子トンネル特性を観測した。また、ネオシリコン中の粒界特性を制御するため、高温酸化処理、2段階酸化処理（低温長時間酸化+高温アニーリング）、熱水蒸気処理等のパッシベーション処理を施すことによる粒界の電気特性と微視的構造の変化を評価した。その結果、2段階酸化処理により粒界は厚さ2~3nm、エネルギー障壁高さ170meVの良質なトンネル障壁となることを見出し、単電子トランジスタの高温動作化に向けた粒界最適化のガイドラインを得た。このプロセスを適用することにより室温で電流のクーロン振動を示す単電子トランジスタの開発に成功した。

また、2つのナノ結晶シリコンドット間の相互作用を観測・評価するため、チャネル内に2個の並列量子ドットを有するポイントコンタクトトランジスタを作製し、2つのサイドゲート電圧を独立に変化させた際のクーロン電流振動の変化を測定した。その結果、2個の量子ドット間の静電相互作用による電流ピークのスイッチング現象を観測し、スイッチング領域でのピーク電圧のシフトから、2個のシリコンドット間の結合容量を評価できることを見出した。さらに、粒界によるトンネル障壁が特に薄いために2量子ドットが強く結合した素子では、共鳴準位間でのコヒーレントなカップリングによって結合・反結合軌道（準分子状態）が形成されていることを4.2Kで観測することに成功した（シリコン系で世界初）。電流ピーク間隔から結合・反結合軌道エネルギー間隔を評価し、GaAs/AlGaAs系の2重ドットに対して報告されている値に比べて1桁近い値（約0.4meV）になっていることを見出した。

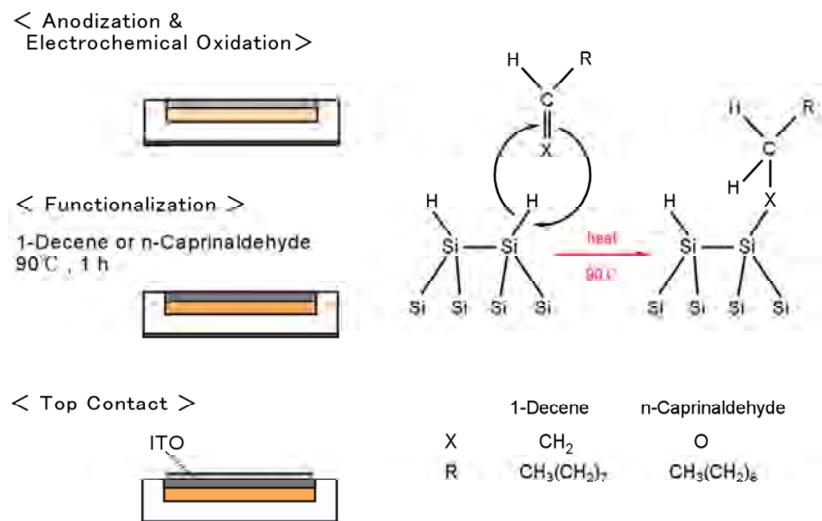

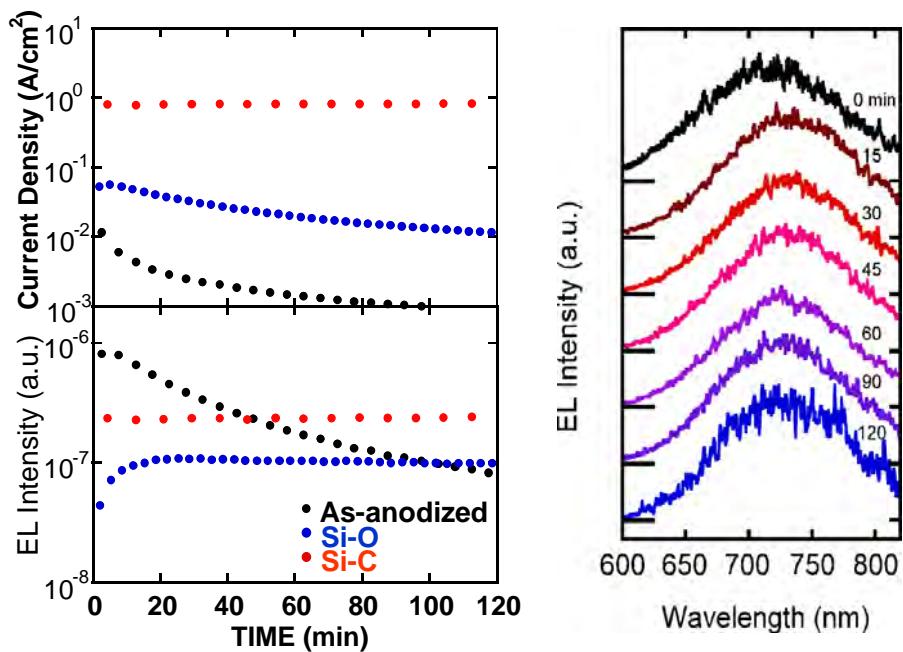

### 3. ネオシリコン発光・電子放出特性評価

高効率・高安定の発光素子ならびに高機能の面放出電子源の開発を目的として、ナノシリコンの発光特性および電子放出の特性評価を行った。シリコン発光素子の高効率化については酸化処理の適正化によるリーク電流低減と動作安定化については、素子の表面を  $\text{SiO}_2$  膜でキャップする方法とナノ結晶シリコン自身の表面水素終端を共有結合で置き換える方法につき、赤色ELにおいてそれぞれ別個に有効性を確認した。シリコン発光素子のマルチカラー化については、熱酸化を行わず、ナノ結晶シリコンのサイズ制御のみでPLでは赤・緑・青色発光を得ることができた。

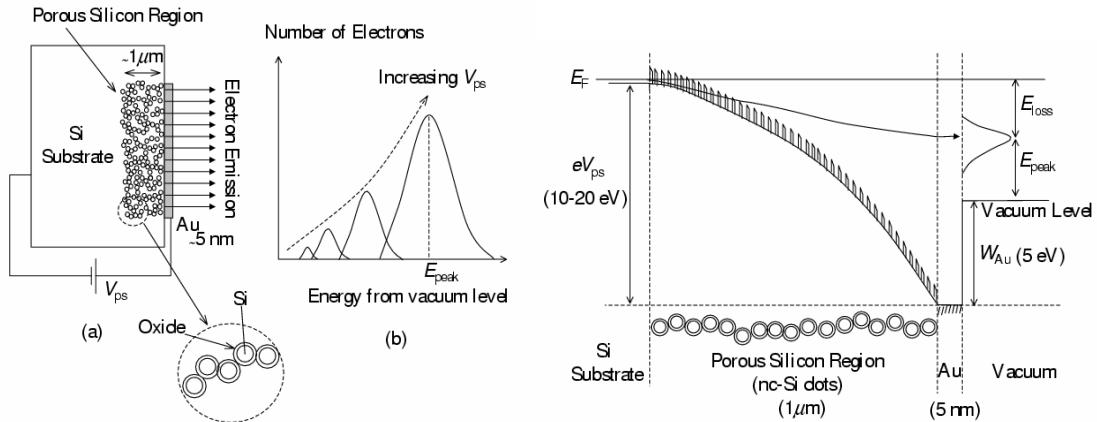

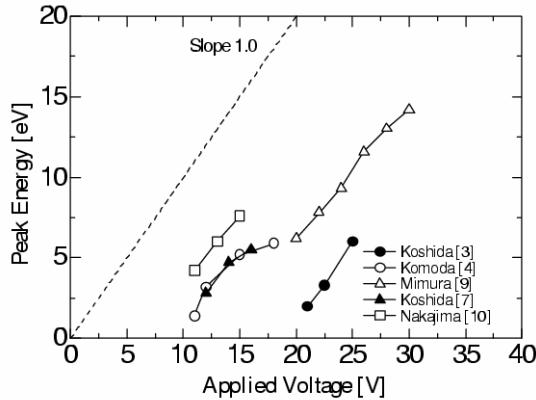

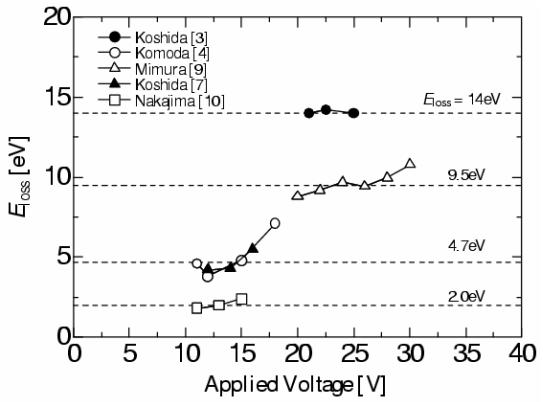

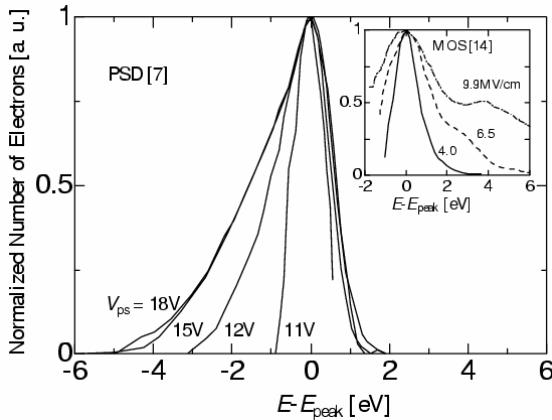

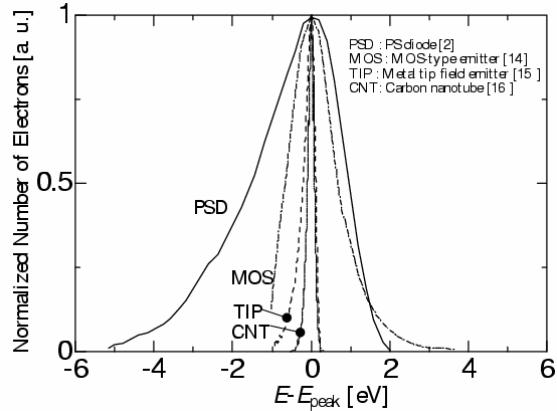

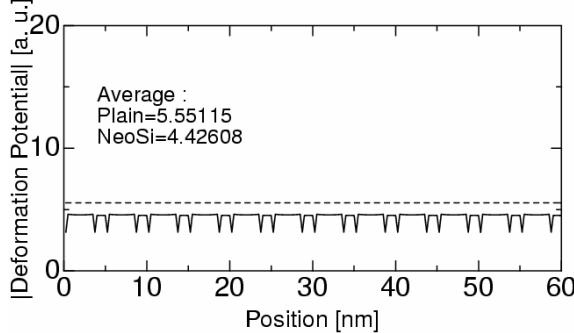

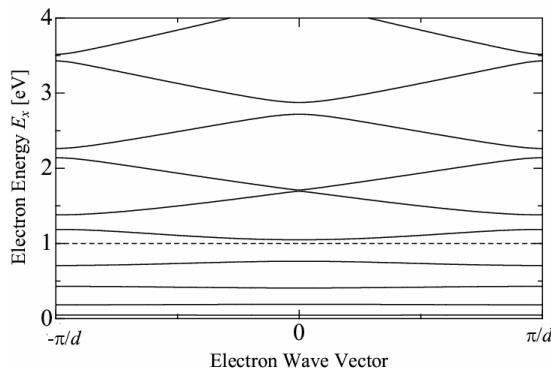

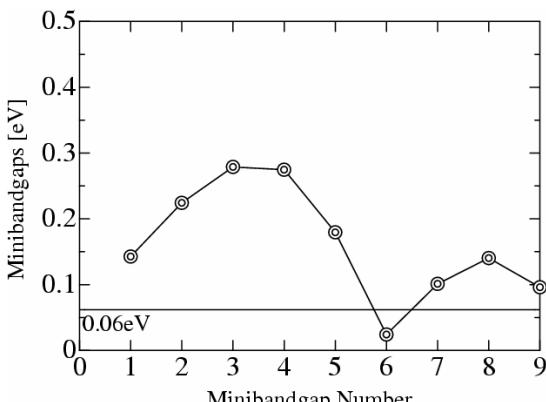

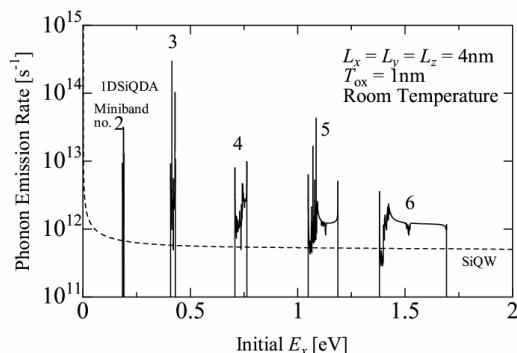

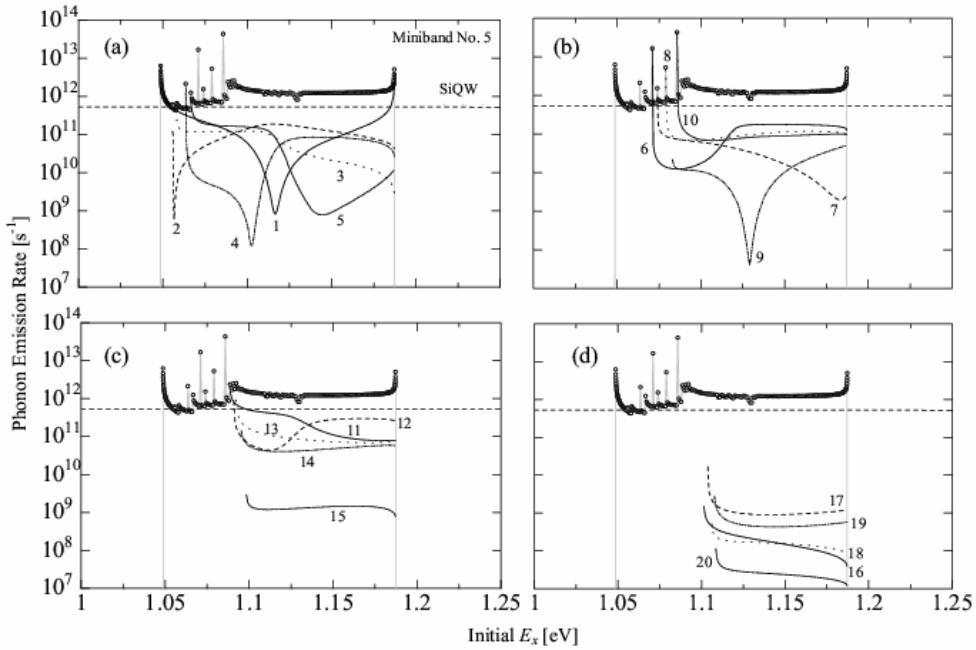

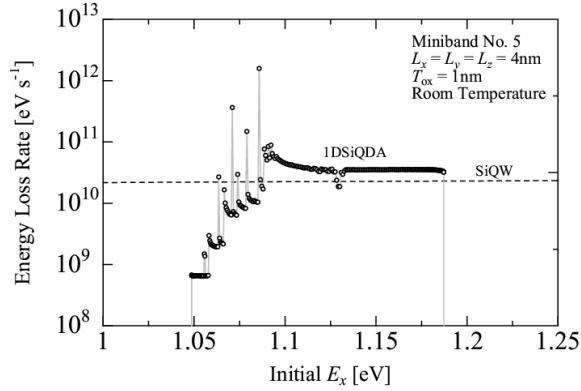

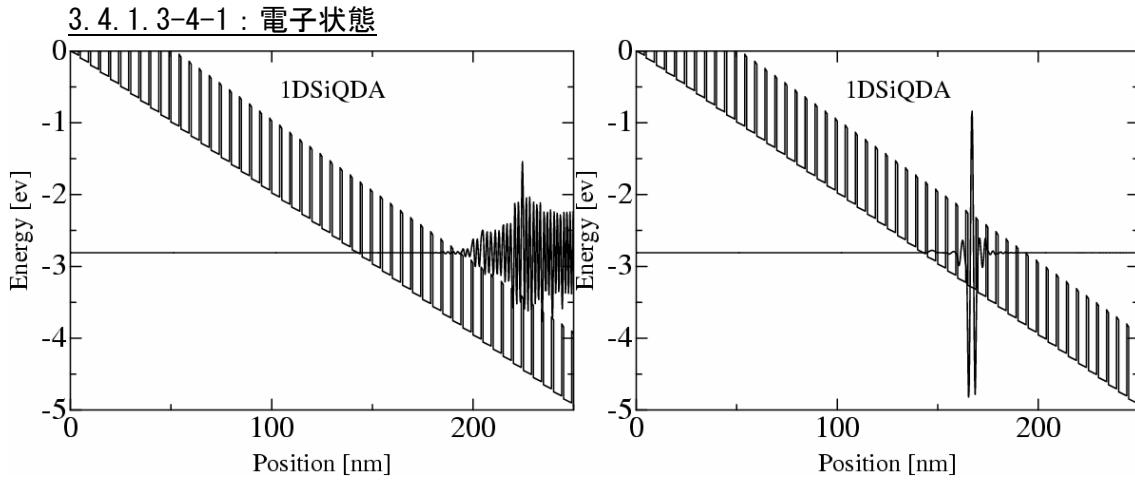

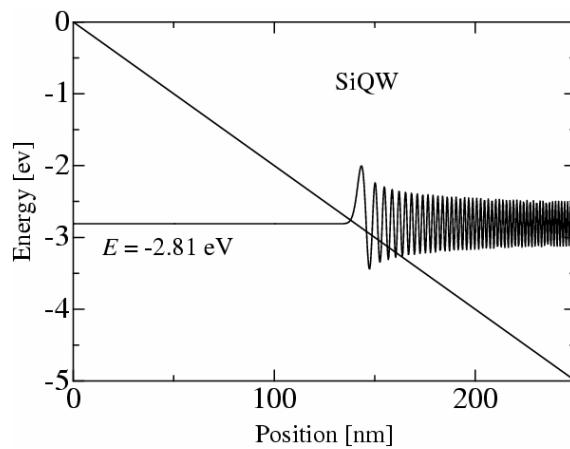

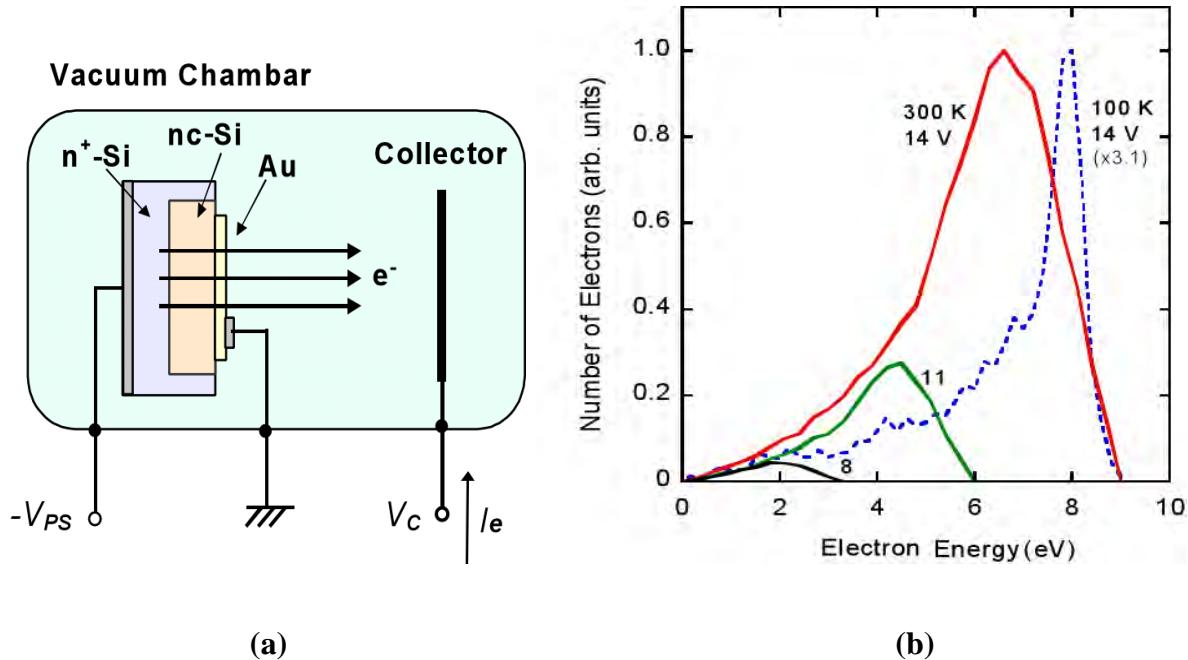

弾道性冷電子放出の機構究明と高効率化を検討し、実験的・理論的に、ナノ結晶シリコン間の多重トンネルによって電子が弾道化し真空に放出されるというモデルの検証を行った。弾道性冷電子放出の物理機構に関しては、ナノシリコンドットがトンネル酸化膜によって1次元的につながれている構造の理論解析を行い、(a) ネオシリコン中の音響ひずみポテンシャル強度がバルクシリコンに比べて減少すること、(b) 電子のミニバンド下端において電子のフォノン放出によるエネルギー損失が大きく抑制されることなどを解明した。また、ナノシリコンからの放出電子のエネルギー分布測定を行い、高エネルギー領域での電子が弾道的に放出されていること、分布が非マクスウェル型となっていることを実証した。

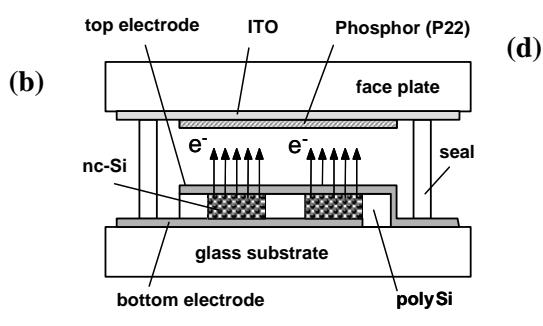

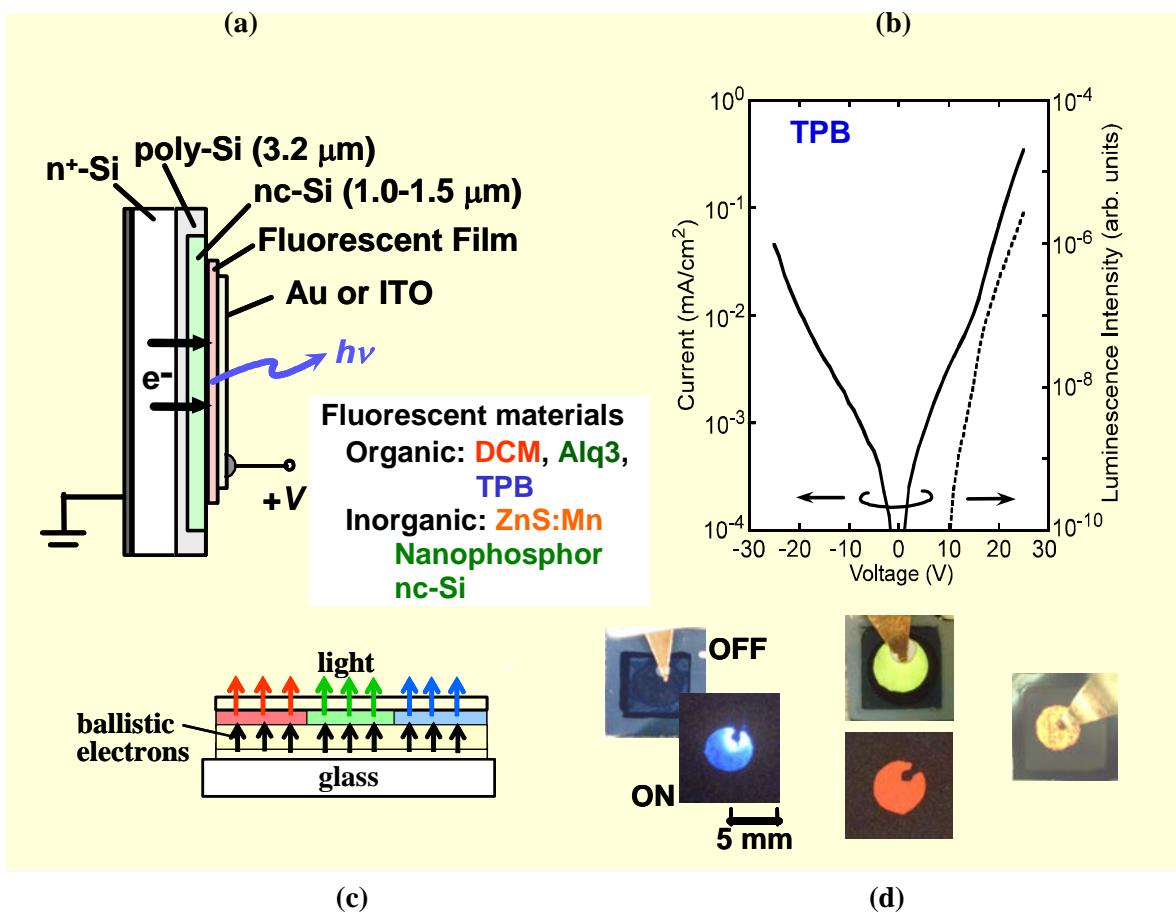

弾道性冷電子放出素子の大面積化については、石英ガラス基板での結果をふまえ、TFT用ガラス基板上に電子放出素子アレイを構成する低温プロセス技術を開発した。また、真空封止や真空維持などについても基礎技術を固めた。さらに、プラズマディスプレイ用ガラス基板を用いたプロトタイプの対角2.6インチ  $168 \times 126$  画素さらには7.6インチ  $336 \times 252$  画素のフルカラー薄型平面ディスプレイを試作し、単純マトリクス方式による動画表示を確認した。また、蛍光体として有機および無機の薄膜をナノ結晶シリコン層に堆積した弾道電子励起形の全固体発光素子を開発し、面発光動作を確認した。

### 4. 素子応用検討

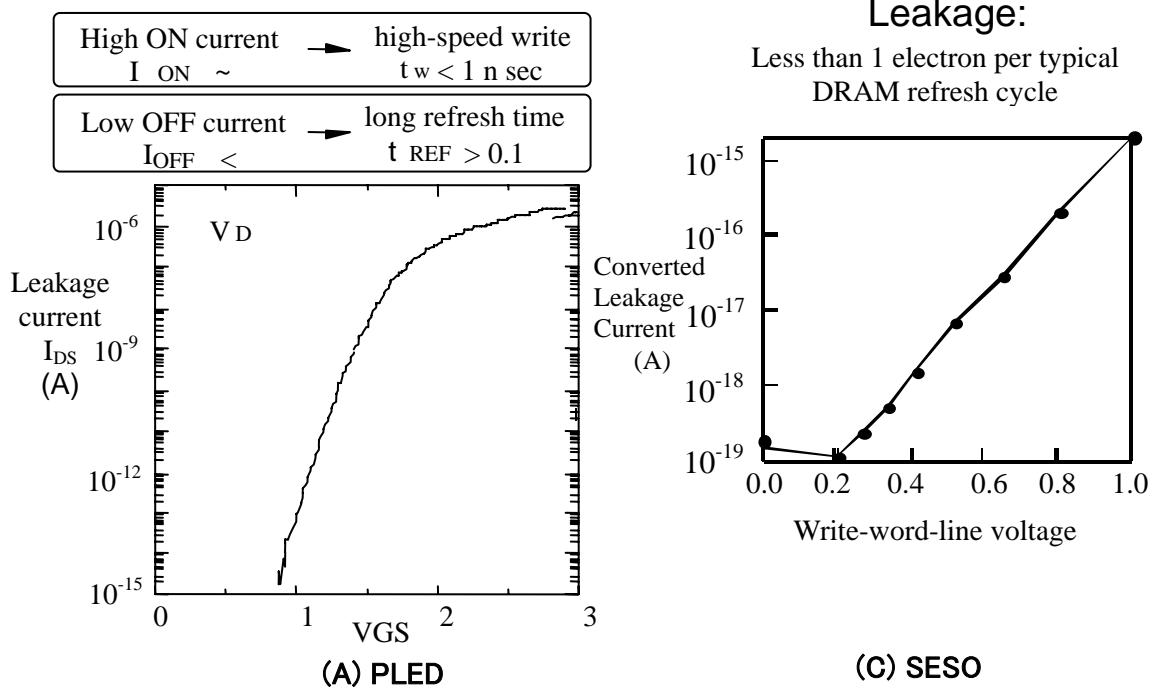

社会ニーズとネオシリコンが持つ特徴あるメリットに注目し、超低消費電力素子と高機能表示素子応用を検討した。モバイル機器用電子素子には高速性を失わず、超低消費電力化と不揮発性が求められている。ネオシリコンが持つクーロン遮蔽効果による高インピーダンス性と、ネオシリコンをナノ変位機構に組み合せた不揮発性を組み合わせて、超低消費電力不揮発性NEMSメモリの概念を提案し、その鍵となるフローティン両持ち梁のナノ変位機構、動作速度、素子のオンオフ比、消費電力などの特性予測をシミュレーションにより行うとともに、両持ち梁構造の試作・機械的特性の評価を行った。その結果、素子設計に必要なナノ領域での変位効果の特徴と構造最適化のガイドラインを明らかにするとともに、作製した梁の機械的双安定性を実証することが出来た。

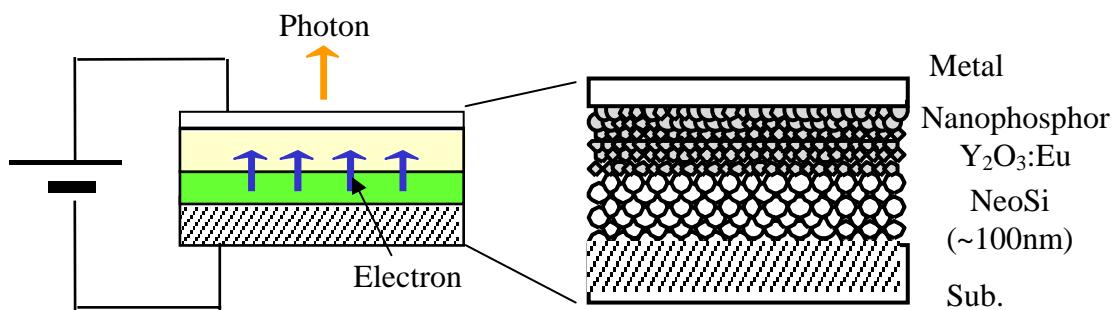

また、ネオシリコンからの弾道電子放出の特異性に注目し、弾道電子放出素子とナノ蛍光体を組み合せた、真空不要の平面ディスプレイの基本機能の検証を進めた。ナノ結晶シリコン膜低エネルギー電子照射によるナノ蛍光体の発光特性の評価を行ない、本応用の可能性実証を行った（上記3を参照）。

表1. 1 各要素技術に対する成果目標と最終成果のまとめ

|      |                                | 目 標                                                | 最 終 成 果                                                                                                                                                                                              |

|------|--------------------------------|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 構造制御 | ドット直径                          | 5 nm以下に制御                                          | 5 nm制御に成功<br>(部分的には3 nmを観測)                                                                                                                                                                          |

|      | ドット界面膜厚                        | 1 – 2 nmに制御                                        | 1 – 2 nm制御に成功                                                                                                                                                                                        |

|      | ドット密度                          | $10^{12} \text{ cm}^{-2}$ 程度の高密度化                  | $\sim 7 \times 10^{11} \text{ cm}^{-2}$ を達成                                                                                                                                                          |

|      | (ドット位置)                        | (2次元配列制御)                                          | 局所的な配列を観測                                                                                                                                                                                            |

| 機能制御 | バリスティック電子放出の制御と電子輸送・放出メカニズムの解明 |                                                    | <ul style="list-style-type: none"> <li>放出電子のNon-Maxwellianエネルギー分布観測と電圧による制御に成功</li> <li>電子・フォン分離とフォンストップバンドの存在の解明に成功。電子・フォン相互作用の減少を理論的に検証</li> <li>タイムオフライト実験により電子速度オーバーシュートを観測(ポーラスSi構造)</li> </ul> |

|      | ドット間相互作用の観測と制御                 | 静電相互作用(古典的)                                        | 隣接する2ドット間の静電相互作用によるクーロン電流振動のスイッチング現象                                                                                                                                                                 |

|      |                                | コヒーレント相互作用(量子論的)                                   | 隣接する2ドット間の波動関数結合による準分子状態を4.2 Kで観測に成功                                                                                                                                                                 |

| 応用展開 | バリスティック表面電子放出素子                | 高効率・フルカラー真空形平面ディスプレイの動作実証(ポーラスSi構造)および全固体面発光素子への展開 | <ul style="list-style-type: none"> <li>ナノ結晶ポーラシリコンBSD*のプロトタイプ素子動作成功 (*Ballistic electron Surface emitting Display)</li> <li>固体面発光素子の動作確認と多色化の成功</li> </ul>                                           |

|      | ナノエレクトロルミネッセンス素子               | ネオシリコンドット/ナノ蛍光体微粒子ハイブリッド構造エレクトロルミネッセンス素子の原理検証      | オックスフォード大/OXONICA社製ナノ蛍光体微粒子サンプルの特性を評価                                                                                                                                                                |

|      | ナノドット単電子素子                     | ナノポイントコンタクト型単電子トランジスタの室温動作実証                       | 室温クーロン電流振動の観測に成功                                                                                                                                                                                     |

|      |                                | 長保持時間ナノドットフラッシュメモリの原理実証                            | シリコン/シリコン窒化膜のデュアルメモリノード構造でデータ保持時間190日を達成                                                                                                                                                             |

|      | ナノエレクトロメカニカルメモリ                | ネオシリコンドット内包型ナノエレクトロメカニカルメモリ動作原理の実証                 | 微細キャビティ構造内の絶縁膜梁構造試作と両持振動子としての膜のメカニカル特性実証に成功                                                                                                                                                          |

### 1. 3 計画達成度・研究成果の意義・自己評価等

表1. 1にまとめた通り、本研究では、構造制御、機能制御、応用展開の要素技術ごとにマイルストーンを設定して研究を進めた。目標欄に記載したターゲットは、初期に設定したものの中間に中間評価での追加・修正を加えたものであり、それぞれかなりハードルの高いものであったと考えている。構造制御については、粒径、粒子間隔、粒子密度について数値目標をほぼ達成し、目標外であったドットの規則配列についても局所的に観測に成功した。機能制御については、中間評価時点での最大の課題であった弾道電子放出現象のメカニズム解明にほぼ成功し、電子放出効率向上に向けた構造最適化技術を確立した。また、ネオシリコンの大きな特徴であるドット間の相互作用解明についても、2ドット間の静電相互作用を観測したのみならず、予想していなかった量子力学的コヒーレント結合を観測するなど、目標を上回る成果が得られた。素子応用に関しては、研究スタート時点では、超高電流オンオフ比スイッチング素子、単電子および少数電子メモリ・ロジック素子、面電子放出素子、固体化積層発光素子など、かなり広範囲な素子応用を検討したが、プロジェクト後半では、弾道電子放出素子と高速・不揮発NEMS

メモリの2つに集中した。NEMSメモリについては、最終的なメモリ素子動作実証までには到達できなかったが、それぞれの素子コンセプトの実証をすることができた。以上のことから、初期に掲げた各目標はほぼ達成できたものと考えている。

## 2. 研究構想

### 2. 1 研究開始時の目標・計画・実施体制

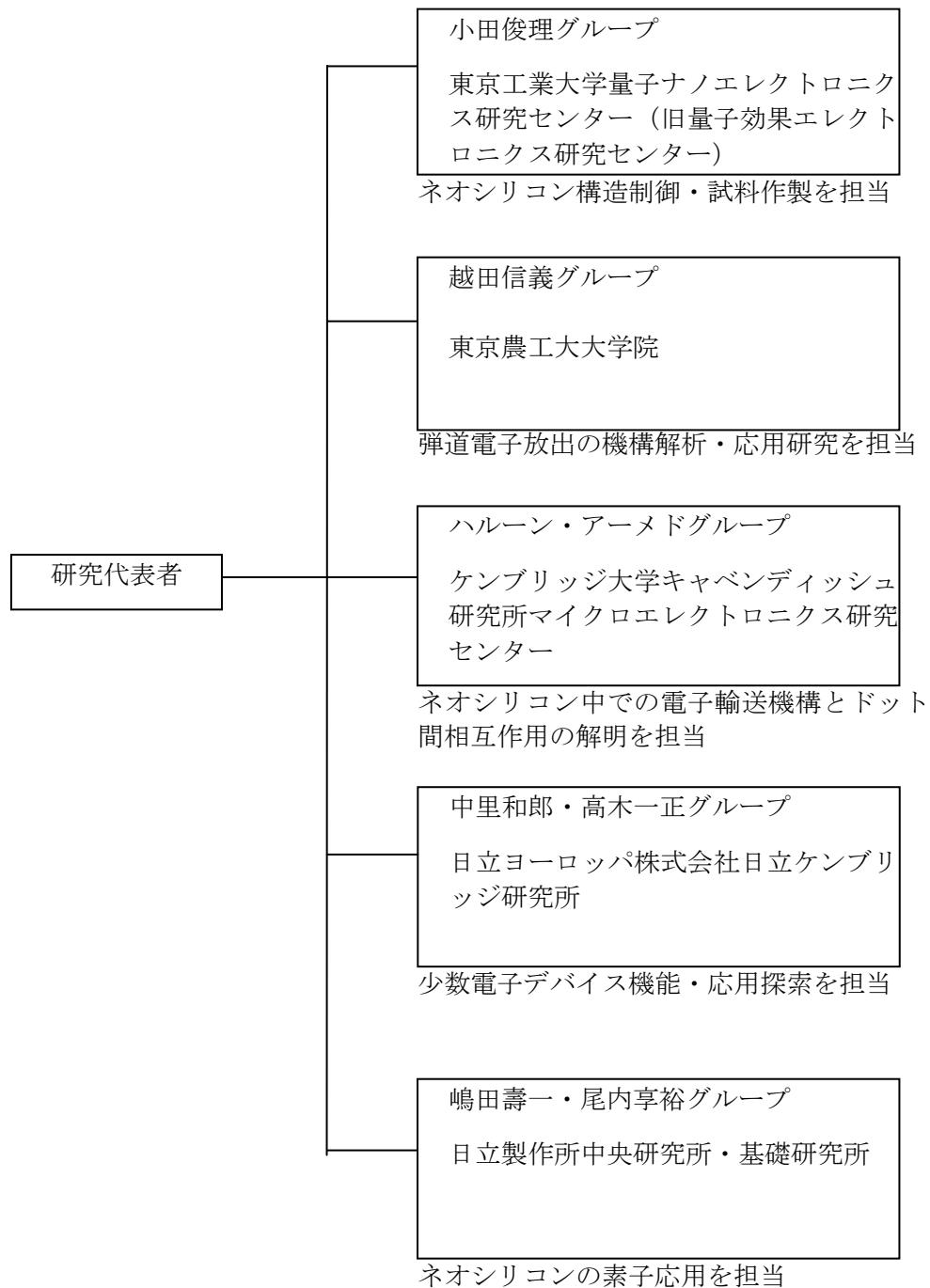

研究開始時において、本プロジェクトは「粒径3–5 nmのナノ結晶シリコン量子ドットを、間隔1–2 nmに制御して配列させた新材料「ネオシリコン」を開発し、その新機能と素子応用を探索する」と、構造作製技術開発から特性探索、更に素子応用検討までを含む大変スケールの大きな目標を掲げた。特に、素子応用としては、シリコンドット内局在電子とドット間の相互作用による電子輸送、光放出、電子放出などの新機能を集積化した、少数電子メモリ・ロジック素子をはじめとした高速演算・超低消費電力素子、不揮発性情報記録素子、高機能表示素子など、幅広い応用をターゲットとした。このような目標の下、プロジェクトを遂行するためには、それぞれの要素技術の専門家によるチームを編成し、各グループが相互補完的に研究を推進する体制を築く必要があった。そのため、まず、研究全体を以下の5つのタスクに分類した。

- (1) 粒径制御ナノ結晶シリコンの作製と極薄窒化膜の形成

- (2) 微細領域電気特性の評価

- (3) 光学特性、電子放出特性評価

- (4) 少数電子デバイス・回路応用

- (5) ネオシリコンの素子応用

これら5つのタスクは互いに密接に関連しており、有機的なフィードバックを図りながら進める必要がある。そのため、担当する研究グループは、個々のタスクの専門家であるだけでなく、他のタスク領域も十分オーバーラップしてカバーできる幅広い能力が要求された。このような観点から、以下の5研究機関をメンバーとしたチームを編成した。

- 東工大量子効果エレクトロニクスセンター [(1), (2), (3)を担当]

- ケンブリッジ大学キャベンディッシュ研究所 [(2)を担当]

- 東京農工大学 [(3)を担当]

- 日立ヨーロッパ社日立ケンブリッジ研究所 [(2), (4), (5)を担当]

- 日立製作所中央研究所・日立研究所 [(5)を担当]

### 2. 2 その後の研究計画の変更・新たな目標等

プロジェクト初期の2年間は、2. 1で述べた通り様々な応用展開の可能性を念頭に、各グループでネオシリコンの機能探索を幅広く行った。その一方で、各グループの研究が孤立してしまうことの無いよう、東京とケンブリッジでの全体会議と個別会議を定期的に行い、また各タスクの進捗状況に応じてグループ間の研究者の交流を活発に進めた。プロジェクト前半の議論と中間評価会議での結果を踏まえ、プロジェクトの折り返し時

点では、要素技術毎のマイルストーンと可能性の高い応用展開方向の絞込みを行い、前述の表1. 1にまとめたような最終目標を設定した。

特に、ネオシリコンの新機能として極めてユニークな弾道電子放出特性の検討を加速するため、中間評価会議後、日立ケンブリッジ研究所グループの主たる目標を、前半のナノシリコン単電子デバイス検討から、弾道電子放出機構の理論的解析にシフトし、東京農工大学グループとの連携を更に強化した。また、ケンブリッジ大学グループは、ネオシリコン本来の大きな特徴であるドット間の相互作用を明確にするため、前半の単電子輸送特性の評価から、2ドット間の静電相互作用・量子力学的相互作用の評価にターゲットを発展シフトさせた。更に、ネオシリコン応用素子として新たに提案したNEM Sメモリの研究を強化するため、日立グループと東工大グループの連携を特に強化し、定期的な個別会議を持つことで、高速・不揮発性メモリとしての可能性の検討と素子動作原理検討を同時に進めた。

### 2. 3 研究過程で得られた新しい発見

本研究では、ネオシリコン中の電子輸送機構の解明のために、チャネルの長さと幅を50 nm以下に制御した量子ポイントコンタクトトランジスタ(Q P C T)構造(縦型・横型)を駆使した。この素子のチャネル部分にネオシリコンの量子ドットを1個～数個配置することにより、ナノシリコンドットとその粒界の個々の特性を評価することが目的であったが、この評価手法からは様々な新現象の発見がもたらされた。

まず、第一は、縦型のQ P C Tにおいて、参考構造として作製したドットのない素子において、明瞭なコンダクタンスの量子化が観測された点が挙げられる。コンダクタンスの量子化現象は、それまで化合物半導体の2次元電子ガス系で盛んに研究されていたが、シリコン系では観測が困難で実験結果は皆無であった。この成果は、本プロジェクトの本来の目的外の成果ではあるが、シリコンにおけるバリスティック素子に対する理解と研究を大きく前進させるものであった。

第二には、ナノ結晶シリコン薄膜を用いて作製したQ P C T構造において、单一の粒界のトンネル障壁特性を評価することに成功し、それを発展させて「グレインバウンダリ制御技術」の可能性を実証した点が挙げられる。この発見は、粒界を最適化する2段階酸化プロセスの開発に繋がり、それによって室温動作単電子トランジスタの実現が可能となった。「グレインバウンダリ制御技術」は、ネオシリコン作製のみならず、TFT開発のパッシベーション技術への応用が大いに注目されており、ポリシリコン薄膜材料・デバイス分野からも招待講演を多数いただいている。

第三には、ネオシリコン2ドット間の静電相互作用を評価している中で、2ドット間のトンネル障壁が特に薄いケースでは、2ドット中の電子の量子力学的結合による結合・反結合状態が形成されていることを発見した点が挙げられる。2ドットの量子力学的結合は、先に化合物半導体構造で観測されていたが、観測温度は50 mK以下であり、また結合・反結合準位の間隔は数十μ eVと非常に小さかった。本研究では、この現象がシリコンで初めて観測され、しかも温度4.2 K、結合・反結合準位間隔～0.4 meVであることから、量子コンピュータの基本素子である量子ビットをシリコン中の電荷で実現するまでの大きな発見と考えている。

## 2. 4 研究項目ごとの達成度

### ① ネオシリコン構造作製・制御

研究開始時に提案した「ネオシリコン」の概念は、「粒径 3–5 nm のナノ結晶シリコン量子ドットを、間隔 1–2 nm に制御して配列させ、そのドット間の相互作用を利用する」ものであった。これに対し、本研究では、VHF プラズマとパルスガス供給を組み合わせたオリジナル技術を世界に先駆けて開発し、最小粒径 5 nm、粒径分散 ± 1 nm と非常に均一性の良いナノ結晶シリコンドットを作製することに成功した。パルスガスの条件次第では、更に小さい粒径 3 nm のドットが部分的に形成されていることも観測されている。また、ドット間隔の制御については、低温ラジカル窒化技術を開発して、厚さ 1 ~ 2 nm の均一な窒化膜をシリコン量子ドットの表面に形成する方法を開発するとともに、窒化後の特異なトラップ準位の特性を明らかにした。更に、中間評価時点で課せられたマイルストーンであるドットの高密度化についても、従来のシリコン加工技術とは全く異なる分散溶液を用いた方法を開発することで、約  $7 \times 10^{11} \text{ cm}^{-2}$  の高密度化を達成し、目標をほぼクリアした。以上のことから、「ネオシリコン構造作製・制御技術の開発」に関しては、初期・中間期の数値目標をほぼ達成できたと考えている。

### ② ネオシリコン電気特性評価

本項目では、前述のようにプロジェクト前半において、単電子帶電効果の制御と単電子素子の動作温度向上に注力し、ナノ結晶シリコンドットとその粒界の構造・特性をエンジニアリングする手法を確立し（特許化済）、単電子トランジスタの室温動作へと繋げた。またナノ結晶シリコンドットへの電荷蓄積の量子化を室温で観測すること、および電荷蓄積時間を 190 日とすることに成功し、現在ポストフラッシュメモリとして期待の高いナノドットメモリの実現に向けた重要な成果を生み出した。また、プロジェクト後半においては、ネオシリコンの大きな特徴であるドット間の相互作用を解明・制御することに注力し、2 ドット間の静電相互作用と量子力学的な結合による準分子状態の形成（シリコンで世界初）の観測に成功した。これらは、ドット間トンネル膜構造の詳細な制御によって初めて達成されたものであり、基礎科学上でも応用上でも極めて価値の高い成果と考えている。また、1 ドット内に蓄積された電子数の量子化とその時間変化を AFM 技術により直接観測することにも成功しており、全体を通して初期の目標を上回る成果が得られたと考えている。

### ③ ネオシリコン発光・電子放出特性評価

本項目においては、弾道性冷電子放出現象という応用上極めて重要なネオシリコンの機能が観測され、その物理的機構解明と放出効率向上が最大の目標となった。これに対し、放出電子のエネルギー分布とその温度依存性測定、飛行時間法による電子ドリフト過程の評価、更に 1 次元ナノドットアレイにおけるフォノン散乱の理論解析などを行い、ナノ結晶シリコン層内において電子のエネルギー緩和過程が抑制され、準弾道的に表面から放出されるというモデルを裏付けることができた。また、それに基づいてナノ結晶シリコン層のナノ構造制御を行い、弾道電子放出の効率と安定性を向上する上でカギと

なる要素技術を固めることができた。弾道電子輸送の理論解析については、高電界領域での定量的評価が今後の課題として残っているものの、ナノ結晶シリコン層内のフォノンスペクトルと電子フォノン相互作用がバルクシリコンと大きく異なることを解明できており、初期の目標を十分上回る成果が得られたものと考えている。

#### ④ 素子応用検討

前述のように、ネオシリコン素子応用としては、面電子放出素子、固体化積層発光素子、大気圧動作電子放出素子、超低オフ電流高オンオフ比高速動作スイッチング素子、単電子および少数電子メモリ、NEMS メモリを提案・検討した。これらの中で、特に、弾道性冷電子放出素子と NEMS メモリは、ネオシリコンの新機能を活かしたユニークなコンセプトであり、その原理実証とともに特許化を行うことができた。

弾道性冷電子放出素子については、上述の機構解明と平行して、ポーラスシリコン構造を用いて、(1) ガラス基板上に電子放出素子アレイを構成する低温プロセス技術の開発、(2) 真空封止や真空維持基礎技術の開発、(3) プロトタイプの対角 7.6 インチ 336×252 画素のフルカラー薄型平面ディスプレイ試作・動作確認、を達成することができた。さらに、有機・無機計蛍光体薄膜をナノ結晶シリコン層に堆積した弾道電子励起形の全固体発光素子を開発し、面発光動作をすることができ、ネオシリコンの弾道電子放出特性を、真空だけでなく固体素子への展開することが可能であることを実証し、初期の目標を十分上回る成果を達成したと考えている。

一方、NEMS メモリ素子においては、最終的なメモリ動作の実証までには至らなかったが、その鍵となる  $S_iO_2$  両持ち梁構造の試作に成功し、その機械的双安定性を実証できたことに加え、3 次元シミュレーションを駆使して NEMS メモリの動作解析と設計手法を確立できたことは大きな成果であり、総合的には目標達成を果たせたと考えている。

### 3. 研究成果

#### 3. 1 チーム全体の成果

本研究では、提案した「ネオシリコン」という新機能材料の概念の実証に向けて、研究全体を、①構造作製・制御技術、②電気特性制御、③発光・電子放出特性制御、④素子応用探索、の4項目に分け、それぞれにオリジナリティの高いマイルストーンを設定して研究を進めた。それぞれの項目での研究成果の詳細については、3. 2節以後で述べるが、全体の成果は以下のようにまとめられる。

- ① 構造作製・制御：粒径、粒子間隔、粒子密度について数値目標をほぼ達成し、目標外であったドットの規則配列についても局所的に観測

- ② 電気特性評価：ドットでの単電子クーロン遮蔽効果と電荷蓄積量子化を室温で観測。更に2ドット間の静電相互作用とコヒーレント結合を4. 2 Kで観測。

- ③ 発光・電子放出特性制御：弾道電子放出現象の観測と、そのメカニズムの実験的・理論的解明に成功。更に放出効率向上に向けた構造最適化技術を構築。

- ④ 弹道性冷電子放出素子のプロトタイプ開発に成功。高速・不揮発N E M Sメモリの提案と原理検証に成功。

以上の成果は、論文発表101件、学会発表154件、特許6件として発表され、その内、招待論文9件、招待講演19件と内外で大きな注目を受けた。いずれも単独の研究成果としてきわめてオリジナリティが高い仕事であるが、これらは、本プロジェクトが材料から素子応用までを総合的に捕らえ、各々が建設的に（時には批判的に）にフィードバックをしながら切磋琢磨し合うことで初めて達成できたレベルの高い成果であることを特筆したい。これらの成果が有機的に組み合わさることにより、最近になって我々の「ボトムアップシリコンナノエレクトロニクス」というシリコンナノデバイス・システムに対する新しいアプローチが次第に評価されるようになって来ている。このようなボトムアップ技術と従来のトップダウン技術の融合は、従来の微細加工技術トレンドとは異なる新たなオートレンド技術を開く可能性が大いにあり、その先導性は非常に高い。一つの新しい技術潮流の芽を生み出しつつある状況であると自負しており、今後、更なる発展に注力をしたい。

また、本プロジェクトは国際的産学連携を特徴としており、従来の枠組みでは極めて難しい半導体の基礎研究と応用研究を同時に実行することができた。企業の立場から見ると、本研究内容は材料基礎研究として捉えられ、大きなリソースの投資が難しいテーマであるが、東工大、農工大、ケンブリッジ大のプロフェッショナルなグループがチームを組み、それに企業の基礎研究所として先端を走る日立ケンブリッジ研究所と、応用研究を担当する日立製作所が参画することで、基礎研究の段階から、大学と企業が一体となって研究を進め、目標設定時から応用の可能性とその意義について企業から大学にフィードバックを掛けるとともに、基礎的研究成果をオンラインに近い状況で活用することが出来、相乗効果の極めて高い研究運営であったと考えている。

### 3. 2 ネオシリコン作製グループ（東京工業大学）

（東京工業大学 小田俊理、水田博、畠谷成郎、土屋良重、宇佐美浩一、新井健太、S. Banerjee, B. J. Hinds, 趙新為、西口克彦、黄少雲、M. A. Salem, 山中崇行、大町純一、中村暦、小澤治、高居康介、中務琢也、田中敦之、川田善之、池澤健太、百々信幸、R. T. Tung）

#### 3. 2. 1 ネオシリコン構造制御

##### 3. 2. 1. 1 はじめに

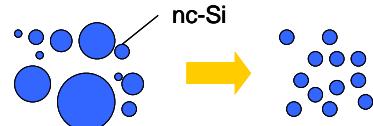

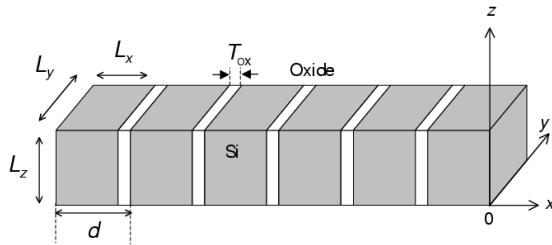

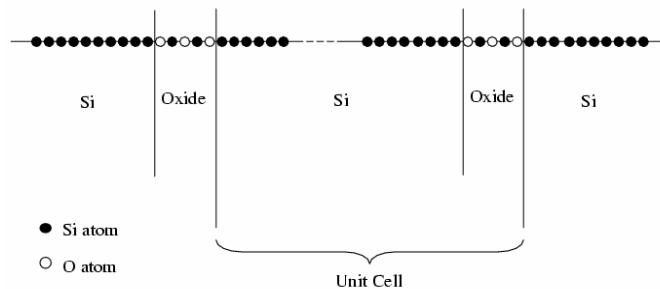

半導体微細構造を作製する方法は、リソグラフィとエッチングによるトップダウン技術により進展してきたが、リソグラフィ技術の限界が取りざたされる中、最近は、原子レベルで制御する結晶成長技術によりクラスター やナノ結晶を形成するボトムアップ技術によりナノ構造を作製する研究が非常に注目されている。ナノ結晶シリコンについては、もともとアモルファスシリコン太陽電池の高効率化のためにアモルファス膜中に微結晶シリコンを混入したり、微結晶シリコン薄膜を用いたりするという目的で多くの研究がなされてきたが、最近は、このナノ結晶シリコン1つ1つを量子ドットとしてとらえ、粒径数 nm のドットで発現する量子効果により高効率化された発光デバイスや、単電子トランジスタや単電子メモリといった新しい原理で動作する電子デバイスへの応用も盛んに研究されている。「ネオシリコン」を創製することは、ある程度自然現象を利用しているがゆえに制御が難しいとされるボトムアップ技術により作製したナノ結晶シリコンの集合体の制御にあえてチャレンジし、ボトムアップ形成ナノ結晶シリコンをシリコンナノデバイスの構成要素として確立することにより、デバイス応用、およびデバイス動作の安定化に大きな寄与をもたらすことである。技術的に重要なポイントとしては、1) ナノ結晶シリコンドットの形状、粒径の制御、2) ナノ結晶シリコンドット間の相互作用の制御、3) ナノ結晶シリコンドットの位置制御、の3点を挙げることができる（図3.2.1.1）。

このような研究背景に基づき、我々のグループでは、シランガスのプラズマ分解により形成したシリコンのラジカルを原料としてナノ結晶シリコンを気相成長する方法を開発し、その技術を発展させることにより、粒径の均一化、サイズの縮小化を試みた（3.2.1.2）。ドット間の相互作用の制御という観点からは、形成したナノ結晶シリコンの表面の物理的性質を制御し、光学特性の評価をおこなった。とくに、表面に直接窒化膜を形成する方法を新たに確立した（3.2.1.3）。また、電子デバイスに応用する際の基礎となるナノ結晶シリコンドットの集合体における電荷保持特性を調べた（3.2.1.4）。ドットの位置制御については、溶液を用いた方法に

##### 1) ナノ結晶シリコンドットの形状、粒径の制御

##### 2) ナノ結晶シリコンドット間の相互作用の制御

##### 3) ナノ結晶シリコンドットの位置制御

図3.2.1.1 ネオシリコン創製の技術的なポイント

よりドットの高密度集積化を目指した(3.2.1.5)。本節ではこれらの研究について5年間の研究成果を報告する。

### 3.2.1.2 ナノ結晶シリコンドットの粒径制御

#### 3.2.1.2-1 VHFパルスプラズマプロセス

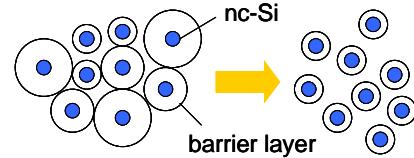

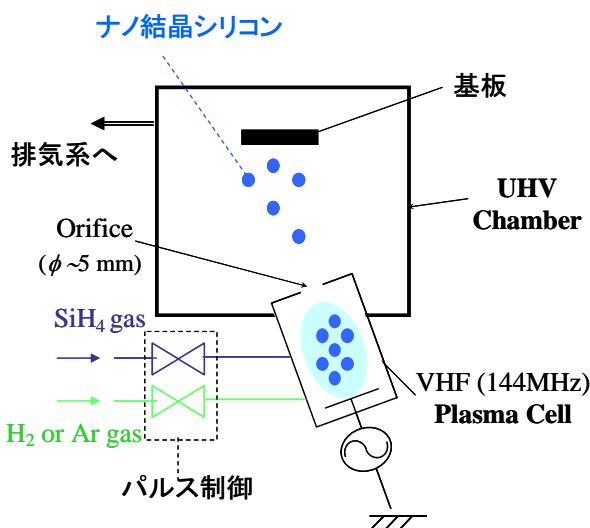

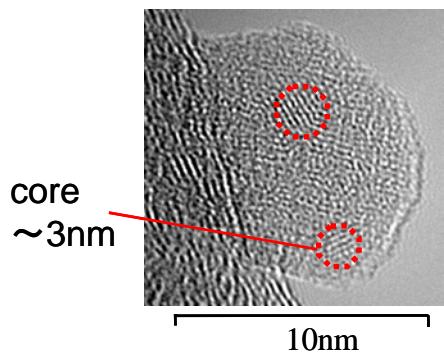

本研究で用いたナノ結晶シリコン堆積装置の模式図を図3.2.1.2に示す。ナノ結晶シリコンドットは、シランガスを原料としてプラズマセル内で形成し、オリフィスを通して堆積室内の基板上に堆積する。周波数144MHzのVHFプラズマはラジカル発生効率が高いのでナノ結晶シリコンドットの形成に適している。比較のために13.56MHzプラズマでも実験を行ったが、ナノ結晶シリコンドットの堆積速度は2桁以上遅くなる。プラズマセルの温度は100°Cであるが、ラジカルの化学エネルギーのため無双晶で単結晶のナノ結晶シリコンドットを得ることができる。シリコン超微粒子の形成法としては他にもガス蒸着法やスパッタ法がある。しかし、シランガスを原料とするプラズマ分解法がこれらの方針と本質的に異なるのは水素ラジカルを発生することである。シリコンクラスターが結晶成長する過程で、表面ダングリングボンドは常に水素原子によって終端されている。そして、ナノ結晶シリコンドットの結晶成長は水素含有シリコンラジカルの堆積と水素ラジカルによるエッチングの平衡により制御された形で進行する。プラズマ中の各種ラジカルの存在比は、圧力、ガス滞在時間、高周波電力、周波数などの外部パラメータで決まる。図3.2.1.3にはこの方法により作製されたナノ結晶シリコンドットの透過型電子顕微鏡(TEM)写真を示す。電子ビームとシリコン原子との干渉により形成した格子像が観測され、良質な単結晶球ができていることが分かる。シランガス中に含まれる水素がシリコン表面を被覆して理想的な結晶成長条件が実現できているものと思われる。この方法の大きな特徴は、室温でどんな基板上にも堆積できることである。

図3.2.1.3 ナノ結晶シリコンのTEM像

図3.2.1.2 ナノ結晶シリコン堆積装置の模式図

ナノ結晶シリコンドットの結晶成長は水素含有シリコンラジカルの堆積と水素ラジカルによるエッチングの平衡により制御された形で進行する。プラズマ中の各種ラジカルの存在比は、圧力、ガス滞在時間、高周波電力、周波数などの外部パラメータで決まる。図3.2.1.3にはこの方法により作製されたナノ結晶シリコンドットの透過型電子顕微鏡(TEM)写真を示す。電子ビームとシリコン原子との干渉により形成した格子像が観測され、良質な単結晶球ができていることが分かる。シランガス中に含まれる水素がシリコン表面を被覆して理想的な結晶成長条件が実現できているものと思われる。この方法の大きな特徴は、室温でどんな基板上にも堆積できることである。

### 3.2.1.2-2 ナノ結晶シリコンドット粒径制御技術

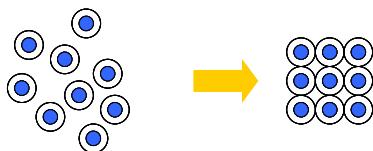

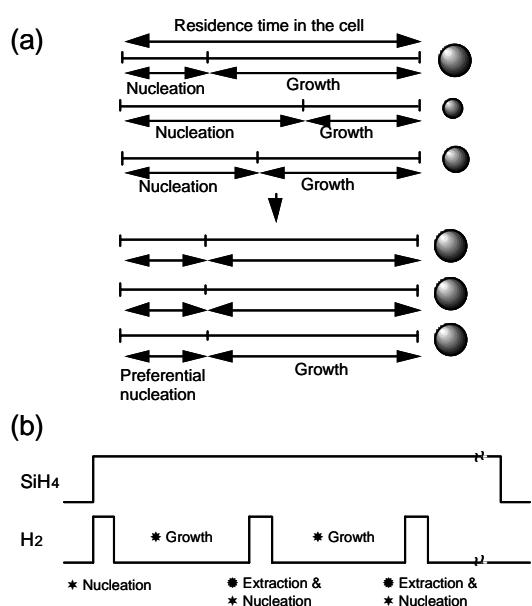

水素ラジカルはシリコン微結晶核の発生を促進するという実験結果と、量子ドットの粒径を均一にするためには核形成と結晶成長を時間分離すればよいとの仮説(図

図 3.2.1.4 均一粒径分布への指針

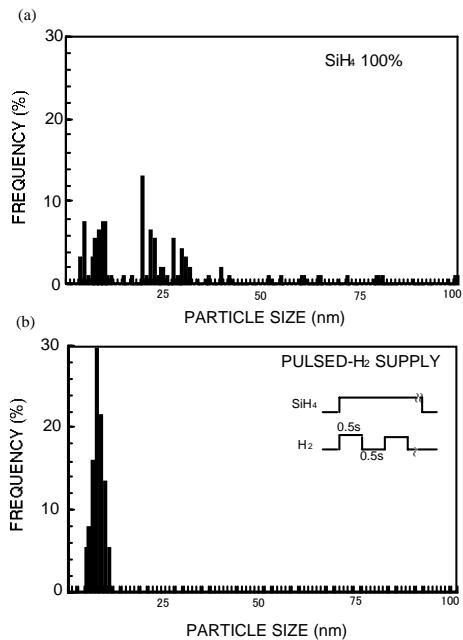

図 3.2.1.5 生成したナノ結晶シリコンの粒径分布(a)水素添加なし(b)水素添加あり

3.2.1.4(a))に基づいて、シランガスプラズマ中に水素ガスパルスを導入する方法(図3.2.1.4(b))により、粒径 8 nm、分散 1 nm という均一な分布のナノ結晶シリコンドットを形成することができた(図 3.2.1.5)。

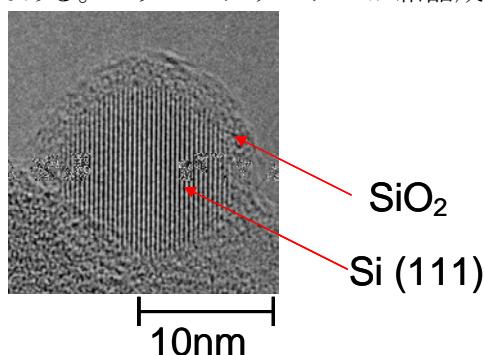

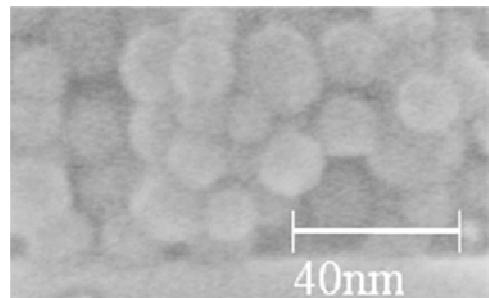

また、アルゴン添加することにより、ラジカル発生効率を 2 枠増加し、堆積速度が大幅に向上することを見いだした。アルゴンプラズマ中にシランガスパルスを添加する方法により、平均粒径 6 nm のナノ結晶シリコンドットを  $10^{12} \text{ cm}^{-2}/\text{h}$  の速度で形成できることを明らかにした。シランガスパルスの立ち上がり部分では、核形成に寄与する短寿命ラジカルが多く存在するのに対して、立ち上がり以外では結晶成長に寄与する長寿命ラジカルの量が相対的に多いため、パルスプラズマにより、粒径の単分散化が実現できるものと考えられる。シリコン基板上に堆積したナノ結晶シリコンの断面走査型電子顕微鏡(SEM)写真を図 3.2.1.7 に示す。粒径がそろったナノ結晶シリコンドットが堆積されている様子がわかる。

上記の実験結果に基づき、シラン-水素-アルゴンの 3 種のガスを用いて、プラズマ条件、パルス条件を変化させ、更なる粒径縮小化を目指している。図 3.2.1.8 は、アルゴンプラズマ中に、シラン-水素混合ガスパルスを導入

図 3.2.1.7 堆積したナノ結晶シリコンの断面 SEM 像

する方法により作製したドットの TEM 像である。全体の平均粒径が約 6 nm で、その内部にサイズが約 2-3nm の結晶のグレインをいくつか含むドットが観測された。この結果は、気相中での更なる粒径縮小化の可能性を示唆している。プラズマ内部で核形成の促進とラジカル発生効率の増大が同時に起こることにより、多量のサイズが小さいナノ結晶シリコンが生成し、衝突が起りやすくなつたために生じたものであると考えられる。

### 3.2.1.3 ナノ結晶シリコンドットの表面制御

#### 3.2.1.3-1 ナノ結晶シリコンの表面酸化

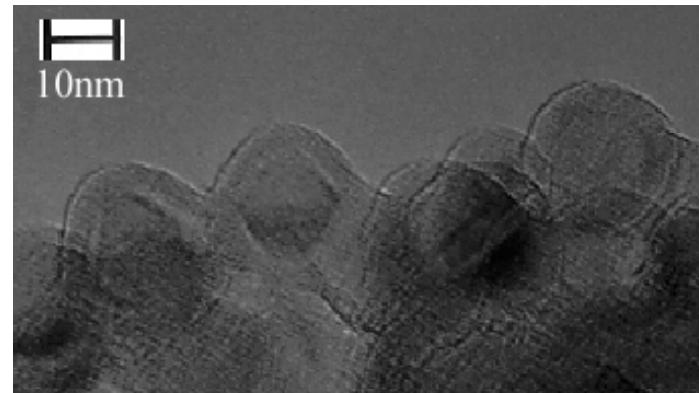

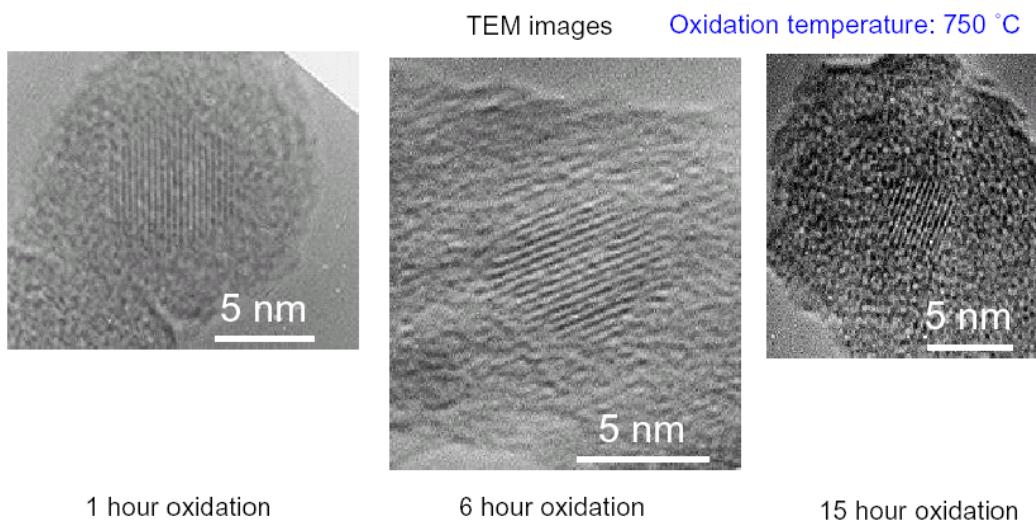

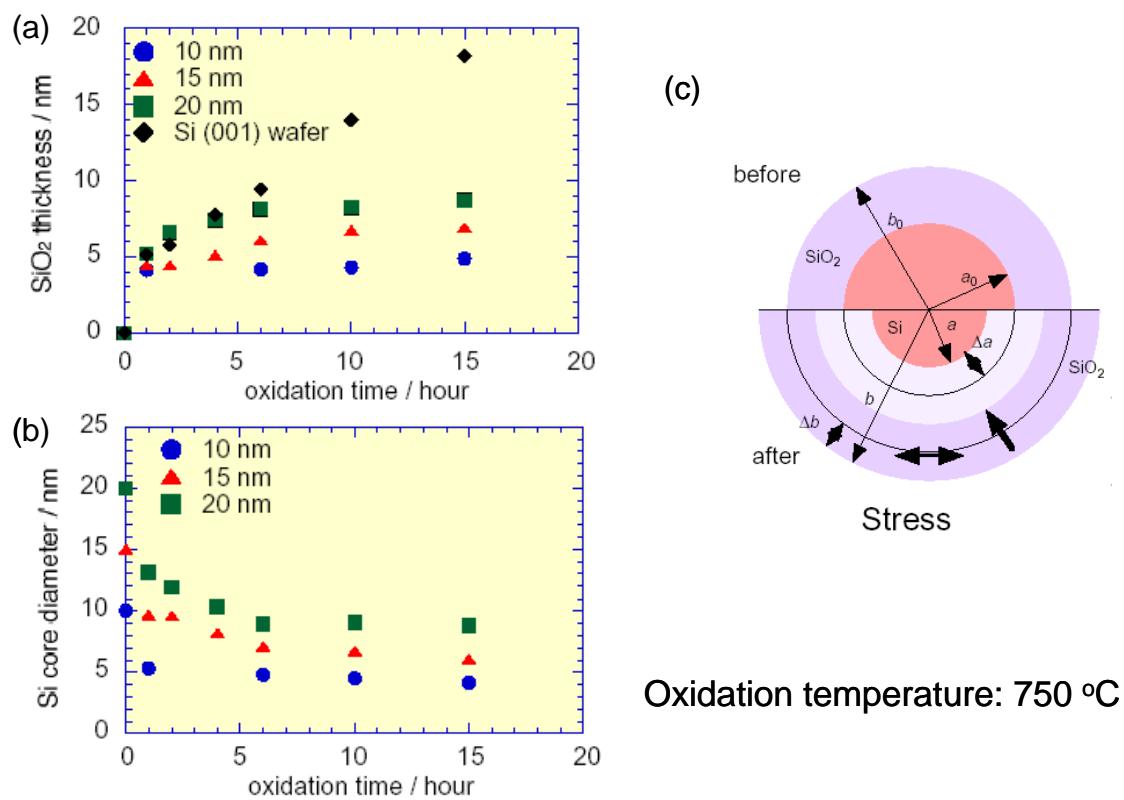

表面に酸化膜を形成した集積化ナノ結晶シリコンドットの TEM 写真を図 3.2.1.9 に示す。非常に均一な厚さの酸化膜がナノ結晶シリコンドットを覆っている様子が観測されている。酸化時間を長くしていくと表面が徐々に酸化され、ドットの粒径が小さくなつていく様子が図 3.2.1.10 から良くわかる。図 3.2.1.11(a)、(b) は 750 °C 酸化において、酸化時間に対して表面酸化膜厚、およびナノ結晶シリコンコアの直径の変化をプロットした図である。ナノ結晶シリコンドットの酸化では、Si 基板と比較して酸化速度が大幅に減少することが明らかとなった。また、750 °C においては、酸化が自然に停止するセルフリミティング現象が観測された。このセルフリミティング現象を利用し、粒径のはらつきがほとんどない直径約 4 nm のナノ結晶シリコンドットを再現性良く作製することができる。また、このセルフリミティング現象については、ナノ結晶シリコンドットは超微小な球形であることから、酸化過程において、酸化膜中に働く引張り応力と Si/SiO<sub>2</sub> 界面に働く圧縮応力のストレス効果として説明することができる(図 3.2.1.11(c))。

図 3.2.1.8 Ar-SiH<sub>4</sub>-H<sub>2</sub> により作製したドットの TEM 像

図 3.2.1.9 表面が酸化されたナノ結晶シリコンドット堆積膜の TEM 像

図 3.2.1.10 表面酸化によるナノ結晶シリコンドットの粒径変化の TEM による観測

図 3.2.1.11 酸化時間に対する表面酸化膜厚(a)、およびのナノ結晶シリコンコアの粒径(b)の変化 (c)ナノ結晶シリコン酸化メカニズム

### 3.2.1.3-2 表面酸化ナノ結晶シリコンドットの光学特性

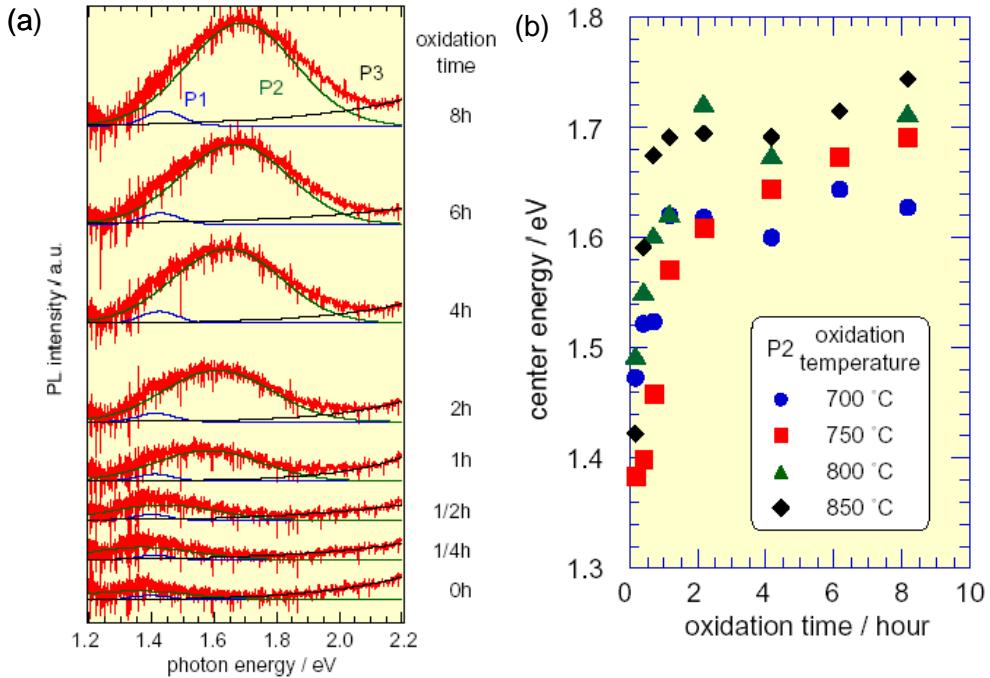

表面酸化したナノ結晶シリコンからは室温で可視光発光が観測される。図3.2.1.12(a)はコア粒径の異なる表面酸化ナノ結晶シリコンドットからの発光スペクトルである。ピーク分離後の図中P2のスペクトルが、ナノ結晶シリコン由来の発光と考えられる。

図 3.2.1.12 (a) 表面酸化ナノ結晶シリコンドットの発光スペクトル

(b) 酸化処理温度が異なる試料の酸化時間に対するピークシフトの違い

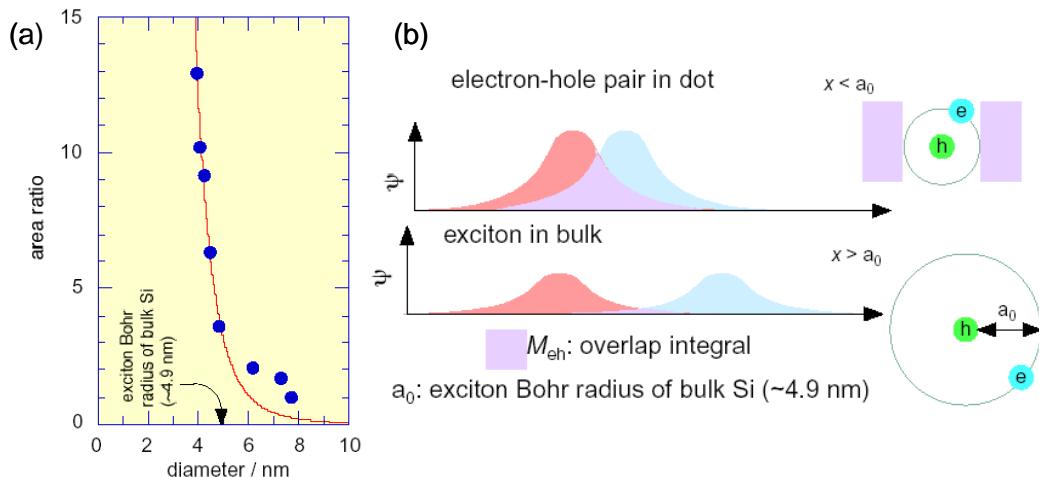

えられる。粒径が小さくなるにしたがって発光スペクトルのピーク位置がブルーシフトしており、これは量子閉じ込め効果に伴うバンドギャップの拡がりに対応していると考えられる。また図3.2.1.12(b)に示すように、酸化処理温度の違う試料においては、粒径の縮小化に伴うレッドシフトも観測されており、これはストレス効果によるものと考えられる。図3.2.1.13(a)には、粒径と発光強度の関係を示すが、ドットの直径がバルクSiにおける励起子のボーラ半径の2倍よりも小さくなる6 nm以下になると、発光強

図 3.2.1.13 (a) ナノ結晶シリコンドット粒径と発光強度の関係 (b) 発光強度増大のモデル

度の急激な増大が観測されることが分かった。これは図 3.2.1.13(b)に示したように、粒径の縮小化に伴う擬似直接遷移的な発光メカニズムへの移行が起こったことによる発光強度の増大と考えることができる。

### 3.2.1.3-3 ナノ結晶シリコンドットの表面窒化

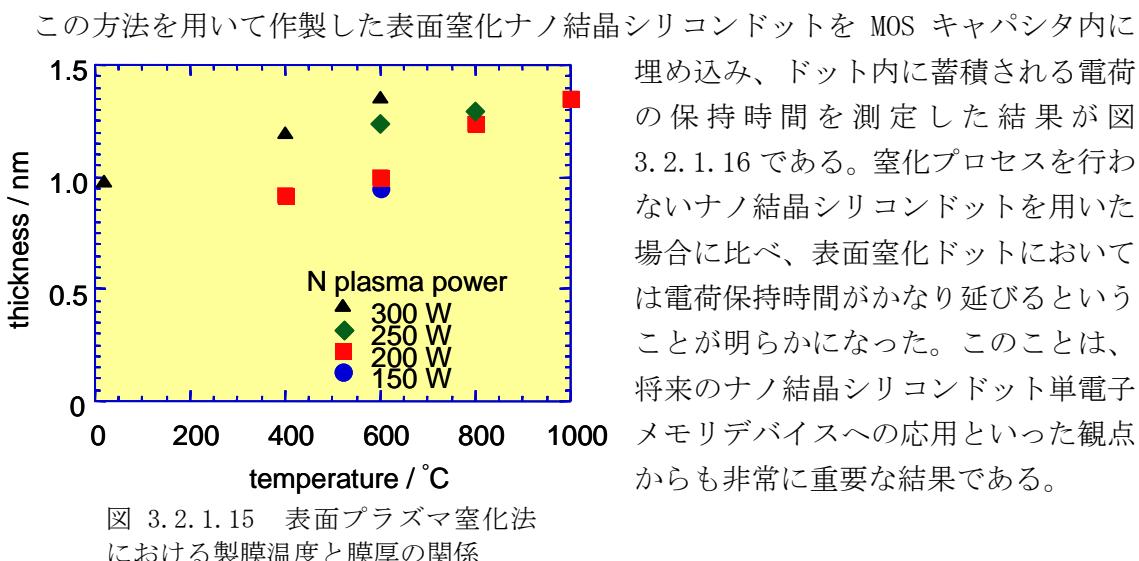

シリコン窒化膜は、シリコン酸化膜よりもバンドギャップが小さいため、ドット間の電子トンネル障壁膜として用いた場合、低電圧でより大きなトンネル電流を得ることができる。本研究では、窒素ラジカルによる直接窒化法をもついて、ナノ結晶シリコン表面に窒化膜を形成するプロセスを確立し、表面窒化シリコンドットの電荷蓄積能の評価をおこなった。図 3.2.1.14 は窒化処理チャンバーの模式図で、このチャンバーはナノ結晶シリコン堆積用のチャンバーと直接つながっているため、大気暴露により影響がなく *in situ* で窒化膜を形成することができる。図 3.2.1.15 には、製膜時間一定の条件下での製膜温度と膜厚の関係を示す。いずれの条件においても窒化膜の膜厚 1.5 nm 以下であり、温度依存性も小さいことから、セルフリミティングのメカニズムが示唆される。これに対して、プラズマパワーの変化に対する膜厚の変化は比較的顕著であり、プラズマ発光スペクトルとの対応を考慮すると、原子状窒素が窒化膜の形成に大きく寄与しているということが分かる。

図 3.2.1.14 表面窒化チャンバーの模式図

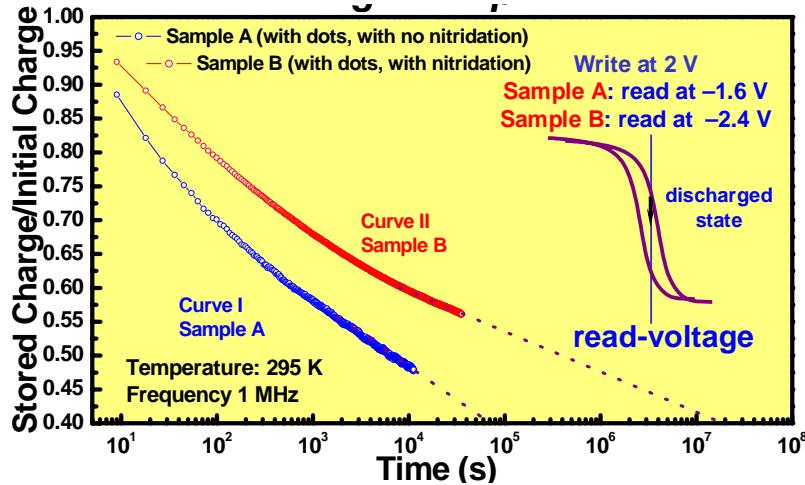

この方法を用いて作製した表面窒化ナノ結晶シリコンドットを MOS キャパシタ内に埋め込み、ドット内に蓄積される電荷の保持時間を測定した結果が図 3.2.1.16 である。窒化プロセスを行わないナノ結晶シリコンドットを用いた場合に比べ、表面窒化ドットにおいては電荷保持時間がかなり延びるということが明らかになった。このことは、将来のナノ結晶シリコンドット単電子メモリデバイスへの応用といった観点からも非常に重要な結果である。

図 3.2.1.16 表面プラズマ窒化ナノ結晶シリコンドットを用いた MOS キャパシタメモリにおける電荷保持時間の測定結果

### 3.2.1.4 走査プローブ顕微鏡によるナノ結晶シリコンドットの帯電状態の観測

#### 3.2.1.4-1 原子間力顕微鏡(AFM)による表面電荷状態の観測

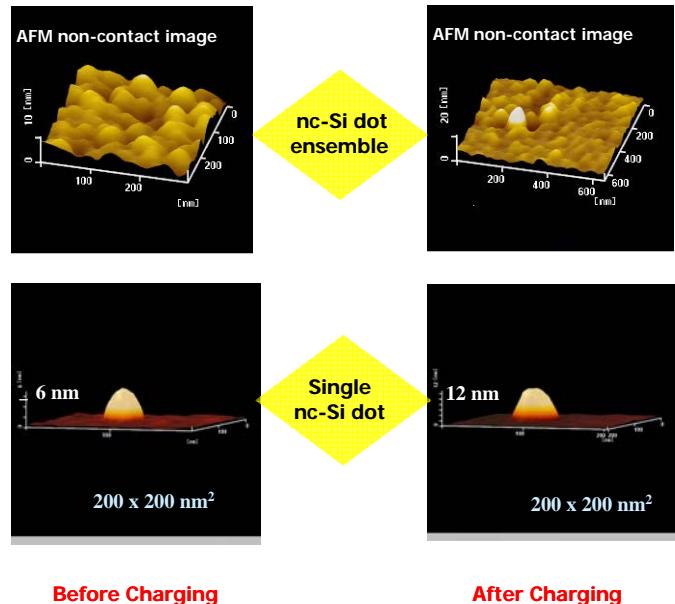

ナノ結晶シリコンドットに蓄積された電荷の振る舞いについては、デバイス応用上興味深い問題である。そこでナノ結晶シリコンドットを堆積した膜の表面の帯電状態について、走査プローブ顕微鏡を用いて調べた。図 3.2.1.17 は、探針に電圧をかけることにより、ドット表面の帯電状態を変化させる前後の、同じ位置での AFM 像である。通常の AFM では表面の形状像が得られるが、表面に電荷が存在する場合には、AFM の探針が静電気力の影響を受けるため、通常の形状像とは異なった像が得られる。帯電前後の像の差と、実際にドットに蓄積されている電荷量との関係について、従来のモデルを改良したドットと探針の幾何学的形状を考慮した新しい計算方法により、ナノ結晶シリコンドットの集合体に蓄積された電荷量を見積もることに成功した。

図 3.2.1.17 AFM 探針に電圧を印加する前後の AFM 像。上がアンサンブルの場合で下が單一ドットの場合

### 3.2.1.4-2 ケルビンプローブ顕微鏡(KFM)による表面電荷状態観測

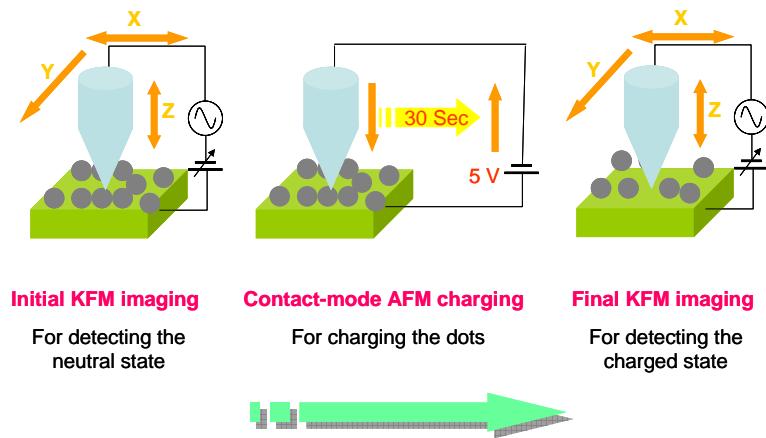

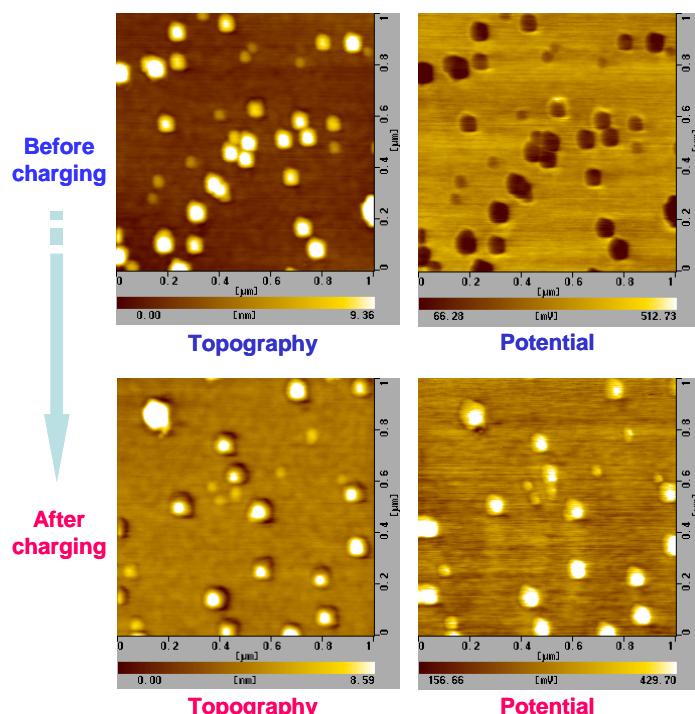

KFMは表面ポテンシャルを測定する走査プローブ顕微鏡であり、これを用いることにより、直接ナノ結晶シリコンドットの表面電荷状態を観測することができる。本研究では、図3.2.1.18に示すように、最初に電気的に中性の状態でKFM測定を行った後、電圧印加によりドットの帶電状態を変化させ、その後同じ位置でのKFM像の時間変化を観測した。形状像には電圧の印加前後での大きな変化は見られないが、電位像については、中性状態では基板より低いポテンシャルであったドットが、電荷蓄積により基板に対して高いポテンシャルの状態に移る振る舞いが観測された(図3.2.1.21)。

図3.2.1.18 KFM実験手順

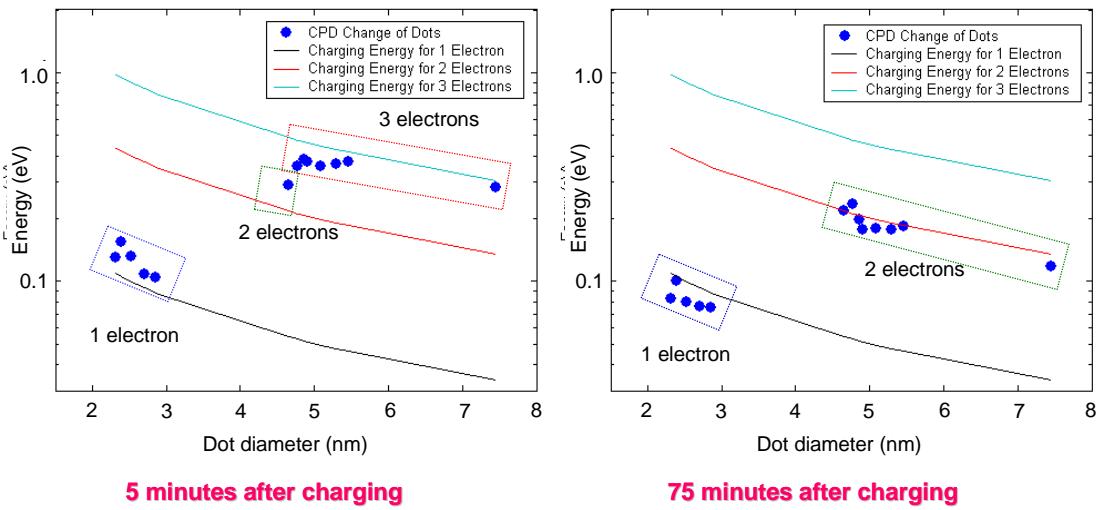

また、ポテンシャルの大きさはドットの粒径に依存し、大きなサイズのドットほど中性状態のポテンシャルは低く、帶電させたときのポテンシャルは高くなっている。図3.2.1.22のように、粒径を横軸に、帶電後のドット中心のポテンシャル高さを縦軸にとり、電子の帶電エネルギーの粒径依存性と比較すると、粒径3nm以下の小さいドットには1個の電子、粒径5nm以上の大きなドットには2個ないし3個の電子が蓄積されていることがわかる。また帶電5分後(左図)と帶電75分後(右図)の結果を比較すると、3nm以下のドットのポテンシャルはほとんど変化しないのに対し、5nm以上のドットの帶電状態は、ほとんど2個の電子の帶電エネルギーに対応する値に収束している。これらの結果から、ドット中に蓄積されている電荷は量子化されていて、かつ1電子蓄積の場合と2電子以上の蓄積がある場合ではその状態の保持時間が異なるということが示唆される。

図3.2.1.21 帯電前後の表面形状像およびKFM像

図 3.2.1.22 帯電エネルギーの粒径依存性

### 3.2.1.5 ナノ結晶シリコンドットの高密度集積化と位置制御

#### 3.2.1.5-1 ナノ結晶シリコンドットの位置制御

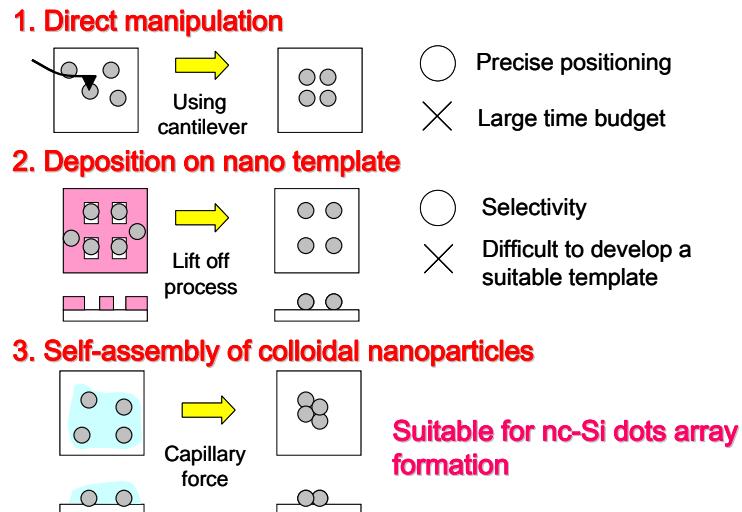

ナノ結晶シリコンドットの位置制御という技術課題は挑戦的な課題であり、ネオシリコンの創製のキーポイントである。図 3.2.1.23 には、位置制御のさまざまな方法を示した。基板上に堆積したシリコンドットはファンデアワールス力で物理吸着しているだけなので、AFMなどの走査プローブで機械的に移動できることは実験で確認済みであるが。この方法では能率が悪く、大規模集積回路では実用的でない。あらかじめパターンが形成されたテンプレート上に堆積し、テンプレートを除去することにより配列を実現することも考えられるが、この方法の場合はテンプレートをいかに作成するかが技術的な課題となる。そこで、本研究では、コロイドナノ粒子の分野で広く行われている分散溶媒を用いて粒子を集積化する技術をナノ結晶シリコンドット配列の形成に応用することを提案した。この方法は、ドットの大規模集積化、また高密度集積化という観点でも有利な方法である。

図 3.2.1.23 ナノ粒子位置制御の様々な方法

### 3.2.1.5-2 フッ化水素酸溶液を用いた方法

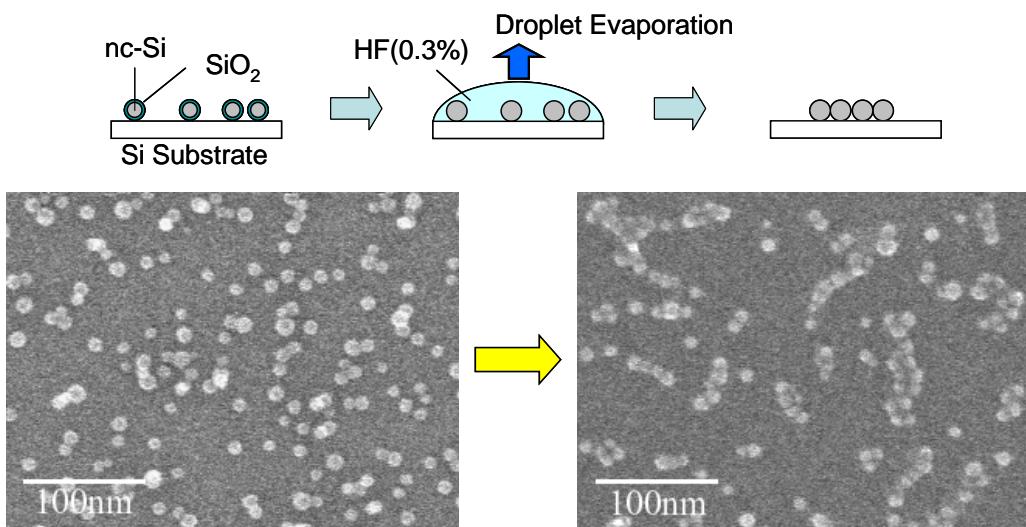

ナノ結晶シリコンの表面は非常に活性なため、基板上に堆積後に大気中に晒すと大気中の酸素や水分と反応し、表面に自然酸化膜が形成される。このとき、基板-ナノ結晶間の結合にもその影響が及んでいるということが実験結果から推測されている。したがって、その状態のナノ結晶シリコンの位置の制御のために、シリコン酸化膜を溶解するフッ化水素酸の水溶液を用いた実験を行った。図 3.2.1.24 に示したように、ドットを堆積し、自然酸化を経た基板上に 0.3% フッ化水素酸水溶液を滴下し、適度な時間放置して液体の蒸発を待つ。溶液滴下前と滴下蒸発後の基板上のナノドットの分布の変化を観察した SEM 写真を見ると、明らかに滴下蒸発後にナノドットは基板上を移動し、凝集により 1 次元ないし 2 次元的な凝集体を形成していることがわかる。コロイドを含む溶液が蒸発する際には、横毛管力が粒子に作用し、粒子は蒸発する液体の裾に曳かれて凝集することが知られており、この場合にも同様なメカニズムで凝集が起こったのではないかと考えている。また、この凝集は粒子の自己組織化の初期段階である核形成と考えることができ、条件の最適化により更なる大面積規則配列が期待される。

### Solution Droplet Evaporation Method (SDEM)

図 3.2.1.24 フッ化水素酸溶液を用いたナノ結晶シリコンドットの位置制御

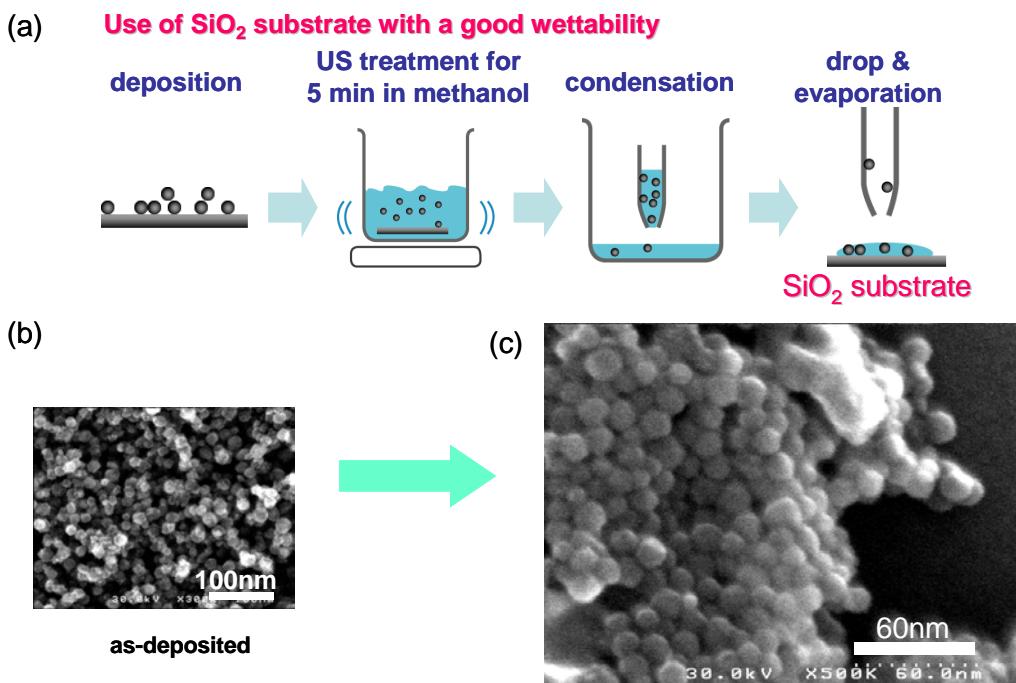

### 3.2.1.5-3 分散溶媒としてメタノールを用いた方法

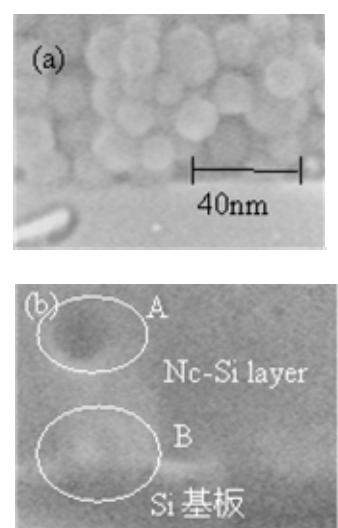

前述のフッ化水素酸を用いた方法は、ナノ結晶シリコンドットの分散溶液を基板上の液滴の中に形成し、それを蒸発させて集積化を試みるという方法であるが、化学反応が起きることに由来する塩が蒸発時に残留するという点や薬品の取り扱い安さの部分で問題がある。そこで、堆積後の自然酸化膜形成を極力抑制することを目的とし、堆積直後に基板を有機溶媒であるメタノールに浸漬し超音波処理を行ったところ、処理後の基板表面にはほとんどナノドットが残留していない様子が観測された。これは、ナノドットがメタノール中に分散しているということを示すものである。そこで、シリコンドットが分散しているメタノールを基板上に滴下し、蒸発後の基板表面の SEM 観察を行った。図 3.2.1.25 に一連のプロセスとプロセス前後の基板表面の観察結果を示す。プロセス

後の基板において、図 3.2.1.25(c)に示したようなドット凝集体構造が観測された。この構造におけるドット面密度は約  $7 \times 10^{11} \text{ cm}^{-2}$  と見積もられ、処理前の堆積のみの段階での面密度( $\sim 1 \times 10^{11} \text{ cm}^{-2}$ )に比べ一桁弱の高密度化が実現した。

### 3.2.1.6 得られた研究成果の評価および今後期待される効果

本研究では、「ネオシリコン」という新しい概念の実現にむけて、世界に先駆けて、VHF プラズマとパルスガス供給を組み合わせた非常に粒径分散の小さい粒径数 nm のナノ結晶シリコンドットを制御良く作製する技術を確立した。また、将来的な集積回路への応用を念頭に、ドット間の相互作用の制御を目的としたドット堆積後プロセスの確立にも着手し、酸化自己停止機構を利用した粒径制御や、窒化後の特異なトラップ生成についても明らかにしてきた。また、応用上での基礎特性として極めて重要な單一ドットの電荷保持特性について、走査プローブ顕微鏡を用いた直接観測による新たな測定技術を確立した。さらに、プロジェクトの開始時点では無理だといわれたランダムに堆積されるナノ結晶シリコンドットの位置制御についても、従来のシリコン加工技術とは全く異なる溶液を用いた方法を採用することにより、高密度化を実現した。最初に述べたナノ結晶シリコンドットの作製技術はもちろんであるが、その他の事項に関しても、ナノ結晶シリコンの電子デバイス応用を強く意識して、要素技術を確立してきているグループは世界的に見ても例がなく、きわめてオリジナリティの高い研究内容であるといえる。

今後期待される効果としては、これらの構造制御技術の確立により、ナノ結晶シリコン量子ドットの量子効果デバイスへの応用に関する研究が飛躍的に進んでいくことが予測される。「集積化されたナノ結晶シリコンドット量子効果デバイス」の実現する日が確実に近づいた事は疑う余地はない。さらなる課題としては、1)

図 3.2.1.25 メタノール分散溶液法によるネオシリコンドット高密度

単分散性を保持したままさらに粒径を縮小する技術の確立、2) 単一ドット電荷保持メカニズムの解明、3) 位置制御技術の改善によるシリコン量子ドット配列形成技術開発、などが挙げられる。

### 3.2.2 ナノ結晶シリコン量子ドット単電子デバイス

#### 3.2.2.1 はじめに

寸法が 10 nm 以下の量子ドット構造は、クーロンブロックード、バリスティック伝導など、ナノ構造に特有な興味深い物性が現れてくる舞台である。特に、ナノ結晶シリコン量子ドットは、既存のシリコン集積回路製造プロセス装置を用いて、シリコンチップ上に形成できるので、応用上きわめて有利である。また、理想的なポテンシャル障壁として働く良質な酸化膜、窒化膜をナノ結晶シリコンの表面に形成する技術により、さまざまな閉じ込めポテンシャルを持つ量子構造形成が可能である。シリコン集積回路中に量子効果デバイスを形成するためには、リソグラフィ技術などのトップダウン法により素子位置を精密に指定する必要がある。一方、量子効果を顕著に発現させるためには 10 nm 以下のナノ構造が必要で、電子線露光技術を用いてもトップダウン法だけでは限界があり、今後はトップダウン法とボトムアップ法を組み合わせて考えていくことが重要である。

我々は、ボトムアップ的なアプローチとして、VHF パルスプラズマプロセスを用いた直径 10 nm 以下のナノ結晶シリコンドットを制御良く作製する方法を確立してきた。また、トップダウン的な観点からは、電子線露光技術の工夫によるナノ微細構造電極の形成法や、エッチング条件の制御による加工寸法の縮小化などを検討してきた。本研究では、これらの技術を駆使し、ナノ微細構造シリコン量子ドット単電子デバイスの作製および特性評価を行った。単電子デバイスは、電子 1 個の動作が直接デバイス特性と結びついているデバイスであり、将来の超低消費電力素子への応用が期待されている。ナノ結晶シリコン量子ドットをクーロンアイランドとして用いたトランジスタの作製と特性評価について報告し(3.2.2.2)、次にナノ結晶シリコン量子ドットをフローティングゲートとして用いた単電子メモリ素子について、動作特性の評価を行った結果について述べる(3.2.2.3)。また、ナノ構造形成技術を組み合わせて作製したシリコン縦型量子ポイントコンタクトトランジスタにおいて、バリスティック伝導特性を実証したのでそれについても報告する(3.2.2.4)。

#### 3.2.2.2 ナノ結晶シリコン単電子トランジスタ

##### 3.2.2.2-1 プレーナ型電極素子構造

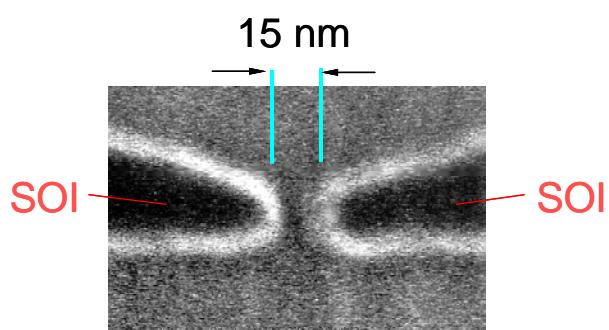

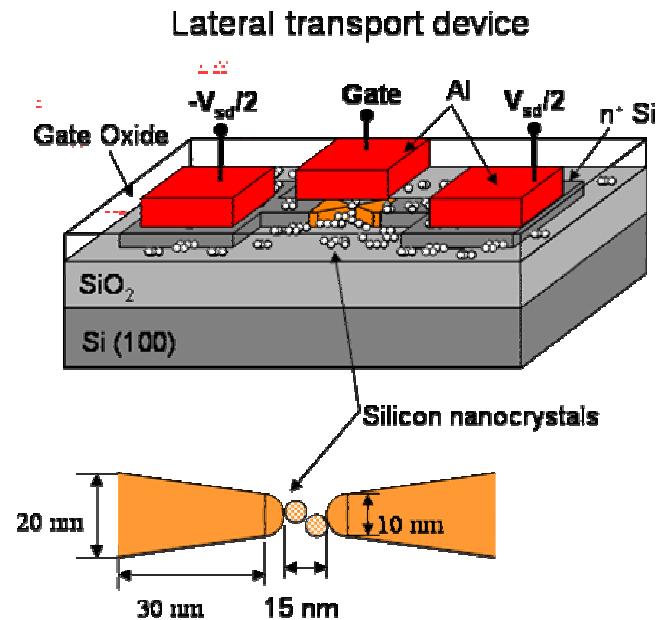

電子ビーム露光技術と ECR 反応性プラズマエッチング技術の最適化により最小間隔 15 nm のシリコン極微細構造の形成に成功した(図 3.2.2.1)。RD2000 ネガ型レジストを使用し、近接効果の補償には 2 段階露光を行っている。SOI でこの電極パターンを形成した後、この上に、VHF パルスプラズマ法によるナノ

図 3.2.2.1 電子ビーム露光技術により作製した SOI プレーナ型電極構造

結晶シリコンドットを堆積する。ナノ結晶シリコン表面の酸化膜がトンネルバリアとなる。シリコン量子ドットはランダムに分布するが、電極間を流れる電流は最もトンネル抵抗の低い部分で決まると仮定すると擬1次元多重トンネル接合素子と等価的に考えることができる。このような構造では電子の帶電効果が顕著になり、単一電子の注入にしきい電圧が必要なクーロンブロックエード現象が期待される。次いでゲート絶縁膜、ゲート電極を堆積するプロセスにより、粒径8 nmのシリコン量子ドットをチャネルとするトランジスタを形成した。トランジスタの模式図を図3.2.2.2に示す。

図3.2.2.2 プレーナ型電極構造单電子トランジスタの模式図

### 3.2.2.2-2 单電子トランジスタ特性評価

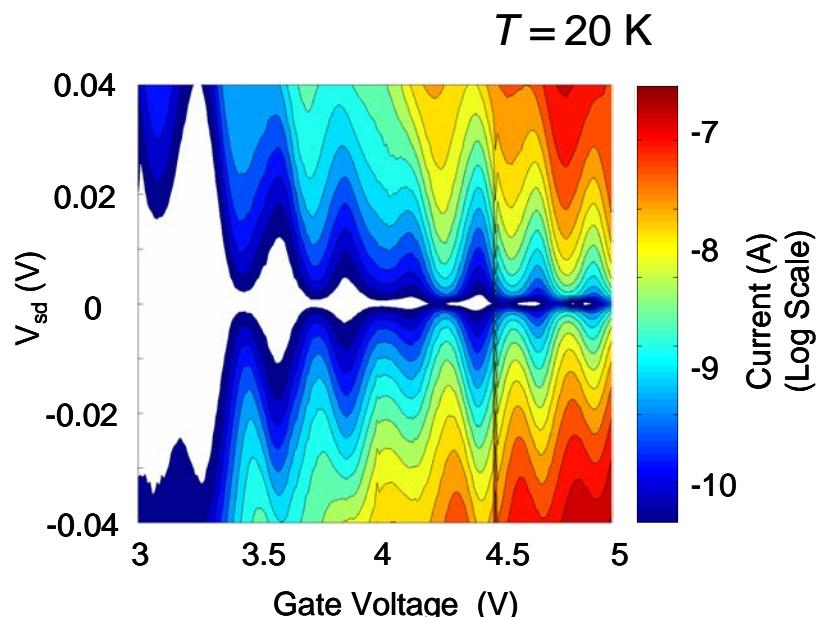

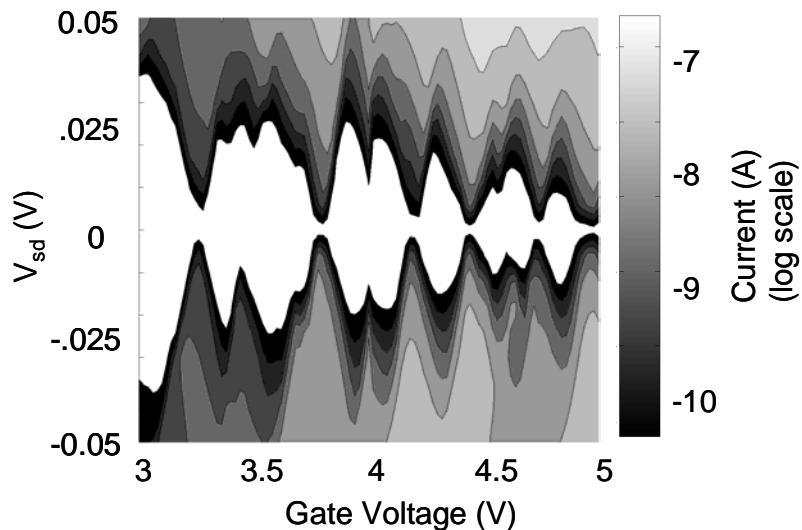

20 Kでの測定では、单電子トンネル現象に特有なクーロンブロックエードやクーロン振動が明瞭に観測された。電極間隔15 nmのSOIパターン上にシリコンドットを堆積した試料の電子輸送特性(クーロンダイヤモンド)を図3.2.2.3に示す。縦軸と横軸はトランジスタの3端子のうち2つの電極間の電圧を表し、曲線は等電流曲線を表す。曲

図3.2.2.3 プレーナ型電極構造单電子トランジスタにおけるクーロンダイヤモンド

図 3.2.2.4 室温でのクーロン振動(微分測定)

特性は主として 1 個のクーロン島に依るものと考えることが出来る。クーロン振動特性の周期は規則的であるが、教科書にあるような金属アイランドの特性とは異なっている。ゲート電圧が低い領域では電流は流れない。電流の閾値電圧が存在する。電流の高さも一様ではない。

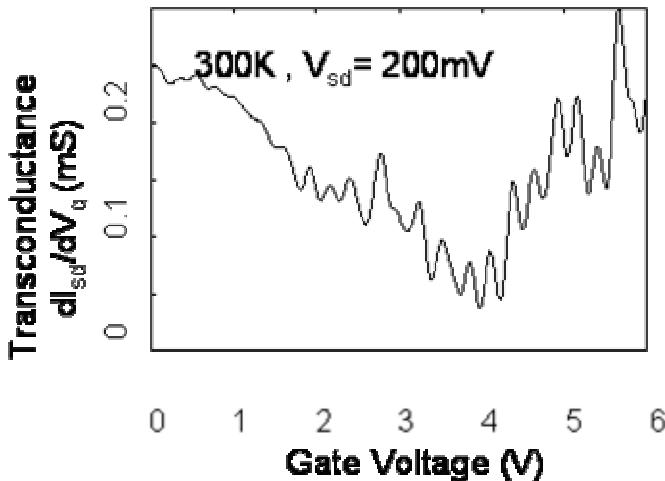

これらは、半導体の量子ドットに特有な性質である。測定温度を高温にすると振動ピークの幅は広がるが、同じゲート電圧にピークは観測される。室温においても、微分測定を行うことにより、クーロン振動を観測することができた(図 3.2.2.4)。室温での観測結果は、実用化に対しても有望であるが、同時にさらなる微細化が必要であることを意味している。多数の測定データから構成される曲線の形状から、電子輸送特性は極めて安定で再現性の高いことが分かる。20 K で測定したデータは量子効果を考慮したモデリングが可能であるのに対して、5 K で測定したデータは、ダブルエット構造が観測され複雑である(図 3.2.2.5)。トンネルバリアの一つがオーミック性を失い、隣接するドットの容量成分が関与した結果であろう。温度依存性の詳細な検討により、単一量子ドットの電子輸送特性だけでなく、ドット間のキャリヤの相関についても情報が得られる。

図 3.2.2.5 プレーナ型電極構造单電子トランジスタの低温測定における

クーロン振動の分裂

線が波のように振動しているのは、1 個 1 個の電子が注入する様子を表している。これは、1 個 1 個の電子の注入によりトランジスタのスイッチ動作ができる事を意味する。従来の 30 nm 間隔の電極では、チャネルを構成するドットの数が多くて、測定結果は複雑でモデリングが困難であったが、15 nm 間隔では 2-3 個のナノ結晶がチャネルを構成するので、規則的な特性が得られた。特に、電極との重なりが大きいドットはオーム接触とみなすと、輸送

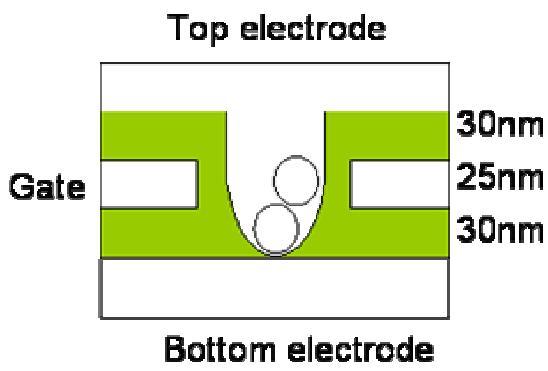

### 3.2.2.2-3 縦型微細電極構造素子による単一シリコン量子ドットの電子輸送特性

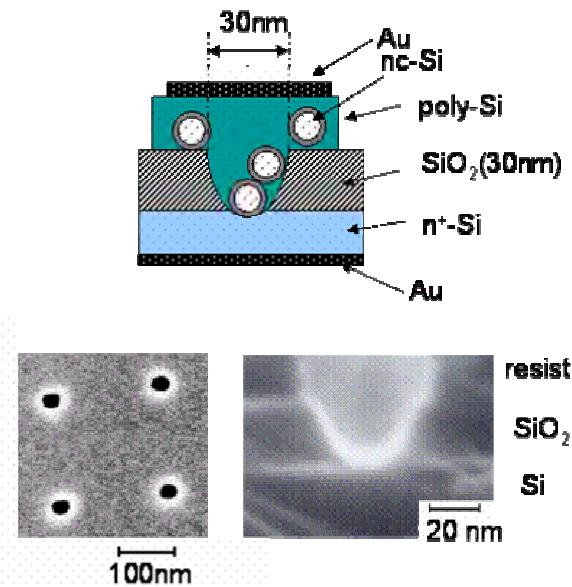

シリコン単電子トランジスタの核になる構成要素である単一シリコン量子ドットについて、その電子輸送特性を評価する必要がある。この場合、プレーナ型電極構造を用いるよりは縦型電極構造を用いたほうが有利である。そこで、酸化膜中に寸法 10 nm 程度の微細孔を設けた構造の素子にシリコン量子ドットを堆積し、单一量子ドットによる電子輸送特性を調べた。図 3.2.2.6 に素子の模式図と平面、及び断面の SEM 像を示す。酸化膜のテーパ状エッチング特性により、上部開口は 50 nm 程度であっても、底部の開口は 10 nm 程度であり、1 個のシリコンドットが占めることになる。上部電極はポリシリコンを CVD 法により形成する。CVD の充填特性により、たとえ複数のドットが微細孔部に堆積しても、最下部のドットに接触する。シリコン量子ドットの周囲に形成される自然酸化膜がトンネルバリアとして働く。測定する個々の素子にシリコン量子ドットが実際に入っていることを確認することが困難なので、シリコン量子ドット堆積プロセスを省略した素子の測定も行い比較を行った。図 3.2.2.6 のダイオード構造の試料の電流電圧特性を種々の温度で測定し、零バイアス近傍の伝導度ディップの半値幅を解析すると接合の数が 2 個の単一量子ドットモデルで説明できる特性を得た。さらにモンテカルロシミュレーションでも單一ドット 2 接合のモデルで実験結果を再現することが出来た(図 3.2.2.7)。さらに詳細な検討を加えるため、図 3.2.2.8 に示すようなラップゲートを設けた。ゲー

図 3.2.2.6 シリコン量子ドット輸送特性評価のための縦型電極構造

図 3.2.2.7 輸送特性の測定結果とシミュレーション結果の比較

トに電圧を加えることにより、シリコン量子ドットの帶電状態を変化させて電子輸送特性を評価することができる。5 Kで測定した結果を図 3.2.2.9 に示す。単電子輸送現象に特徴的な周期的なクーロン振動特性が観測できた。しかし、周期は单一ではなく、複数の周期が重畠している。これは、隣接する量子ドットからの寄与を考慮して説明できる。すなわち、ラップゲート縦型トランジスタ構造を用いて、単一シリコン量子ドットの電子輸送特性を定量的に評価すると同時に、量子ドット間のキャリヤ相関に関する情報も得られたことになる。これらの情報は、量子ドットを用いて、量子セルオートマトンや量子コンピュータを実現するために重要である。

図 3.2.2.8 ラップゲート縦型

電極素子模式図

図 3.2.2.9 ラップゲート縦型電極

素子で観測されたクーロン振動

### 3.2.2.3 ナノ結晶シリコン単電子メモリ

#### 3.2.2.3-1 素子構造

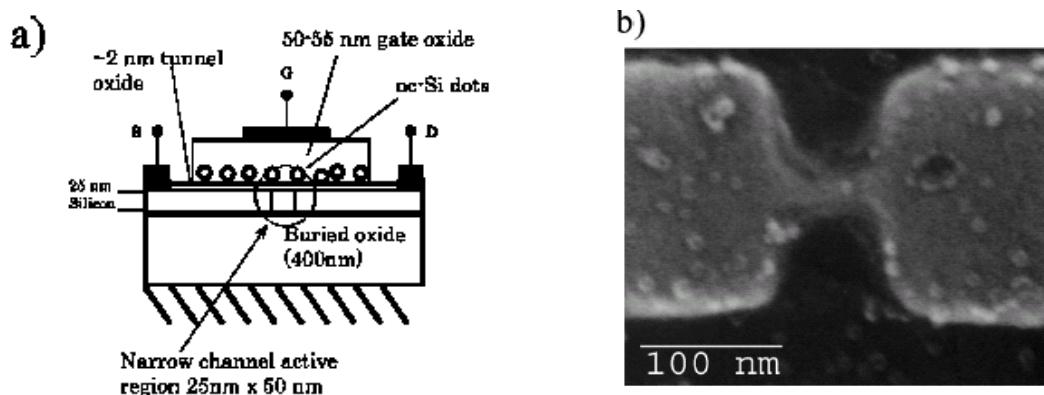

ナノ結晶シリコン量子ドットをトランジスタチャネルの近傍に配置させると、量子ドット中の帶電状態によりトランジスタの導電特性を変化させることができる。従って、この構造で単電子メモリデバイスを実現でき、超低消費電力の大容量不揮発性メモリへの応用が期待されている。MOSFET のチャネル近傍にトンネル酸化膜を介して配置したシリコンナノクリスタル量子ドットを蓄積ノードとする単一電子メモリ素子を作製しその特性を評価した。SOI 層は 30 nm まで薄層化して、EB 露光と ECR エッチングによりチャネル領域を  $20 \times 50$  nm まで狭窄化した。膜厚 2 nm のトンネル酸化膜を形成した後に、プラズマプロセスにより、粒径 8 nm のナノクリスタルシリコン量子ドットを堆積した。膜厚 50 nm のゲート酸化膜を形成した後にポリシリコンゲートを堆積した。素子の模式図とナノ結晶シリコンドットを堆積した狭チャネル近傍の SEM 像を図 3.2.2.10 に示す。

図 3.2.2.10 (a) ナノ結晶シリコン単電子メモリの模式図 (b) チャネル近傍の SEM 像

### 3.2.2.3-2 電気特性評価

チャネル領域  $30 \times 50 \text{ nm}$  の素子について  $77 \text{ K}$  で測定したチャネル電流のゲート電圧依存性からは、ゲート電圧の掃引範囲（書き込み電圧）を増加すると、シリコン量子ドットに電荷が蓄積されるのに伴いしきい電圧がシフトするという結果が得られた。しきい電圧は書き込み電圧に対して階段状に変化することから、電子が 1 個ずつ蓄積していく様子が分かる。しきい電圧のシフト量、書き込み電圧の幅は、素子の寸法から予想される値に一致する。 $20 \times 50 \text{ nm}$  まで狭チャネル化した素子の特性は、図 3.2.2.11 に示すように、室温においてもメモリ特性を示す。チャネル電流の過渡特性を調べると階段状に変化することから、単電子メモリ現象を裏付けている。しかし、メモリ保持時間は室温において数分程度であり、更なる保持時間特性の向上が必要である。

図 3.2.2.11 狹チャネルナノ結晶シリコン単電子メモリの室温における特性

### 3.2.2.4 縱型シリコンバリスティックトランジスタ

#### 3.2.2.4-1 素子構造

前出の単一シリコン量子ドットの輸送特性評価に用いたものと同一の縦型電極構造を電子ビーム露光、プラズマエッチング、薄膜堆積技術を駆使して作製し、ナノ結晶シリコンを堆積せずにポリシリコンの堆積を行うと、そのポリシリコンの一部がチャネルになり、ラップゲートを有する、シリコン縦型トランジスタが作製される(図 3.2.2.12)。この構造においては、チャネル長はゲート電極のポリシリコン薄膜堆積膜厚(20 nm)で決まるので、リソグラフィ技術の制約は受けない。ラップゲートに加える電界が空乏層を形成して、シリコンチャネルを狭窄化できるので、ほぼ理想的な量子ポイントコンタクトが実現される。さらに、シリコンチャネルは2段階アニール法により形成した高品質ポリシリコン薄膜であり、チャネル内は無欠陥完全単結晶と考えられる。

図 3.2.2.12 シリコン縦型トランジスタの模式図

図 3.2.2.13 シリコン縦型トランジスタにおける量子化コンダクタンスの観測

#### 3.2.2.4-2 電気特性評価

コンダクタンスの量子化に伴う階段状の I-V 特性を 3-5 K の温度範囲で観測することが出来た(図 3.2.2.13)。化合物半導体と較べて移動度の低いシリコンからの量子コンダクタンスは極低温における AC 測定を中心にいくつか報告されているが、DC 測定により明瞭な量子化コンダクタンスが観測されたのは例がない。今回作製した縦型トランジスタの CVD ポリシリコン膜の粒径が素子寸法より十分に大きいこと、ゲート電圧によりチャネル幅を 0 個、1 個と制御できること、チャネル長はポリシリコンゲート膜厚の 20 nm と短いことなどにより、シリコンでバリスティック伝導が実現できているものと思われる。

磁場を印加して測定したときの量子化コンダクタンスの振る舞いからは、スピントバレーの縮退が解けていることが分かる(図 3.2.2.14)。バイアス電圧を 100 mV と大きくなった測定では、バリスティック伝導の条件は満たさないので、コンダクタンスの値は低くなっている。コンダクタンスのプラトー値は、デバイスの形状によって異なっている。図 3.2.2.13 の測定に用いた素子はストレート形状のチャネルであるため、通常の 4 重に縮退したシリコンの特徴を反映しているが、図 3.2.2.14 の測定に用いた素子はテー

パ形状のチャネルを有するため、零磁場においても縮退が解けてい

ると考えられる。

図 3.2.2.14 磁場印加時の量子化コンダクタ

ンス

### 3.2.2.5 得られた研究成果の評価および今後期待される効果

本研究は、現在盛んに行われているシリコンを用いた单電子デバイスの研究のひとつであり、单電子デバイスを特徴づける電荷溜めに、ボトムアップ技術により作製したナノ結晶シリコンを用いていることが大きな特徴である。プレーナ型单電子トランジスタ特性については、クーロンアイランドとして用いるナノ結晶シリコンの対称性を反映したきれいな振動特性が得られており、インパクトの大きい研究結果である。これにさらにドットの位置制御技術が加われば、特性のそろった单電子トランジスタの集積化につながるであろう。このナノ結晶シリコンの輸送特性を測定に用いた縦型電極は非常に巧妙であり、評価できる。また、2つのドットが含まれている場合には、2ドットの相互作用による2準位系の量子ビットの実現が期待できるため、更なる発展が可能である。单電子メモリの研究に関しては、メモリ素子というよりはむしろ、单電子メモリの要素としてのナノ結晶シリコンの特性に注目したもので、長い保持時間を確保するための指針を与えるものである。電子デバイス応用に対する新しい機能材料としてのナノ結晶シリコンの役割に焦点をあてて総合的に探った研究はこれまでなく、世界的にもユニークな視点であるといえる。

また、縦型トランジスタで観測されたバリスティック伝導に起因する量子化コンダクタンスは、シリコンでは世界で初めての観測であり、微細加工の工夫の賜物である。無散乱の伝導が生じるため、将来的には低電流動作が必要な素子への応用が期待される。さらには、量子化コンダクタンスに観測されるステップやプラトー構造を積極的に利用する素子の可能性も考えられる。

これらを実現するための解決すべき問題点は多い。特に、ボトムアップ技術で作製するので位置制御の観点からは精度が極めてよくない。より正確なデータを得るために、ナノ結晶シリコンの配列制御の研究も同時に進めていく必要がある。

### 3.2.3 ナノ結晶シリコン平面型電子放出素子

#### 3.2.3.1 はじめに

近年、フラットパネルディスプレイにむけたさまざまなタイプの電子放出素子の開発が進んでいる。こういった電子放出素子には低駆動電圧、低消費電力、低コストなどの性能が要求されているが、その中でポーラスシリコンを用いた電子放出素子が上述の条件を満たすデバイスとして注目されている。特にこの素子においては、通常の散乱メカニズムでは説明できないような高エネルギーの電子放出が観測されており、この特異な電子放出のメカニズムについては明らかではないが、電子走行層に存在するナノ結晶シリコンが非常に重要な役割を果たしていることは、さまざまな実験により検証されつつある状況である。

我々は、VHF パルスプラズマプロセスにより気相中でナノ結晶シリコンを作製する技術を開発してきた。この技術は、1) ドライプロセスである、2) 任意の基板に堆積可能である、という点が、ポーラスシリコンと大きく異なる特徴である。

本研究では、ナノ結晶シリコンを用いた平面型電子放出素子を作製し、その電子放出性能の評価および特性向上に向けた作製プロセスの改善を行ったので、その成果について報告する(3.2.3.2節)。また、放出電子のエネルギー分布の測定を行い、ナノ結晶シリコン平面型電子放出素子においてもポーラスシリコン素子と類似の高エネルギー電子の放出が起こるということを明らかにしたので、それについても報告を行う(3.2.3.3節)。

#### 3.2.3.2 ナノ結晶シリコン電子放出素子の作製と特性評価

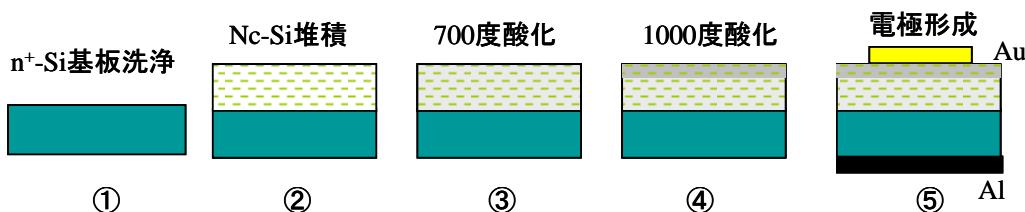

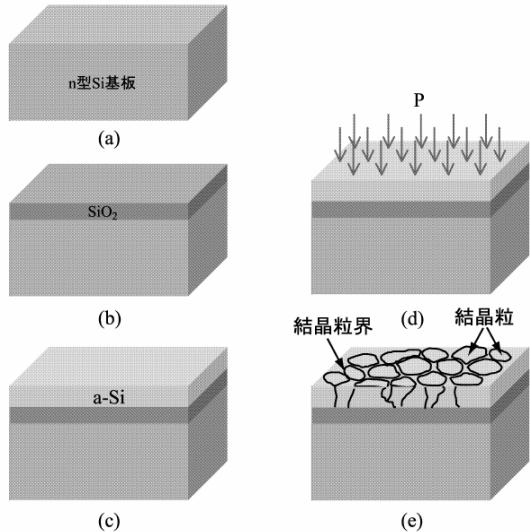

##### 3.2.3.2-1 作製プロセス

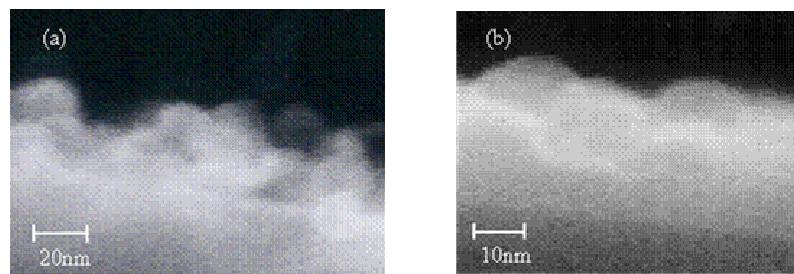

図 3.2.3.1 にこの素子の作製プロセスを示す。まず、抵抗率の低い( $\rho \sim 10^{-2} \Omega \text{ cm}$ )n型シリコン基板に VHF パルスプラズマプロセスにより、直径 6 nm から 10 nm で、よく粒径制御されたナノ結晶シリコンを堆積する。このときのナノ結晶シリコン層の膜厚は、0.1 – 1.5  $\mu\text{m}$  程度である。堆積後すぐに試料を電気炉に入れ、700 °C, 1 時間、続いて 1000 °C, 5 分のドライ酸化を行う。はじめの酸化はナノ結晶シリコンの周りにトンネル酸化膜を形成し、後の酸化でキャップ層を形成する。素子の断面 SEM 写真から、基板付近では球形のドットがはっきり観測され、ドット間の空隙も残存しているのに対し、上部電極に近いキャップ層は酸化が進み、ドットの判別ができにくくなっている様子がよくわかる(図 3.2.3.2)。

図 3.2.3.1 素子作製プロセス

均一な電子放出特性を実現するためには、素子内部の電界がなるべく均一になる必要があり、そのため、表面のラフネスを軽減する必要がある、いくつかの試料については、リフローアニールプロセスを行い、表面の平坦化を試みた。バルクの  $\text{SiO}_2$ 、及び Si の融点はそれぞれ約 1700 °C、1400 °C と高いが、このナノ結晶シリコンが  $\text{SiO}_2$  で覆われている構造をもつ膜の場合、表面が非常に大きな割合を占めるため、融解やマイグレーションが起こりやすくなり、

図 3.2.3.2 1000 °C酸化後の素子の断面SEM写真

図 3.2.3.3 アニール前(a)とアニール後(b)の断面 SEM 写真

より低温でリフローによる平坦化が実現する。ナノ結晶シリコンを数層堆積した試料について、800 °Cで 5 分間酸化した後、1200 °Cで 4 時間アニールを行った。図 3.2.3.3 に示したアニール前後の試料の断面 SEM 像によると、アニール後にナノ結晶シリコンに特徴的な球状の凹凸形状が緩和されていることが分かる。

膜厚の厚い素子を形成する際には、上記の方法のみでは不十分であり、より平坦な表面の実現のために、酸化膜中にリンを拡散させて酸化膜の融点をさらに下げ、リフローアニールによって表面を平坦化するプロセスを行った。リンの拡散源は  $\text{P}_2\text{O}_5$  を用い、窒素雰囲気中 1100°Cで 10 分間拡散する。このプロセス前後のナノ結晶シリコン層の断面の変化を図 3.2.3.4 に示した。アニール前にはナノ結晶シリコンの球状の形がはっきり分かる積層構造であったのに対し、アニール後はその輪郭はほとんど消えている。また、膜厚に関しても、最初のナノ結晶シリコンの堆積時には、層の膜厚が 150 nm であったのに対し、アニール後は 60 nm まで減少しており、これからも、平坦化が非常にうまくいっていることがわかる。この不純物拡散を用いる方法を用いたプロセスを考える場合、酸化膜やナノ結晶シリコンに拡散する不純物が、素子の特性にどのように影響を及ぼすかについても調べる必要がある。リン拡散を用いなくても、ナノ結晶シリコン

図 3.2.3.4 平坦化前(a)、後(b)の断面 SEM 写真

堆積後に酸化、アニールプロセスを数回繰り返すことにより、不純物拡散のないプロセスでトータルの膜厚が 60 nm 程度の平坦な素子を作製することができるため、この 2 つの異なる方法で作製した素子間での特性の比較を行った。電子走行層であるナノ結晶シリコン層の形成を行った後は、表面に膜厚 10 nm の金電極を電子ビーム蒸着により形成し、裏面には基板へのコンタクトを取るためのアルミニウム電極を形成する。

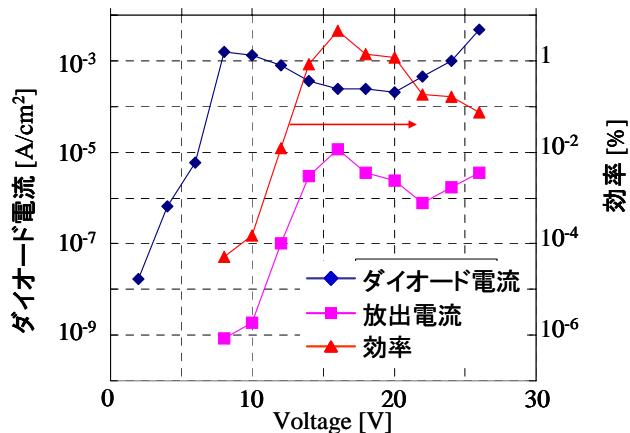

### 3.2.3.2-2 電子放出特性評価

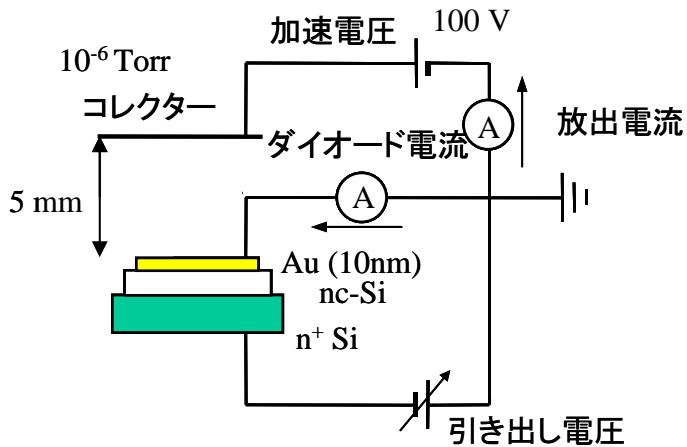

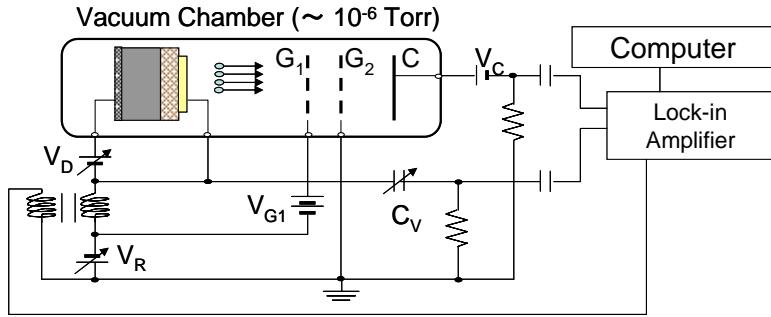

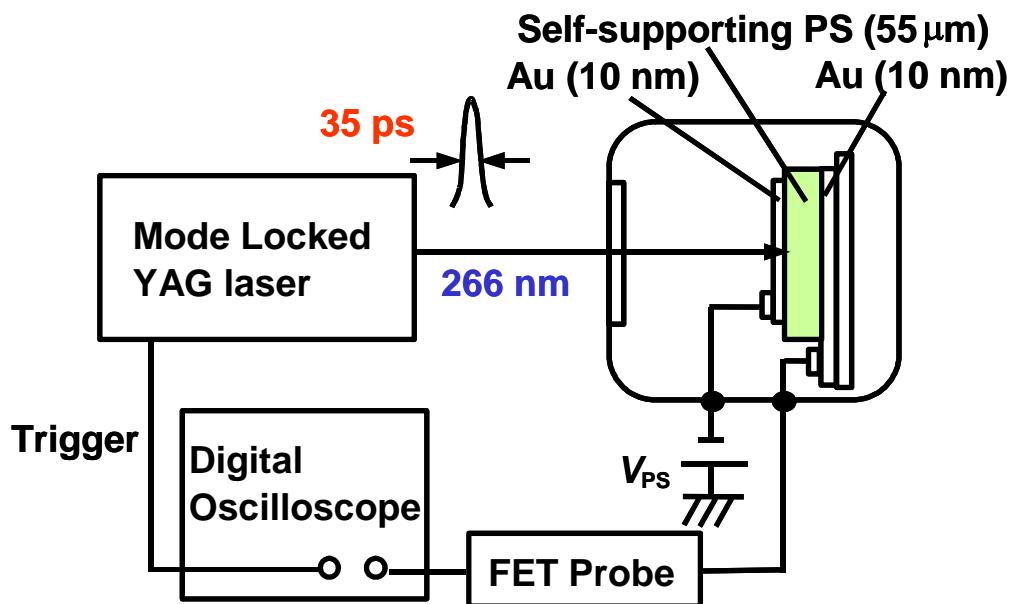

図 3.2.3.5 は、電子放出素子の特性評価のための配線図である。測定は、 $10^{-4}$  Pa 以下の真空チャンバー内でおこなう。素子の表面の金電極を接地し、裏面の Al 電極に負の電圧を印加する。裏面からナノ結晶シリコン層へ注入された電子は、大部分が金電極に流れ込み、ダイオード電流として観測されるが、走行層でエネルギーを得た一部の電子が金電極を通過して放出される。金電極の表面から約 5 mm 離れた位置にコレクタ電極を設け、100 V の電圧を印加しておき、放出された電子を捕集する。これが電子放出電流として観測される。電子放出素子の性能を表す指標として電子放出効率があり、これは放出電流の全電流に対する比として定義する。

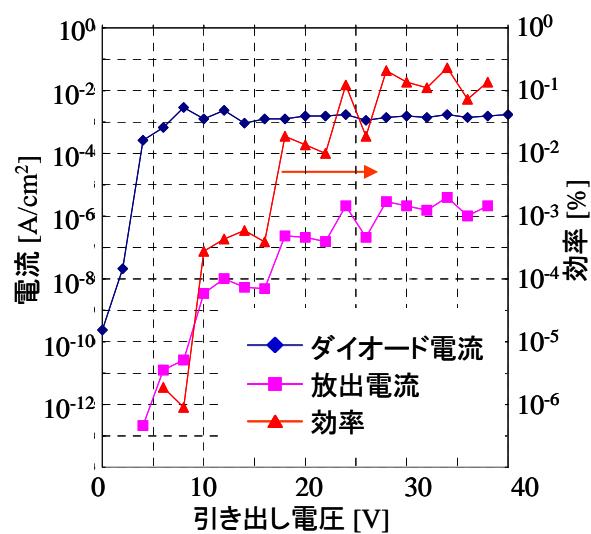

平坦化を行う前のナノ結晶シリコン層の膜厚が 1  $\mu\text{m}$  の試料の測定結果を図 3.2.3.6 に示す。横軸は裏面電極にかけたマイナス電圧の大きさを示す。電圧を上げるにしたがってダイオード電流が増加するが、ちょうど金の仕事関数の値 ( $\sim 5 \text{ eV}$ ) を超えたあたりから放出電流が観測され始める。電圧 36 V で放出電流として約  $4 \text{ }\mu\text{A}/\text{cm}^2$ 、電子放出効率として 0.2 % が得られている。平坦化を行わない試料においても、表面のラフネスが小さい試料の方が高い電子放出効率を示す傾向にあり、この素子の特性に表面の凹凸の状態が重要であるということが示唆される。実際に、リン拡散を用いた平坦化プロセスを経た試料の電子放出特性を図 3.2.3.7 に示す。16 V においてエミッショントリニティ電流  $10 \text{ }\mu\text{A}/\text{cm}^2$ 、電子放出効率 4.5% が得られ

図 3.2.3.5 電子放出素子測定ダイアグラム

図 3.2.3.6 平坦化を行う前の試料での電子放出特性の測定結果

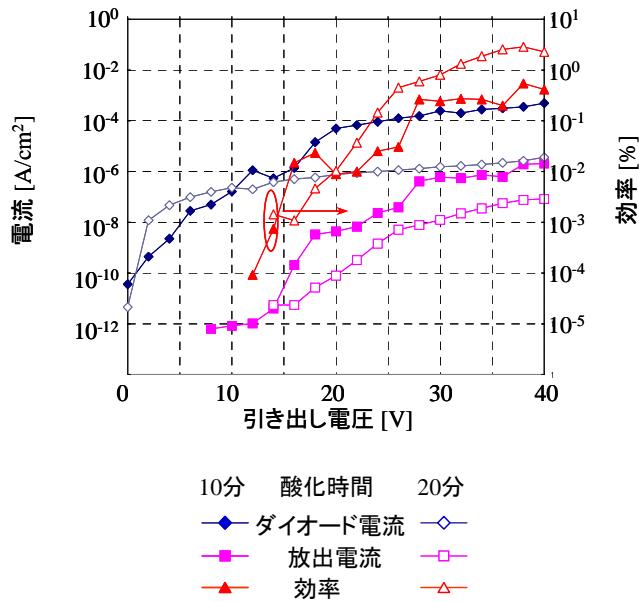

ており、平坦化により 1 枝以上の効率の改善が見られた。さらに、リン拡散前の酸化工程とリン拡散、アニールの工程を分離することにより、より高い効率の素子も得ることが可能である。これに対して、繰り返し酸化—アニール法により平坦化を行った素子の電子放出特性を図 3.2.3.8 に示す。トータルの酸化時間が異なる 2 つの試料の結果である。

酸化時間が長い試料の方が電流レベルは小さくなっているが、効率としては大きな値を示している。これは、酸化時間の長い試料では、電子走行層における酸化膜部分の増加により総電流量は減少するものの、電子走行層に含まれるナノ結晶シリコンの割合は小さくなるため、球形のナノ結晶シリコンに電界がかかるときに生じる電界の横成分の影響が少なくなり、電界の方向にまっすぐに走る電子の割合が相対的に多くなるからと解釈することができる。トータル 20 分酸化の試料において効率数%程度が得られており、この方法においても平坦化による素子特性の改善が明らかである。

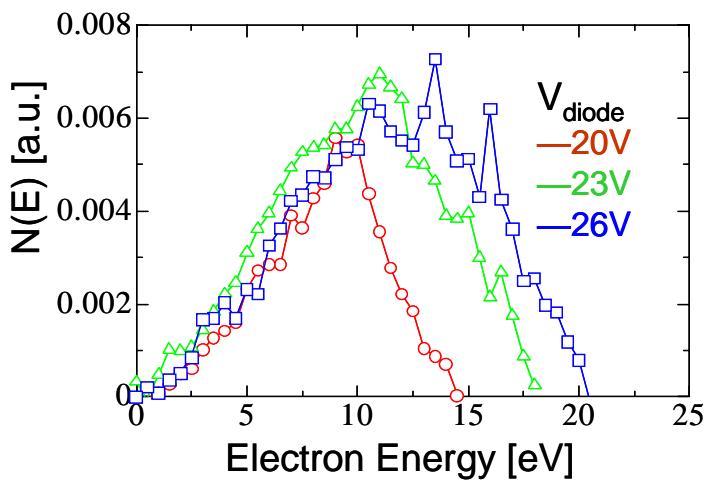

### 3.2.3.2-3 放出電子エネルギー分布の評価

更なる高効率化を考えた場合、ナノ結晶シリコンで構成された電子走行層の輸送機構を明らかにすることは極めて重要である。そこで、ナノ結晶シリコン電子放出素子の放出電子のエネルギー分布を測定することにより、電子走行層における散乱機構に関する知見を得ることを試みた。測定は図 3.2.3.9 に示したような阻止電場型分析装置を用いて行った。真空中で電子放出素子を動作させ、阻止電圧と呼ばれる電圧のかかったメッシュ電極を通過してコレクタ電極に到達する阻止電圧以上のエネルギーを持つ電子による電流を、阻止電圧を変化させながら観測することでエネルギー分布を測定する。用いた試料は、リン拡散により表面平坦化を施した試料で、ナノ結晶シリコン堆積後、850°Cで 20 分酸化、1050°Cで 6 分のリン拡散の後、1100°Cで 10 分間、窒素アニール行

図 3.2.3.7 リン拡散による平坦化後の試料での電子放出特性の測定結果

図 3.2.3.8 繰り返し酸化—アニールによる平坦化後の試料での電子放出特性の測定結果

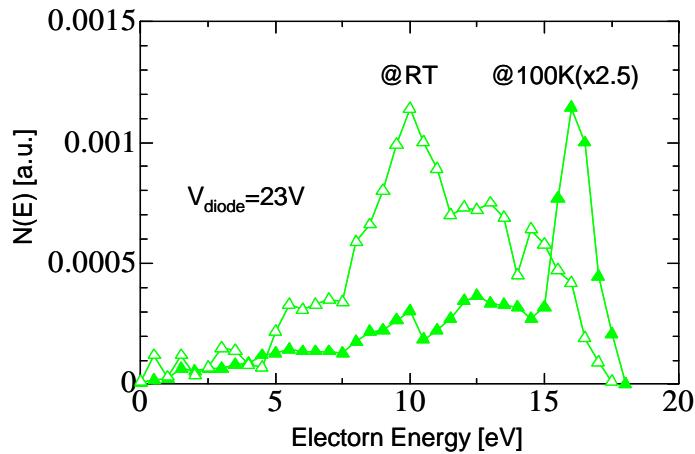

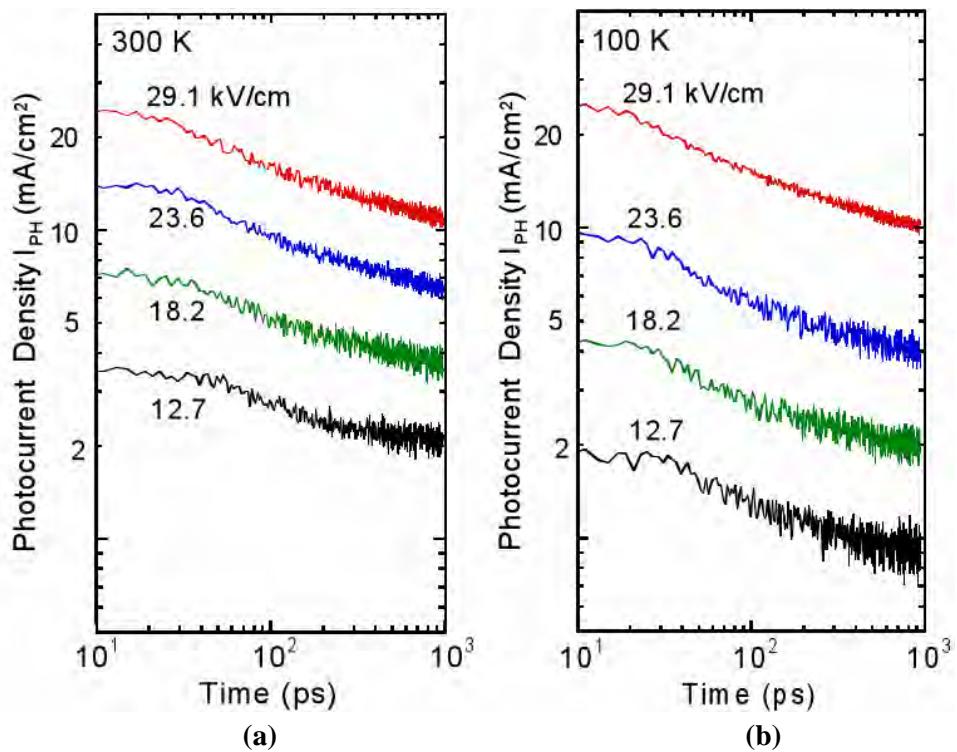

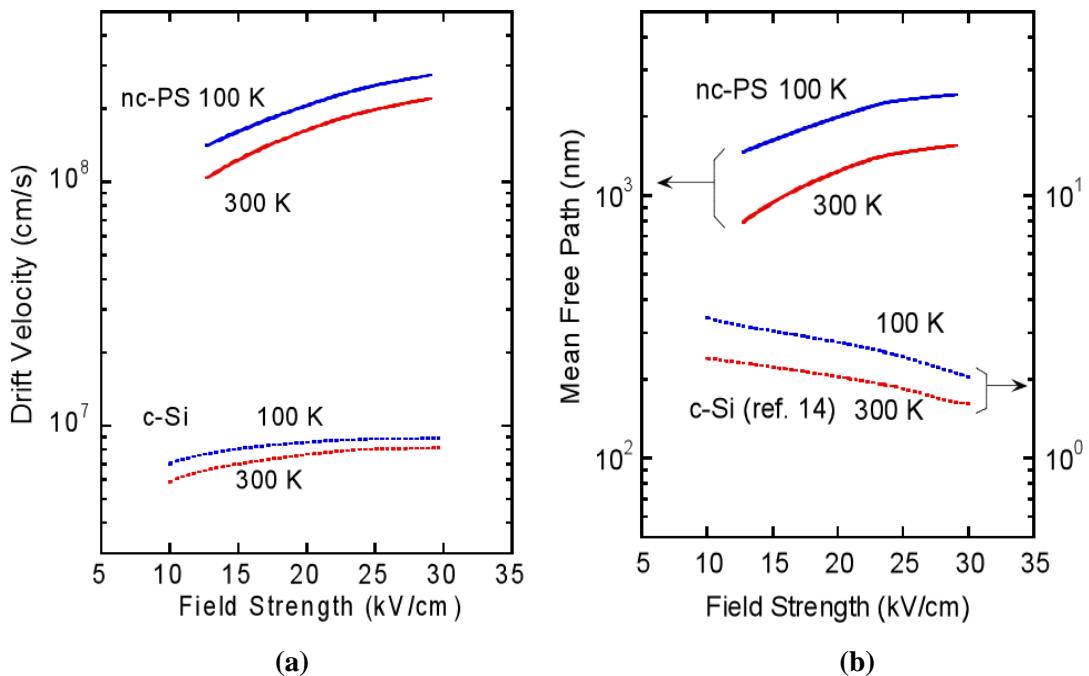

ったものである。測定したエネルギー分布を図3.2.3.10に示す。このエネルギー分布はノイズまじりではあるが、このノイズの原因是放出電流値が時間的に安定せず、ある程度変動しているためにこの変動をロックインアンプが交流信号として拾

ってしまうことによるものと考えられる。最もこのノイズが大きくなる0V付近でもある程度小さな値に収まっていることからある程度正確なエネルギー分布を示しているといえると考えられる。

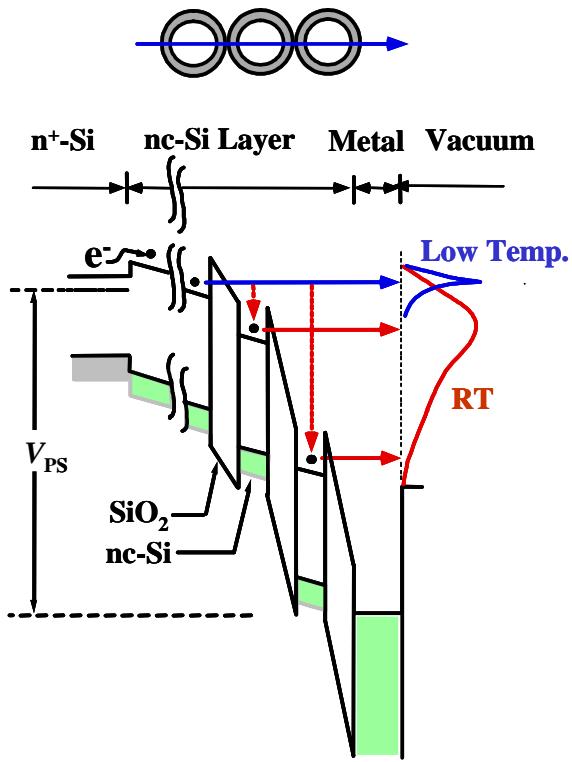

そしてエネルギー分布の様子であるが、印加したダイオード電圧の上昇に従ってエネルギー分布のピーク位置がシフトしているのがわかる。この振る舞いは、ポーラスシリコン電子放出素子で観測されている放出電子エネルギー分布と非常に良く似た振る舞いであり、明らかにMOS型の電子放出素子で報告されているようなマクスウェル分布とは異なっている。このことは、ナノ結晶シリコンを用いた電子放出素子においても電子走行層における散乱が抑制され、弾道的に伝導する電子が存在するということを示唆するものである。図3.2.3.11には100Kまで冷やして測定した結果および100Kと室温とのエネルギー分布を比較して示す。ピークが鋭くなるようが観測されており、これは低温化により電子の平均自由行程が伸びることにより散乱される電子が減少し弾道的に伝導する電子が増加したためであると考えられる。また、室温と低温での測定結果を比較した場合、低温化することにより低エネルギーの成分が抑えられてピークおよび平均エネルギーが上昇しており弾道伝導する電子が存在を示唆する。低温では、ダイオード電圧が大きくなつくるとピークが広い分布を持つようになっている様子が観測されており、これは発熱により低温化の影響が薄れたためである。

図3.2.3.9 阻止電場型エネルギー分析装置の模式図

図3.2.3.10 室温での放出電子のエネルギー分布の測定結果

図 3.2.3.11 低温での放出電子のエネルギー分布の測定結果との比較

### 3.2.3.2-4 ナノ結晶シリコン層の電子輸送メカニズム

ポーラスシリコン電子放出素子とナノ結晶シリコン電子放出素子の共通点は、電子走行層にナノ結晶シリコンの鎖構造を内包しているということである。したがって、比較的高いエネルギーを持つ電子の放出とナノ結晶シリコンチェーンの存在は密接な関連があるということが示唆される。

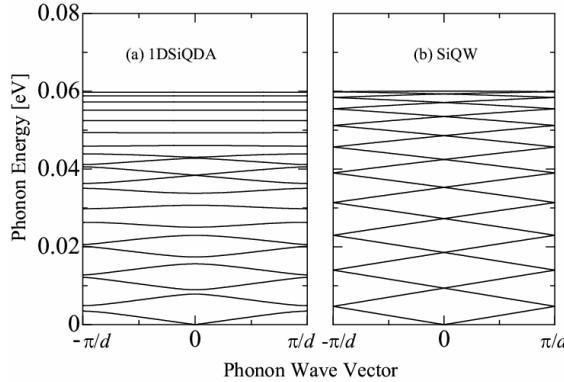

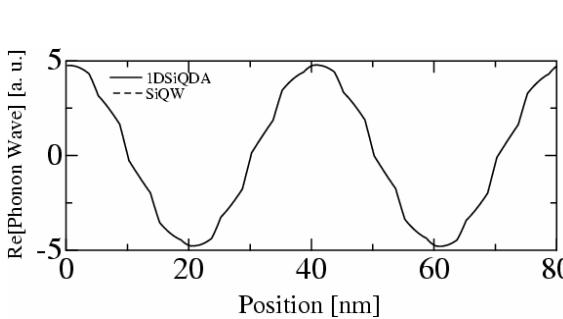

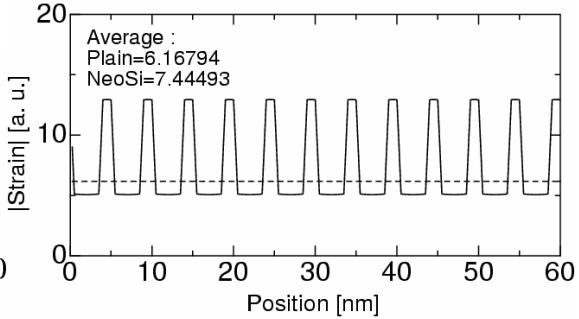

最近宇野らはナノスケールのシリコンと  $\text{SiO}_2$  の周期構造においてフォノンの振動モードと状態密度を理論的に計算した。それによれば、低エネルギーのフォノン振動モードにおいては、ひずみが相対的にやわらかい材料である  $\text{SiO}_2$  部分に集中しており、その結果、ナノ結晶シリコン中に存在確率の高い電子との散乱は抑制される可能性があるということである。またフォノンの状態密度は、周期構造を作るだけでバルクのシリコンの場合と全く異なる分散関係になっており、低エネルギー領域にいくつもギャップが存在し、高エネルギー領域では完全に離散化していることがわかる。このようにフォノンの状態密度にギャップができるとそのギャップに対応する周波数に対応するフォノンは存在することができない。すなわち、電子の散乱メカニズムのひとつのフォノン散乱において、フォノンのとりうるエネルギーに制約ができるために、散乱が抑制される可能性があるということである。これらの理論と実験の対応を明らかにするためには更なる知見が必要であるが、ナノスケールであればこそ現れてくる新たな現象として非常に興味深い。

### 3.2.3.3 得られた研究成果の評価および今後期待される効果

本研究では、ナノ結晶シリコンの堆積とシリコンテクノロジの組み合わせにより平面型電子放出素子を作製し、電子放出を観測した。また、表面の平坦化が素子の特性向上に重要なことを明らかにし、平坦化によって最大数%の効率をもつ素子の作製に成功した。放出電子のエネルギー分布の測定により、この素子においてもポーラスシリコンで報告されているような弾道的な電子放出が起こっていることがわかった。これらのこととは、従来ポーラスシリコンで報告されていた高効率の平面型弾道電子放出素子を、

ドライプロセスによる堆積でも作製できるということを示したものである。これにより、任意の基板に作製したり、別のシリコンデバイスとの組み合わせを考えたりすることで、さらなる高機能素子への展開が期待される。また、物理的にも、なぜこのようなナノ結晶シリコンと酸化膜の周期的な構造を通過するときに散乱が抑制されているように見えるのかについては非常に興味深い問題である。ただ、素子の安定性に関してはポーラスシリコンに比べてまだ不十分であり、更なるプロセスの最適化が必要であると考えている。

### 3.2.4 NEMSメモリデバイス

#### 3.2.4.1 はじめに

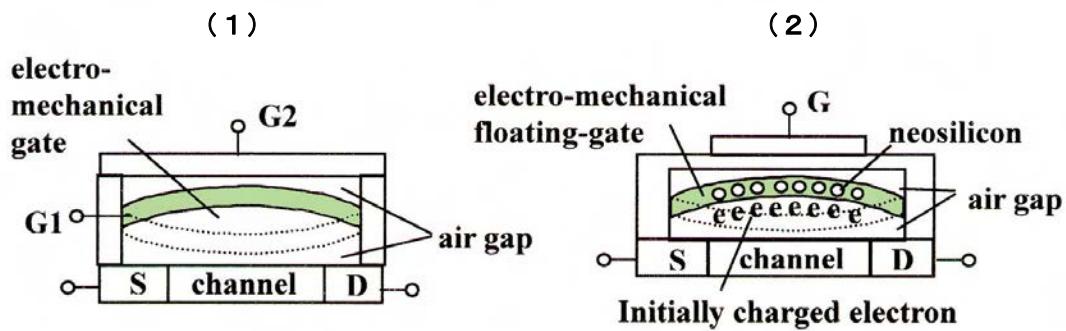

半導体微細加工技術の飛躍的な進展は、MOSFET の高速動作、高集積化、消費電力低減といった VLSI に課せられた厳しい要求をさらに上回る勢いで実現してきた。この加工技術の発展は、マイクロマシンという新たな分野を生み出すこととなり、センサやアクチュエータ等、既に多くの面で実用化がなされている。このマイクロマシンは、これまで MEMS (Micro Electro-Mechanical Systems) と呼ばれてきたが、近年ではさらに小さいナノスケール構造を持つ物、NEMS (Nano Electro-Mechanical Systems) の研究が盛んに行なわれている。NEMS の実現により、従来は遅いというイメージであった機械的動作が高速化する。実際に最近、シリコンカーバイドを用いて作製された、長さ  $1.1 \mu\text{m}$  の微小両持ち梁構造で、共振周波数  $1\text{GHz}$  を達成したという報告がなされた[1]。これは機械的な動作でも十分に小さいものならば非常に高速な動作ができるることを示したものであり、今後の微細化技術の進歩によって、更なる超高速動作が期待される。動作速度が  $\text{GHz}$  程度まで高速化することで、新しい流れとして NEMS を電子デバイスに応用する可能性が現れてくる。本研究では、NEMS の高速性を活かした、新しいメモリデバイスの提案を行なう。本報告では、まず提案内容と素子の動作原理について述べ、動作速度の見積の結果を示す。つづいて、この素子の心臓部である可動フローティングゲート構造を紹介し、その後、素子作製プロセスについて述べる(3.2.4.2)。また、可動フローティングゲート構造の機械的特性について、理論、実験の両面から考察した結果についても報告する(3.2.4.3)。

#### 3.2.4.2 NEMSメモリデバイスの提案

##### 3.2.4.2-1 動作原理

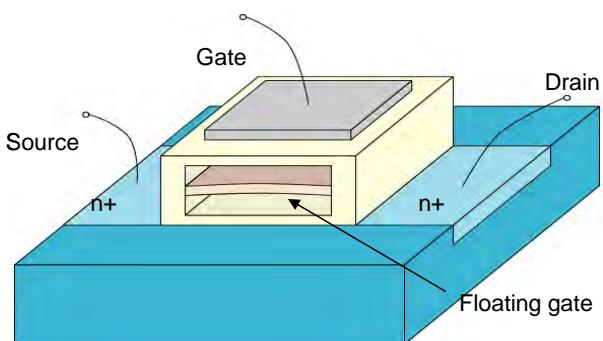

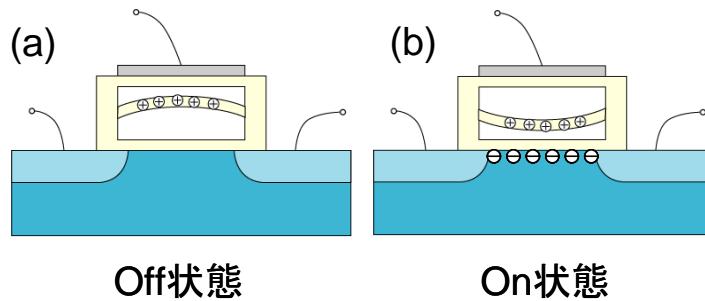

図 3.2.4.1 に、提案する素子構造を示す。MOS トランジスタにおけるチャネルと、その直上のゲート電極間が空隙となっており、その間に可動フローティングゲートを配置した構造となる。このフローティングゲートとは、一般的にフラッシュメモリのそれとは機能的に異なる。フラッシュメモリの場合、電気的に浮いているという意味合いであるが、本素子においてこのフローティングゲートは、電気的にも、さらには構造的にも浮いた状態にある。本素子の動作においては、あらかじめこの可動フローティングゲート層に電荷が蓄積された状態にあることが必要である。この電荷に外部から電圧を加えることで、フローティングゲート層を機械的に変位させる。それにより、チャネル部の表面電位が変化し、閾値電圧がシフトする。この両持ち梁構造の可動

図 3.2.4.1 NEMS メモリ素子構造の模式図

フローティングゲートを、作製時にあえて湾曲させ、この梁が双安定性を持つことで、この素子は不揮発性メモリとして動作する。そしてこの安定点間の変位は、上部電極に電圧を印加する事で生じる電極とフローティングゲート間の静電気力によって行なう。例えばフローティングゲートが図 3.2.4.2(a)のような状態にあるとき、フローティングゲート内の電荷がチャネル部の表面電位に大きく影響を与えておらず、コンダクタンスの小さい“OFF 状態”である。ここで上部電極にフローティングゲート内の電荷と同極の電圧を印加する。この力によってフローティングゲートが下部に押し下げられ、図 3.2.4.2(b)の状態となる。この状態ではコンダクタンスの高い“ON 状態”となる。これらの事から、電気的に書き換え可能な不揮発性のメモリデバイスとして動作させる事が可能となる。

図 3.2.4.2 NEMS メモリ素子の ON と OFF

### 3.2.4.2-2 動作速度

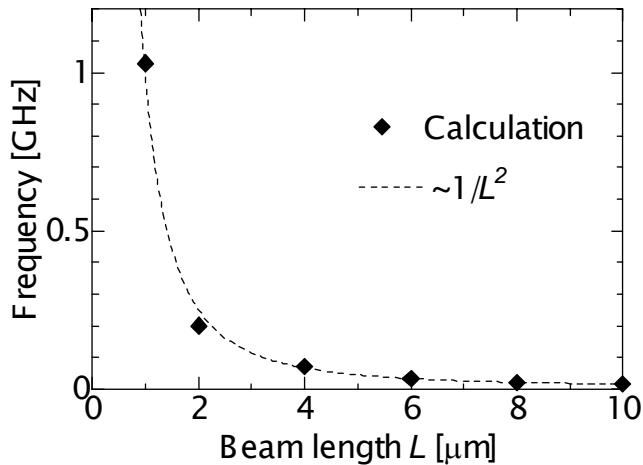

次にこの NEMS メモリデバイスの動作速度について述べる。このデバイスでは ON/OFF の切り替えをフローティングゲートの変位で行なうので、ここでは上に凸となっているフローティングゲートが下に凸となるまでの時間を求める事になる。一次元モデルを考え、電界によって梁が加速される方向に働く力と、梁が圧縮される事によって働く弾性力を考慮した梁の運動方程式を解くことにより変位に要する時間を得る事ができる。この計算によれば、梁のサイズ  $1 \times 1 \times 0.1 \mu\text{m}^3$  では周波数  $1.7 \text{ GHz}$ 、 $0.1 \times 0.1 \times 0.01 \mu\text{m}^3$  では  $17 \text{ GHz}$  いう値が見積もられた。また、有限要素法をもちいた梁構造の動作ミュレーションにおいても、長さ  $1 \mu\text{m}$  の梁について、約  $1 \text{ GHz}$  程度の振動数が予測されている（図 3.2.4.3）。現在一般的に使用されているフラッシュメモリの情報書き換え時間が数百ナノ秒であるから、この速度は不揮発性メモリとしては驚異的である。

図 3.2.4.3 次元有限要素法を用いて計算した梁長さと振動数の関係

### 3.2.4.2-3 可動フローティングゲート

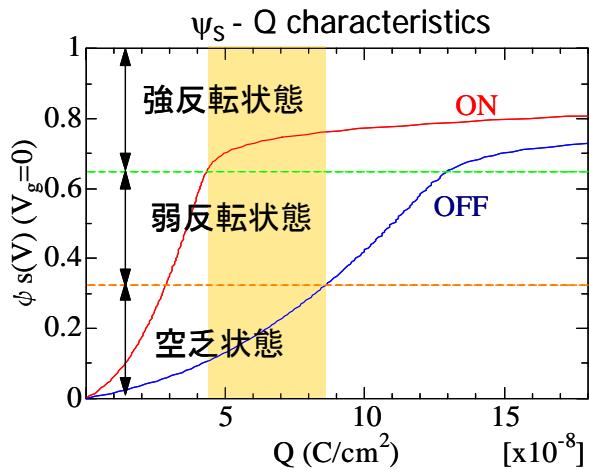

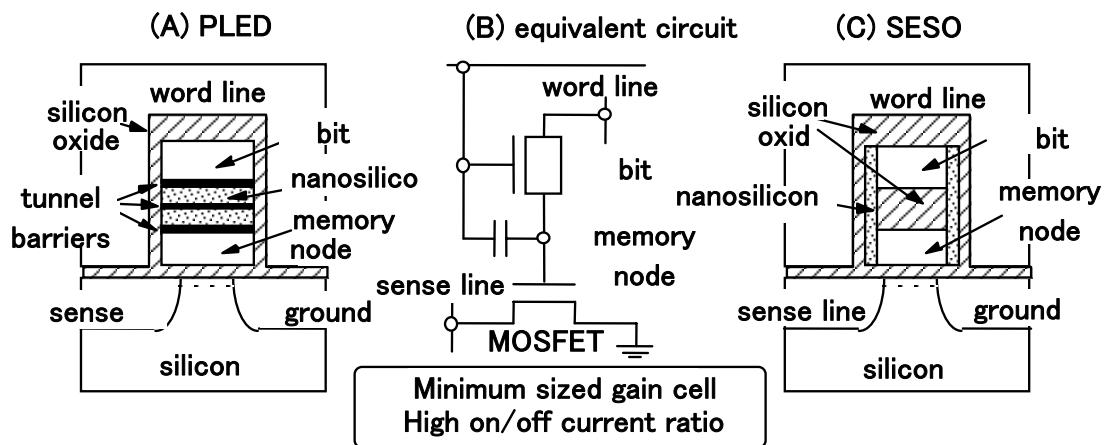

本素子の特徴である可動フローティングゲートには、素子動作のために、1) 電荷を保持できる機構である事、2) 保持する電荷量が制御可能である事、3) 変形しやすい材料である事、が要求される。この条件を全て満たす構造が、 $\text{SiO}_2$  薄膜中にナノ結晶シリコンを内包した構造である。このナノ結晶シリコンはシランガスをプラズマ分解して気相中で成長させる事により得られる、粒径 8 nm 程度で均一な球形の微小単結晶である。素子の一次元近似モデルを用いて考えると、保持電荷と Si 基板の表面電位の関係が導かれる。素子動作の条件として、ON 状態の時には Si 基板表面は強反転状態、OFF 状態の時には空乏又は蓄積状態である事が挙げられる。空洞の高さを 200 nm、フローティングゲート変位量を 50 nm とした場合の表面電位と電荷の関係を図に示す。条件を満たすのは図内の黄色で示された領域で、 $10^{-8} \text{ C cm}^{-3}$  のオーダーとなる。ナノ結晶シリコンは気相中で成長し、シャッターの開閉により  $10^{-8} \text{ cm}^{-3}$  オーダーで堆積量を制御可能なので、NEMS メモリデバイスに必要とされる電荷量を制御する事は十分可能であるといえる。

図 3.2.4.4 1 次元近似モデルで計算した保持電荷と表面電位の関係

### 3.2.4.2-4 素子作製プロセス

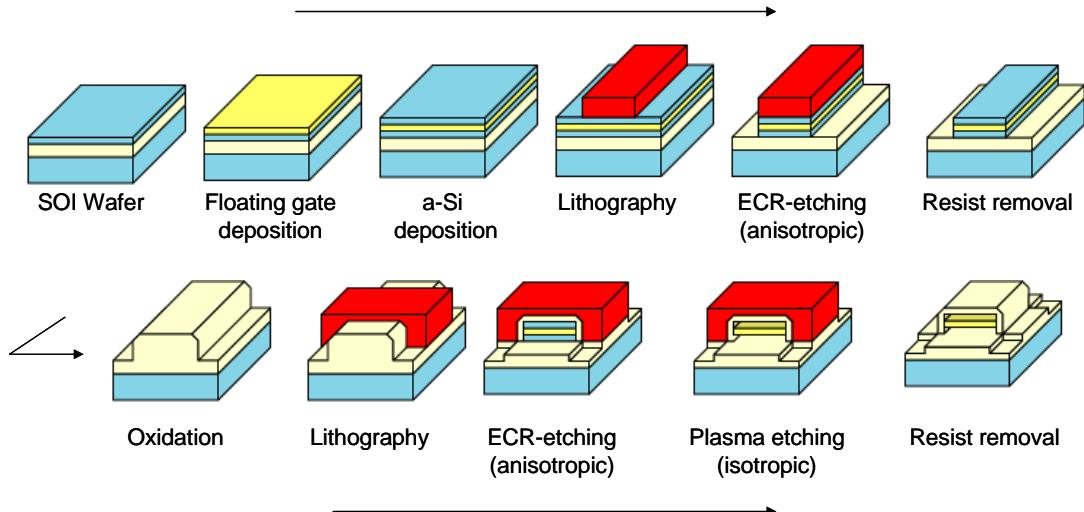

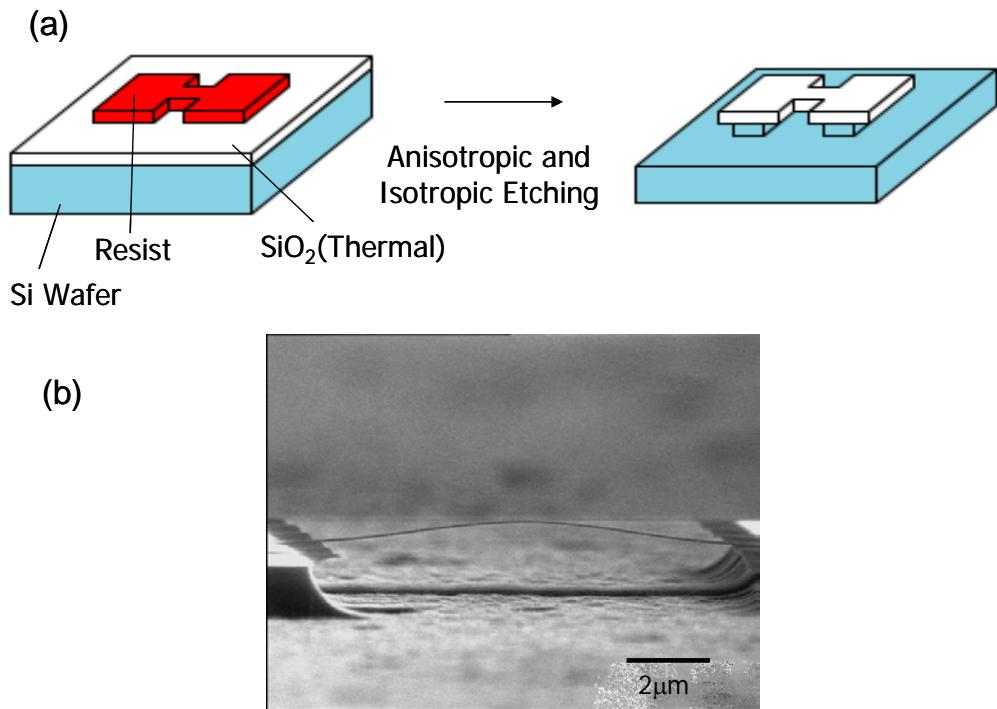

素子作製のプロセスを図 3.2.4.5 に示す。ここではまず 2 重空洞構造が作製可能かどうかの確認のための素子である。基板は SOI ウェハーを用いた。ここでは SOI 層を犠牲層 Si として用いる。基板酸化により  $\text{SiO}_2$  層を形成し、その上にジシランを用いた熱 CVD 法によりアモルファスシリコンを堆積する。この  $\text{SiO}_2$  層が最終的にフローティングゲートに、アモルファスシリコンが犠牲層となる。リソグラフィとしは、アモルファスシリコン層の上に、図のようなラインをパターニングし、パターンを基板に転写するために、異方性エッチングを行なう。エッチングは SOI 層が完全にエッチングされて、その下の酸化膜層を少しオーバーエッチするくらいが望ましい。レジスト剥離後、ドライ酸化により  $\text{SiO}_2$  膜を形成する。これは最終的には両持ち梁構造の支柱部分にあたる。再度リソグラフィを行なう。ここでは 1 回目のラインと垂直に交差するようなラインをパターニングする。再び異方性エッチングを行なう。これによって一回目のパターンによって形成された部分の断面を露出させる。ここでも SOI 層が完全にエッチングされた状態にする事が理想だが、ここでは完全にエッチングしきらなくても構わない。最後に等方性エッチングを行なう。フローティングゲートや支柱部を残して、犠牲層 Si のみをエッチングする。先の異方性エッチングで残った SOI 層も、このプロセスにて完全に除去される。以上で構造の完成となる。以上のようなプロセスを行なった結果、図 3.2.4.6

図 3.2.4.5 2重空洞構造作製プロセス

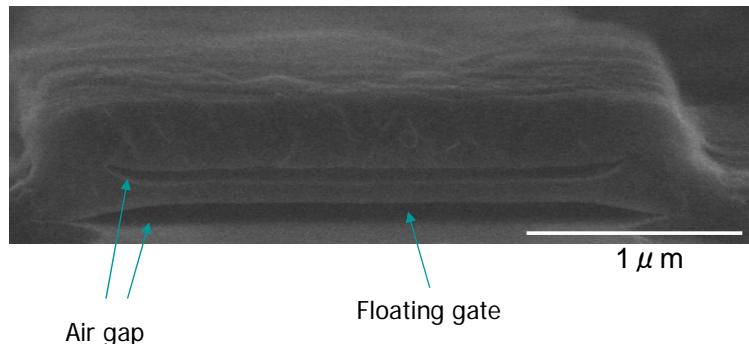

のような結果が得られた。リソグラフィによって決まる素子寸法は、横  $3\text{ }\mu\text{m}$ 、奥行き  $3\text{ }\mu\text{m}$  である。フローティングゲート層及び上部酸化膜が倒壊することなく、目的とする構造が作製された事が確認された。

図 3.2.4.6 作製した2重空洞構造

### 3.2.4.3 可動フローティングゲート構造の機械的特性

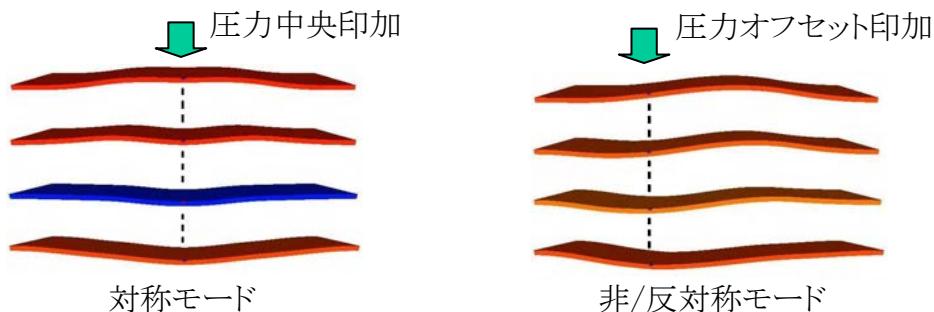

#### 3.2.4.3-1 機械的特性

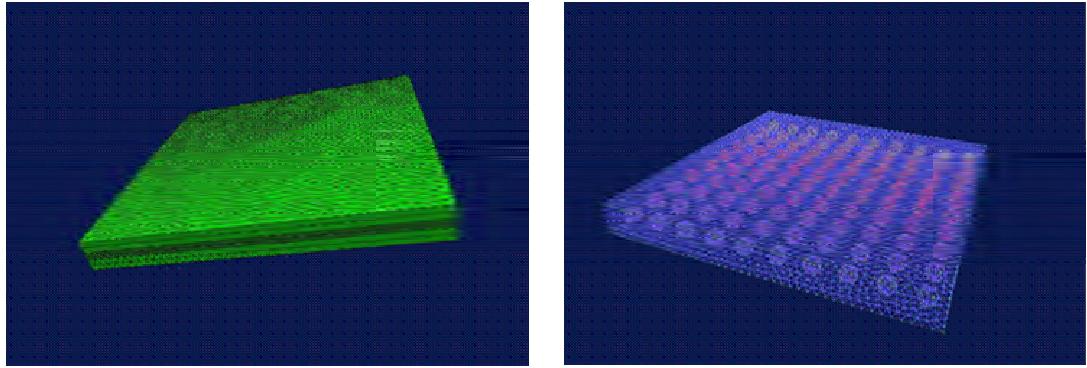

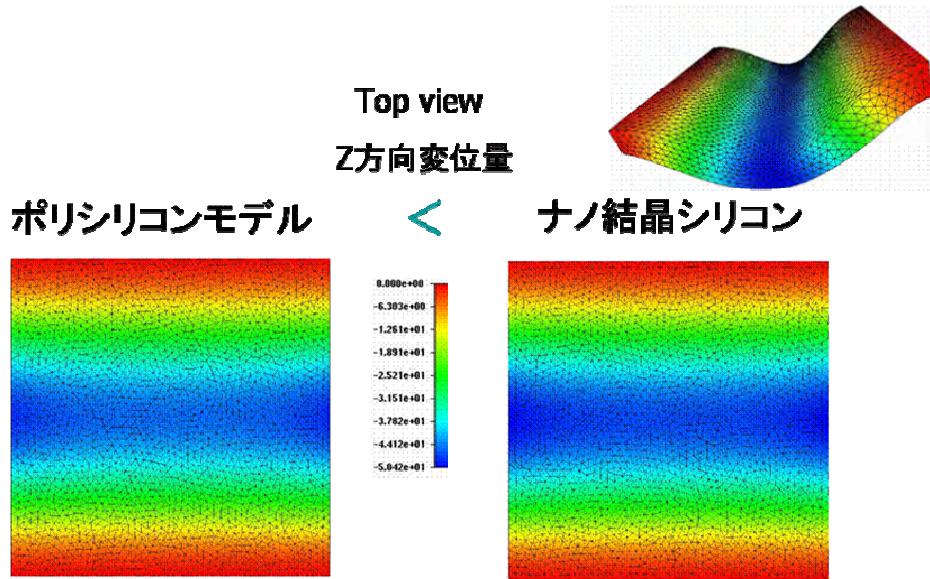

この素子の動作解析を行う上で可動フローティングゲート構造の機械的特性を知ることは極めて重要である。ここで、機械的特性とは材料の変形しやすさ、やわらかさについてである。やわらかい梁を用いることは、低電圧動作に有利である。ここでは、三次元有限要素法解析により、図 3.2.4.7 のようなモデル(左：ポリシリコン、右：ナノ結晶シリコン)の機械的特性の違いを調べた。これらのモデルは全体の寸法は全く同じとし、同一の境界条件を与え、さらに電荷保持部となるポリシリコンとナノ結晶シリコンの体積を等しくした場合について、その変位量の比較を行う事で、変形しやすさの検討を行なった。その結果、右のナノ結晶シリコンモデルの方が中央の青色が濃く、より大きく変形している事が判る。これは  $\text{Si}_2$  に対して硬いシリコンを内包させる場合、一

図 3.2.4.7 有限要素法による解析モデル(左：ポリシリコン、右：ナノ結晶シリコン)

様ではなくある程度局所的に配置する事でより変形しやすくする事が可能であり、機械的特性の観点からもナノ結晶シリコン内包梁構造はこの素子に対して有効であるということがわかった。

図 3.2.4.8 有限要素法による解析結果(左：ポリシリコン、右：ナノ結晶シリコン)

### 3.2.4.3-2 負荷試験

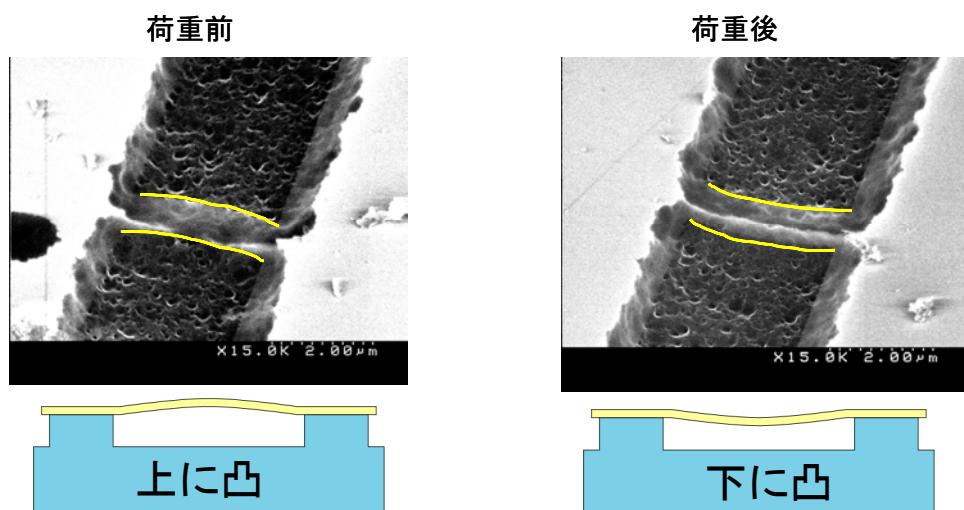

素子の試作段階において、図3.2.4.9(a)のようなプロセスで $\text{SiO}_2$ 一層のみの構造を作製すると、図3.2.4.9(b)のように、上に凸となるように湾曲した構造が得られた。これは、熱酸化によってSiから $\text{SiO}_2$ に変化した際の体積膨張により、 $\text{SiO}_2$ 薄膜に圧縮応力が働き、その後下地のSi部がエッチングされることで支持が無くなり、変形したものと考えられる。このような構造で実際に双安定性が得られるのかどうかを確認するために、作製した両持ち梁に試験針によって直接荷重をかける実験を行なった。図3.2.4.10に荷重前後の素子の電子顕微鏡写真を示す。試験前では上に凸であった両持ち梁が、試験後では下に凸となっていることが確認できる。両持ち梁の弾性ポテンシャルが機械的な双安定性を持っていることを直接観測することができた。

図 3.2.4.9 (a)  $\text{SiO}_2$  層構造作成法 (b) 作製した  $\text{SiO}_2$  ブリッジ構造

図 3.2.4.10 荷重試験前後での梁の形状の変化の観測

### 3.2.4.4 得られた研究成果の評価および今後期待される効果

本研究は微細化によって可動構造物が高速動作するようになるナノエレクトロメカニカルシステム(NEMS)を電子デバイスに応用するという、極めて独創的な試みであり、素子提案から作製プロセスまでの一貫した研究はこれまで世界的にも例をみない。動作速度の見積からは 1GHz 動作が可能であることが分かった。また、可動フローティングゲートにナノ結晶シリコンを埋め込み、電荷保持に用いるというアイデアは、フローティングゲート内の電荷制御という面と、機械的なやわらかさが必要という面の両面から優位であることが分かった。また、不揮発性メモリ動作の要である双安定性も確認された。これらの基礎的な評価の結果は、NEMS メモリの研究を提案のレベルからよりリアルな段階へステップアップさせといえる。

実現可能性があきらかになってきたところで今後の課題としては、まずは実際に電気的に動作する素子の作製である。また、この NEMS の電子デバイス応用ということについては、本研究で提案した高速不揮発性メモリのみならず、様々な素子に応用可能であると考えられ、本研究は必ずやその礎となるものであると信じている。

#### 参考文献

- [1] X. M. H. Huang *et. Al.*, Nature 421, 496 (2003).

### 3. 3 微細構造電気特性評価グループ（ケンブリッジ大学）

Cavendish Laboratory, Microelectronics Research Centre,

M.A.H. Khaladalla, Y.T. Tan, T. Kamiya, Z.A.K. Durrani and H. Ahmed

#### 3.3.1. Introduction:

The development of novel nanocrystalline silicon (nc-Si) materials [1, 2], consisting of crystalline silicon grains ~10 nm in size isolated by thin amorphous grain boundaries (GBs), has raised the possibility of a dramatic increase in the functionality of the silicon chip. The grains ‘naturally’ form silicon quantum dots, isolated by tunnel barriers at the GBs, over the entire area of a nc-Si thin film, leading to the observation of strong quantum confinement and single-electron charging effects [3] in the electronic transport across the film which complement the novel optical properties of nc-Si. Advanced quantum dot and single-electron transistors (SETs) can then be fabricated in the films, without the need for lithographic definition of the quantum dots. If the grains are ~10 nm or less in size, and the GB tunnel barriers are ~100 meV or higher, then the single-electron charging energy and tunnel resistances can be large enough for room temperature operation of the nc-Si QDs and SETs, opening a promising route for the development of room-temperature nano-electronics in large-scale integrated (LSI) systems.

One of the most promising devices for future nano-electronic LSI is the SET [4]. In this device, the single-electron charging effect is used to control precisely the charging of individual electrons on a conducting island. Electrons are transferred to the island from source and drain terminals by tunnelling across potential barriers. The charging of the island by single electrons can be controlled using a gate terminal. The SET has the advantages of very low power consumption, better immunity from statistical charge fluctuation and very high scalability compared to conventional complementary metal-oxide-semiconductor devices.

The practical application of SETs to LSI systems requires room temperature operation and silicon process compatibility. For room temperature operation, the single-electron charging energy of the island,  $E_c = e^2/2C_\Sigma$  ( $C_\Sigma$  is the total island capacitance and ‘e’ is the elementary electronic charge) must be large compared to the thermal energy  $\sim k_B T \approx 26$  meV ( $k_B$  is Boltzmann’s constant and temperature  $T = 300$  K). Therefore, the value of the  $C_\Sigma$  must be  $\sim 1$  aF or less and in practice this implies that the charging island must be  $< 10$  nm in size. In addition, electrons must be localised on the island, which requires a large tunnel barrier resistance as compared to the quantum resistance  $R_Q \sim 26$  k $\Omega$  at the operating temperature. In addition, for room temperature operation, the tunnel barrier height should be at least  $\sim 100$  meV, i.e. high in comparison with  $k_B T$  at room temperature. In addition to the work discussed in this report, there have been only a few demonstrations of silicon SETs operating at room temperature (e.g. see Refs. [5-8]). In these devices, the islands were formed by discontinuous ultra-thin polycrystalline silicon (poly-Si) layers, or were defined in crystalline silicon-on-insulator films using high-resolution lithography and controlled oxidation.

The GB tunnel barrier isolating the grains is of great importance, not only in determining the bulk resistivity of the nc-Si films, but also in determining the extent of the electrostatic and tunnel coupling between different grains, especially at low temperatures. These additional quantum effects can lead to the nc-Si thin film behaving as a system of coupled quantum dots [9-11]. In recent years, similar systems have become of great interest in the development of novel silicon-based quantum information processing devices in the solid state [12].

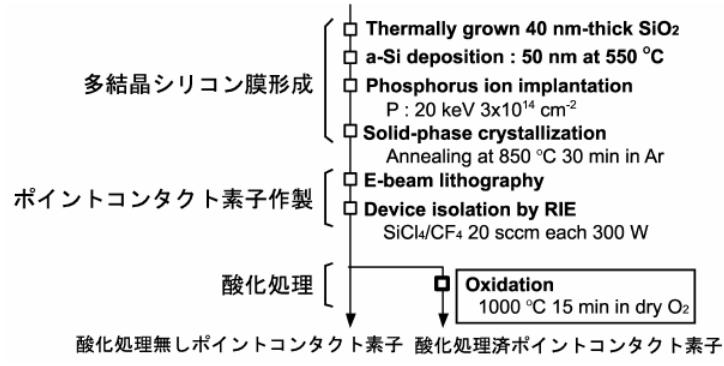

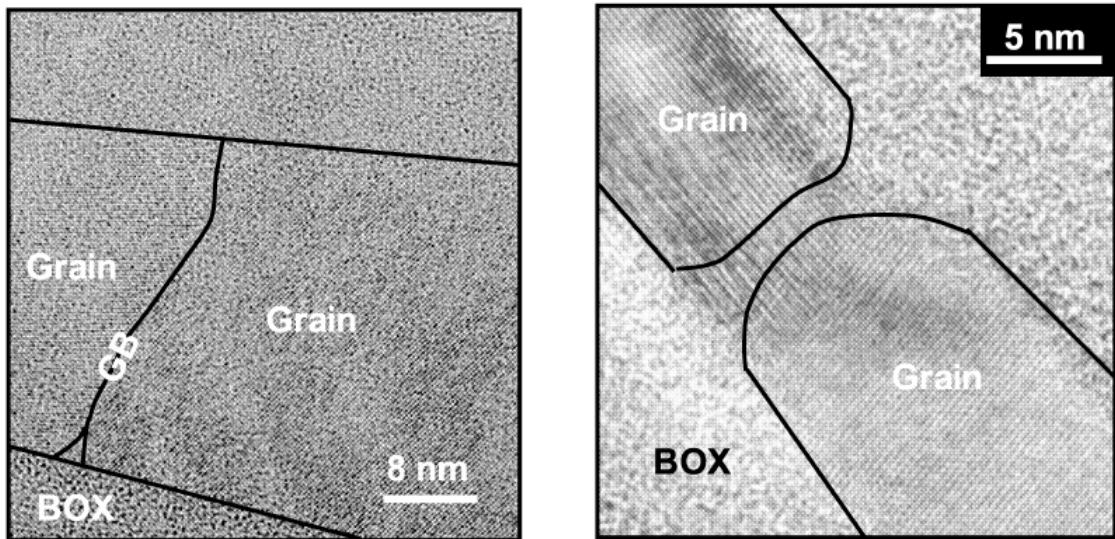

This report discusses research on electron transport in nc-Si devices at the Microelectronics Research Centre, University of Cambridge, during the CREST programme. The report is organised as follows. We begin by discussing the fabrication and characterisation of nanowire SETs in solid-phase crystallised polycrystalline silicon material [13], where the grains were up to 50 nm in size, and the devices operated up to 15 K (Sec. 2). We then consider our work to improve the operating temperature of the SETs by using nc-Si point contacts [14, 15] (Sec. 3.1), and the development of room temperature nc-Si point contact SETs [16-19] (Sec. 3.2). Engineering the GB structure and potential barrier is discussed in Sec. 3.3 [20-22]. We discuss inter-grain electron coupling effects in Sec. 4. These novel effects include electrostatic [9] (Sec. 4.1) and electron wavefunction (Sec. 4.2) coupling effects [10, 11], and the latter effect is observed for the first time in silicon. Finally, in Sec. 5 we conclude this report and assess the significance of our results.

### 3.3.2. SETs in polycrystalline silicon [13]:

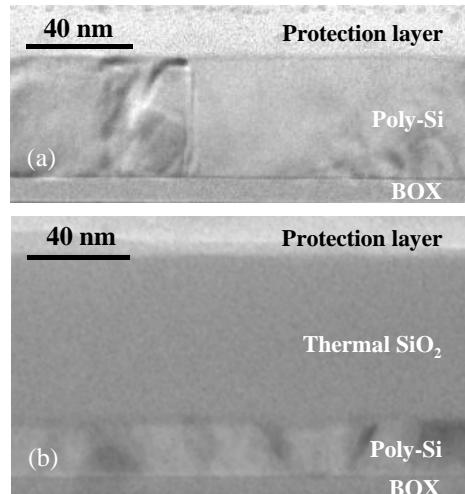

The initial stages of the project concerned the fabrication and detailed characterisation of lateral, side-gated nanowire SETs in solid-phase crystallised (SPC) polycrystalline silicon films, deposited on SiO<sub>2</sub> layers grown on silicon substrates. A Coulomb staircase was observed at 4.2 K, and this was fully modulated by the side-gate voltage. Conductance oscillations with a sudden switch in period ('two-period' oscillations) were observed in nanowires fabricated on only 10-nm-thick buried oxide layers, while single-period oscillations are observed in nanowires fabricated on 40-nm-thick buried oxide layers. The two-period oscillations were attributed to the formation of a charge layer in the silicon substrate. The single-electron effects were studied in detail as a function of the nanowire dimensions, and annealing or oxidation treatments. The effects were then correlated to the structure of the polysilicon film, characterized using transmission electron microscopy (TEM), Raman spectroscopy, and electron spin resonance (ESR) analysis.

Our polycrystalline silicon material was prepared as follows: A 50 nm thick amorphous silicon film was deposited at 550°C by PECVD on a 10 nm thick gate quality silicon oxide layer grown on a crystalline silicon substrate (*p* doped, at  $5 \times 10^{14} \text{ cm}^{-3}$ ). The amorphous silicon film was heavily doped to  $5 \times 10^{19} \text{ cm}^{-3}$  using phosphorous ion-implantation and then crystallized into polycrystalline silicon using thermal annealing at 850°C for 30 minutes. TEM analysis indicated that the grains varied from ~5 nm – 50 nm in size, and the average grain size was ~20 nm. Lateral side-gated polysilicon nanowires of various geometry were defined in the film using electron-beam lithography on polymethyl methacrylate (PMMA) resist and reactive-ion-etching in a 1:1 plasma of SiCl<sub>4</sub> and CF<sub>4</sub>. Figure 3.3.1 shows a SEM image of a device where the nanowire is 1 μm long and 40 nm wide. Nanowires of various dimensions (width: 40 nm–90 nm, length: 500 nm–1.5 μm) were fabricated. After the nanowires were defined, they were processed further using (1) thermal oxidation at 1000 °C for 15 minutes, (2) annealing in argon at 1000 °C for 15 minutes or (3) annealing followed by oxidation. The oxidation process reduced the cross-sectional area of the nanowire by ~ 10 nm and passivated the defect states. The annealing process modified the defect state density at the GBs, at the Si/SiO<sub>2</sub> interface and along the etched surfaces, and increased the grain size.

The drain-source I-V characteristics at 4.2 K, from an oxidized nanowire where the pre-oxidized width was 50 nm and length was 1.5 μm, are shown in Fig. 3.3.2. The characteristics show single electron charging effects which may be associated with the charging of the polycrystalline silicon grains along the nanowires, isolated by tunnel barriers at the GBs. A zero-current Coulomb gap region is observed which oscillates in

width with the gate bias, leading to trapezoidal charge stability regions at the origin in the  $V_{ds}$ - $V_{gs}$  plane. The period of oscillation changes abruptly at  $\sim 0.5$  V, and a larger period is observed for negative gate bias. This ‘two-period’ behaviour can be attributed to the formation of a charge layer in the silicon substrate, which changes the gate-island capacitance and does not occur in devices with thicker buried oxide layers. Current steps are also visible in the  $I_{ds}$ - $V_{ds}$  plane, which may be attributed to a Coulomb staircase. Figure 3.3.3 shows the temperature dependence of the ‘two-period oscillations’ in the drain-source current as a function of gate voltage. We observe that the oscillations become weaker as the temperature increases and at a temperature of 15 K, the Coulomb blockade effect is overcome and the oscillations disappear completely.

The dependence of the device characteristics on nanowire dimensions was investigated in detail. The oscillation periods increased when the nanowire length was increased from 500 nm–1.5  $\mu$ m, and decreased when the nanowire width was increased from 50 nm to 60 nm. Wider wires showed only Ohmic conduction. We explained this behaviour by considering the effect of the nanowire dimensions on the grains within. The longer the nanowire, the higher was the probability of smaller grains existing along the nanowire, with smaller gate capacitances and larger observed oscillation periods. The decrease in the oscillation period with increasing width implied an increase in the lateral area of the charging island. Therefore, the electric field distribution between the side-gates and the charging island had to be considered in three dimensions, and the increase in area was associated with fringing fields below the plane of the side-gates and nanowire.

We also characterised the structure of our polycrystalline silicon films using TEM, Raman and ESR spectroscopy. The ESR spectra indicated that annealing prior to oxidation decreased the passivating effect of the oxidation process, due to segregation of dopants to the GBs and Si/SiO<sub>2</sub> interfaces. These effects caused an increase in the resistance of annealed nanowires. The single-electron oscillation periods in the corresponding devices were also smaller, associated with an increase in grain size. The Raman spectroscopy showed that the Raman peak in the as-deposited polycrystalline silicon film associated with the amorphous silicon component of the film disappeared after thermal treatment. In the case of argon annealing, the formation of crystalline silicon grains from the amorphous silicon reduced the intensity of this peak while oxidation caused the formation of SiO<sub>x</sub>, which also reduced the intensity. As amorphous silicon (found in the GBs) oxidises more readily as compared to crystalline silicon, we expected the formation of SiO<sub>x</sub> to encapsulate the crystalline silicon grains.

### 3.3.3. SETs in nanocrystalline silicon [14-22]:

In Sec. 2, we discussed the operation of side-gated nanowire SETs in SPC polycrystalline silicon material. These devices showed single-electron effects only up to  $\sim 15$  K, due to the large grain size (up to  $\sim 50$  nm) and the relatively long dimensions of the nanowire (500 nm minimum). It is possible to improve the SET operating temperature considerably by using nanocrystalline silicon (nc-Si) deposited by VHF PECVD, with small grains  $< 10$  nm in size, in conjunction with reducing the nanowire length to  $\sim 50$  nm or less to form a ‘point-contact’ SET. In this section, we discuss the fabrication and characterisation of point-contact SETs in as-deposited nc-Si (Sec. 3.1), and in nc-Si where a low-temperature oxidation and annealing process is used to selectively oxidise the GBs to raise the tunnel barrier height (Sec. 3.2). The later devices are capable of operating even at room temperature. We also discuss control of the inter-grain tunnel barrier by ‘GB engineering’ (Sec. 3.3).

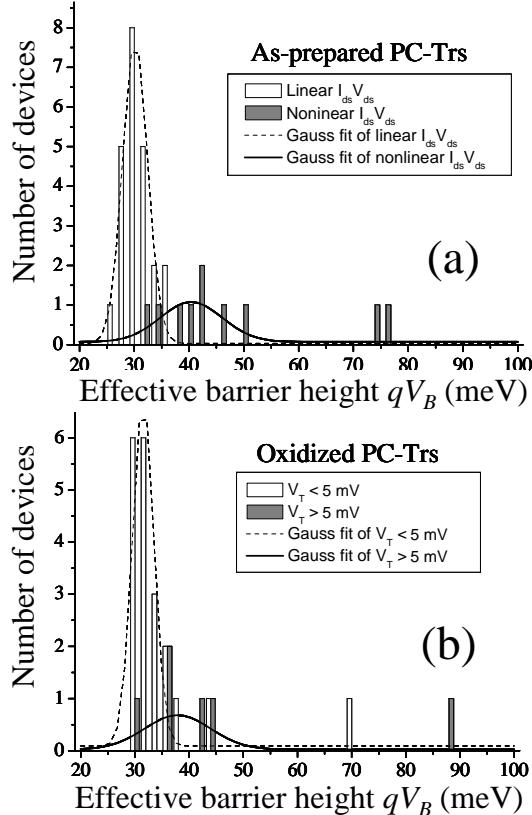

### 3.3.3.1. Point-contact SETs in as-deposited nanocrystalline silicon [14-15]:

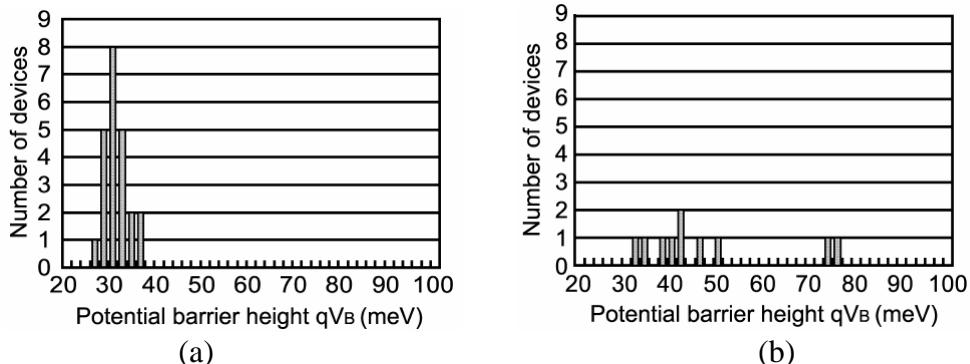

Point contact SETs fabricated in as-deposited nc-Si films showed single-electron effects up to 60 K. Our films were phosphorus-doped and deposited at 300°C by VHF PECVD. TEM and Raman spectroscopy was used to determine the grain size, crystalline volume fraction and GB thickness. The single-electron effects could be associated with islands formed by crystalline silicon grains only  $\sim$  4 nm in size, isolated by amorphous silicon regions only  $\sim$  1 nm in thickness. The structural characteristics of the nc-Si film could be correlated to the electrical behaviour. The electrical transport mechanism at high temperatures was attributed to percolation conduction across a distribution of tunnel barriers, with a maximum barrier height of  $\sim$  40 meV.

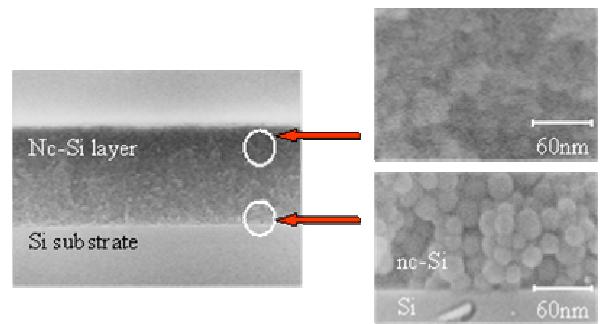

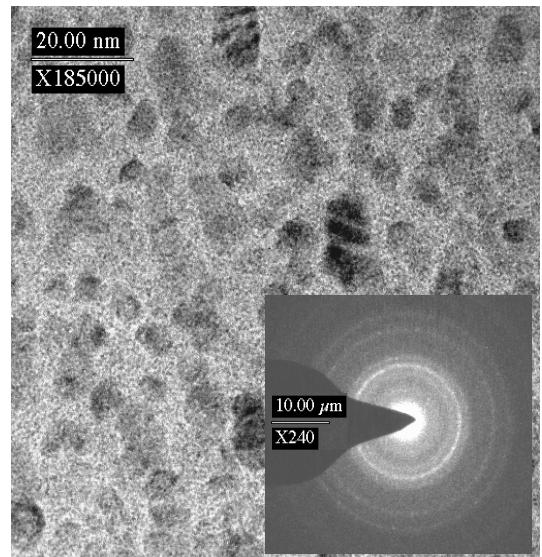

Our nc-Si films were 30 nm thick, deposited using VHF PECVD from a SiF<sub>4</sub> : H<sub>2</sub> : SiH<sub>4</sub> gas mixture. The films were deposited on a 150 nm thick silicon oxide layer grown thermally on top of *n*-type crystalline silicon. The flow rates of the SiF<sub>4</sub>, H<sub>2</sub> and SiH<sub>4</sub> were 30, 40 and 0.25 sccm. The films were doped *in situ* with PH<sub>3</sub> (1% diluted with H<sub>2</sub>), where the concentration of PH<sub>3</sub> in SiH<sub>4</sub> was 2%. The VHF frequency was 100 MHz, the VHF power was 40 W and the reactor pressure was 200 mTorr. The carrier concentration and electron mobility, measured at room temperature by Hall measurements, were  $3 \times 10^{20}$  /cm<sup>3</sup> and 1.8 cm<sup>2</sup>/Vs respectively. Figure 3.3.4 shows a TEM image of the nc-Si film, with uniformly distributed crystalline silicon grains embedded in an amorphous silicon matrix. The grain sizes range from  $\sim$  4–8 nm. The diffraction rings shown in the inset imply that the film contains crystalline silicon and is not entirely amorphous. Additional high-resolution TEM analysis using Fresnel contrast indicated that the GBs were decorated with fine layers of amorphous silicon less than 1 nm thick. Raman spectroscopy was used to confirm the average grain size ( $\sim$  4 nm) and determine that the crystalline volume fraction was 70%. Details of the growth, structure, and the bulk transport properties of these films can be found in our work in ref. [15].

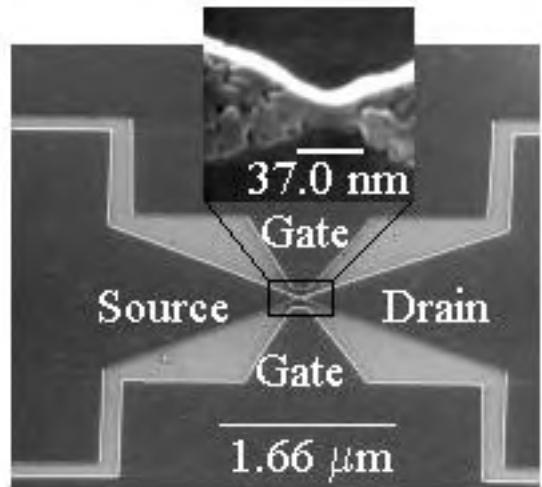

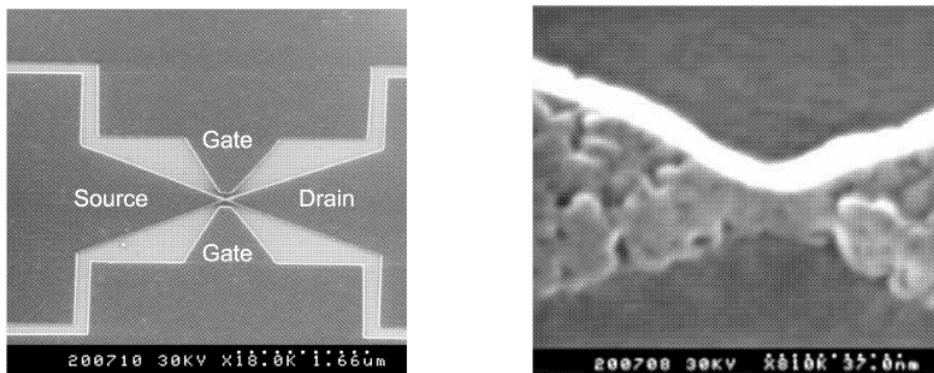

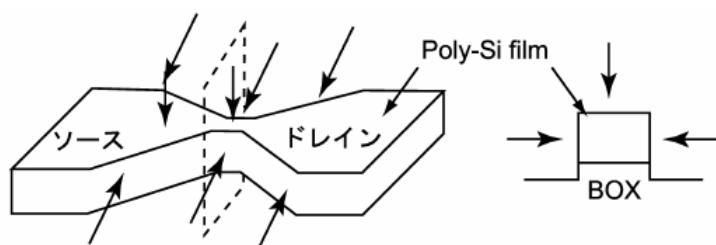

The point contact SETs were defined using electron-beam lithography in polymethyl methacrylate resist, and reactive-ion-etching in a mixture of SiCl<sub>4</sub> and CF<sub>4</sub> gases (20 sccm each) at 13.56 MHz, 300 W and 20 mTorr. A typical point contact had a width of 20 nm. Ohmic contacts were formed to the structure using aluminium contact pads. Figure 3.3.5 shows a scanning electron micrograph of a SET.

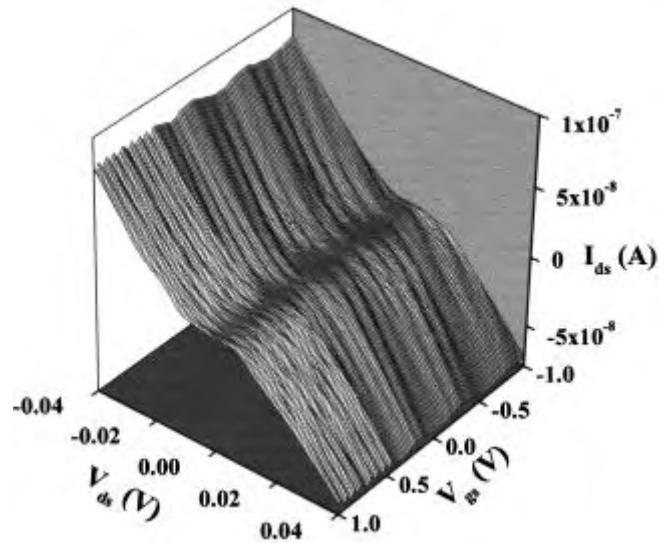

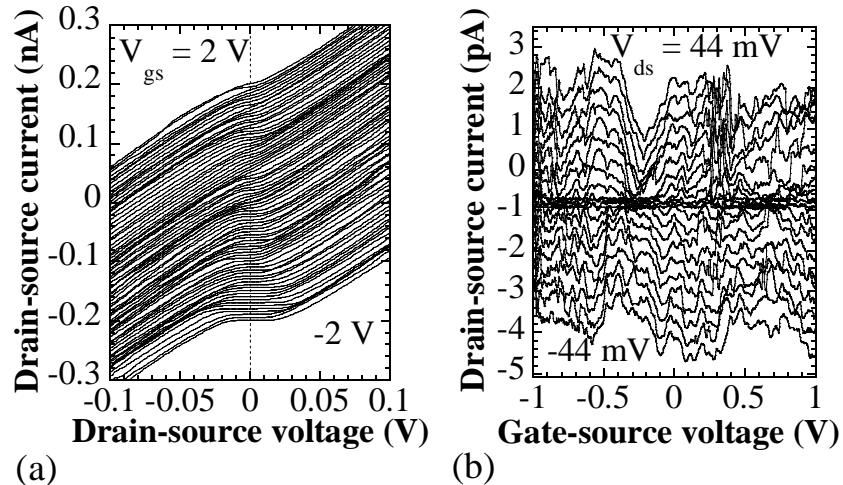

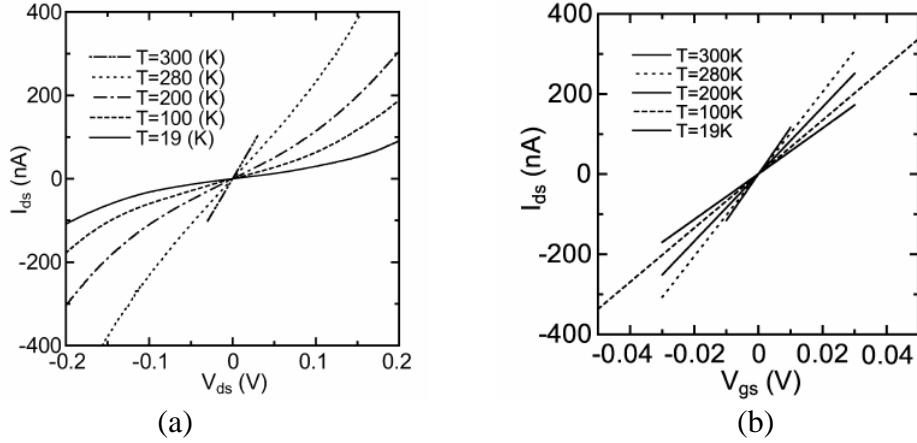

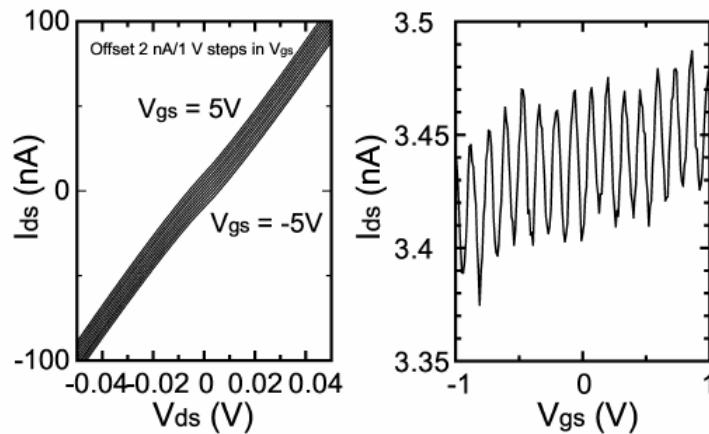

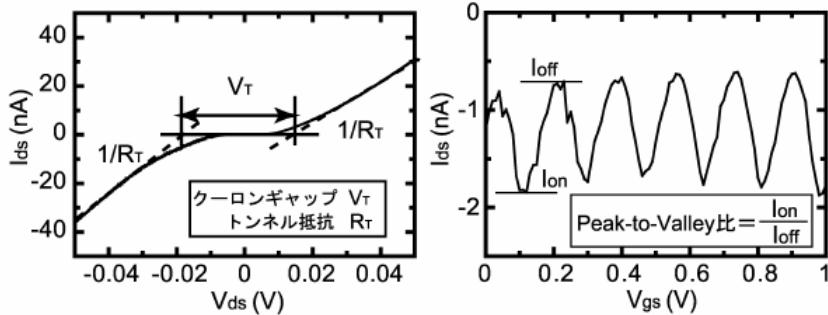

The devices were characterised electrically from 4.2 K to 300 K. Figure 3.3.6(a) shows the drain-source (I<sub>ds</sub>–V<sub>ds</sub>) characteristics of the device at 8 K, as the gate voltage (V<sub>gs</sub>) is varied from -2 V to 2 V in 50 mV steps. The Coulomb gap V<sub>C</sub>, strongly modulated by V<sub>gs</sub>, has a maximum width of  $\sim$  40 mV. A non-linearity in the I<sub>ds</sub>–V<sub>ds</sub> characteristics corresponding to the Coulomb gap was observed up to a temperature of  $\sim$  60 K.

Figure 3.3.6(b) shows the single-electron oscillations in I<sub>ds</sub> as V<sub>gs</sub> is swept from -1 V to 1 V and V<sub>ds</sub> is varied from -44 mV to -4 mV, and from 4 mV to 44 mV in 4 mV steps. A dominant oscillation with a period of 500 mV, and smaller superimposed peaks with periods of 100 mV and 60 mV are seen in the characteristics. This behaviour can be attributed to single-electron conductance oscillations in a multiple tunnel junction (MTJ). We can estimate the minimum size of the charging islands from the oscillations periods and the temperature at which they disappear. The dominant oscillation of 500 mV can be associated with a  $\sim$  4 nm island, which fits well with the grain size from TEM analysis. Similarly, we can obtain island sizes for the minor oscillations periods of  $\sim$  6 nm and 12 nm respectively.

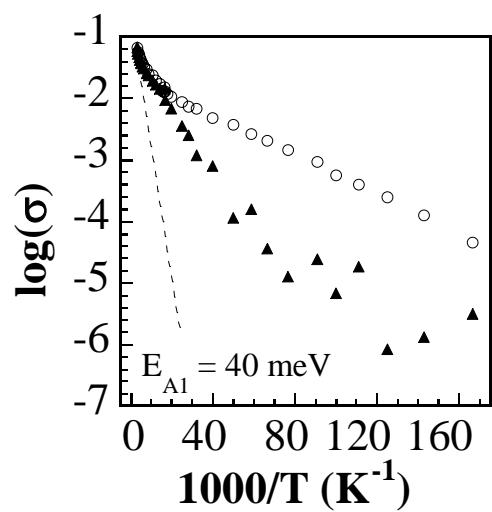

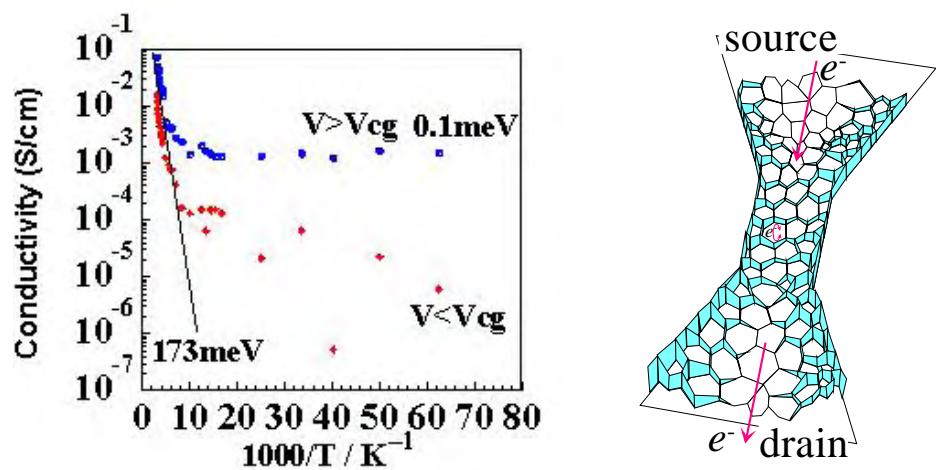

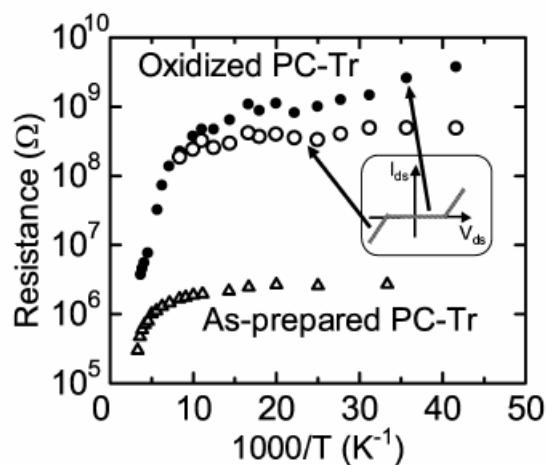

Figure 3.3.7 shows an Arrhenius plot of the conductance of the device as a function of inverse-temperature. The device conductivity  $\sigma$  is measured outside the Coulomb gap at a bias of  $V_{ds} = 50$  mV (circles), and within the Coulomb gap at zero bias (triangles). From 6 K to a transition temperature  $T_1 \sim 60$  K,  $\log(\sigma)$  follows a  $T^{-1}$  dependence and above  $T_1$ ,  $\log(\sigma)$  follows a  $T^{-1/4}$  dependence. In the region of the  $T^{-1/4}$  dependence, the conduction mechanism is likely to be dominated by percolation conduction through a distribution of potential barrier heights with various activation energies. The maximum gradient obtained from the region of  $T^{-1/4}$  dependence corresponds to an activation energy  $E_{A1} \sim 40$  meV, which can be associated with the maximum height of the amorphous silicon tunnel barriers in the nc-Si. For  $\sigma$  measured at zero  $V_{ds}$ , the device operates within the Coulomb gap. However, at temperatures above  $T_1$ , the behaviour is similar to that measured at  $V_{ds} = 50$  mV because the Coulomb gap in the device disappears at  $\sim T_1$ . The variation in the amorphous silicon tunnel barrier height can be attributed to fluctuations in the dopant and defect state distribution in the nc-Si film.

### ***3.3.3.2. Point-contact SETs in nanocrystalline silicon operating at room temperature [16-19]:***

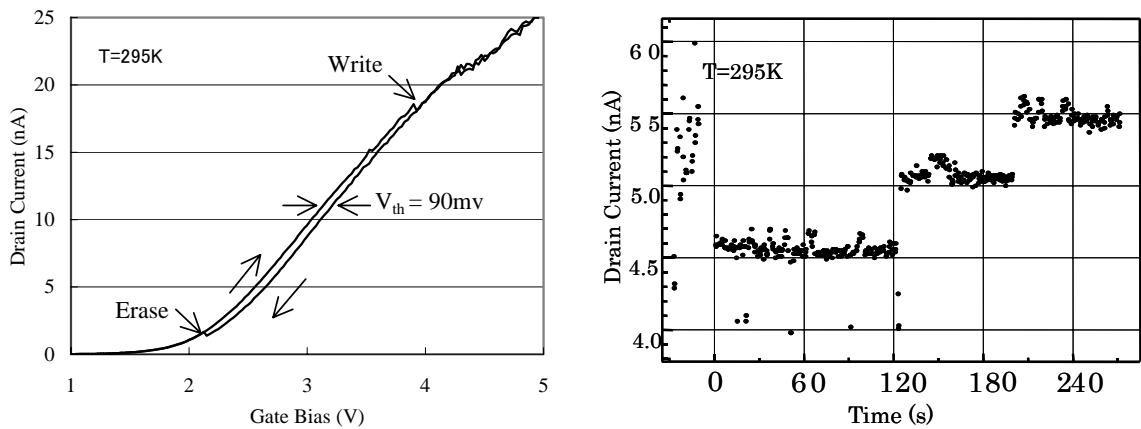

The operating temperature of the point-contact SETs in VHF PECVD nc-Si could be raised to room temperature by selective oxidation of the amorphous silicon GBs into  $\text{SiO}_x$ . The VHF PECVD nc-Si film as deposited was 20-nm-thick, with crystalline silicon grains 4.8 nm in size, separated by amorphous silicon GBs (Sec. 3.1). Our room temperature SETs used a side-gated 20 nm  $\times$  20 nm point-contact. By oxidising selectively the GB using a low-temperature oxidation and high-temperature argon annealing process, it was possible to engineer the GB tunnel barriers to increase the potential energy of these barriers. This formed a ‘natural’ system of tunnel barriers, consisting of  $\text{SiO}_x$  tissues that encapsulated sub-10 nm size grains, which were small enough to observe room-temperature single-electron charging effects.

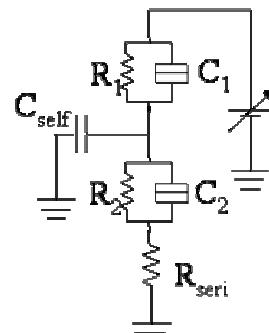

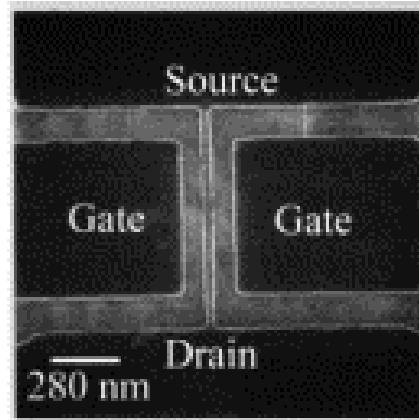

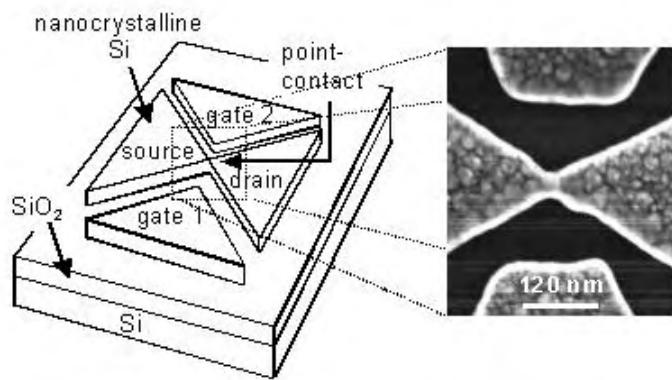

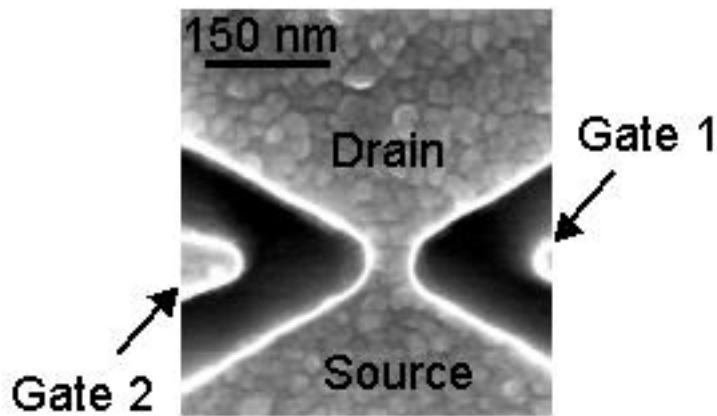

The 20 nm-thick, *n*-type hydrogenated nc-Si film, was prepared by VHF PECVD from a  $\text{SiF}_4 : \text{H}_2 : \text{SiH}_4$  gas mixture, as discussed in Sec. 3.1. The various material parameters of the film were also similar. The SETs were again defined in the as-deposited film using electron-beam lithography with polymethyl methacrylate resist and reactive-ion-etching in a mixture of  $\text{SiCl}_4$  and  $\text{CF}_4$  gases. The SETs used a 20 nm  $\times$  20 nm point-contact defined between source and drain electrodes, with in-plane gate electrodes on either side. However, after defining the SET, a low-temperature oxidation and high-temperature annealing process was used to oxidise the GBs. This process was performed after defining the SETs, in order to simultaneously passivate the surface states in the device. We used a relatively low oxidation temperature of 750°C for 1 hour, in order to take advantage of the higher rate of diffusion of oxygen atoms at these temperatures into the GBs, in comparison with the crystalline silicon grains. The devices were then annealed at 1000°C for 15 minutes to improve the tunnel barrier height. Figure 3.3.8 shows a schematic and an SEM image of a device. Microscopy of the SET before and after the oxidation / annealing process did not show significant change in the grain shape and size due to encapsulation of the grains by  $\text{SiO}_x$ . The film was however reduced by approximately 5 nm in thickness due to the formation of a surface oxide.

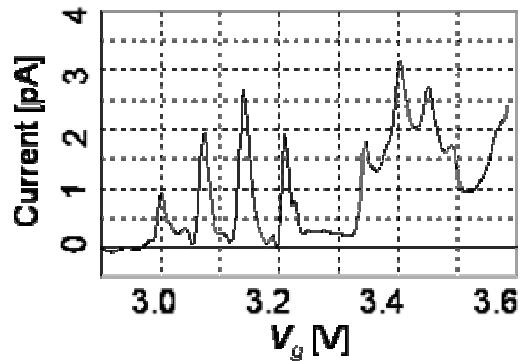

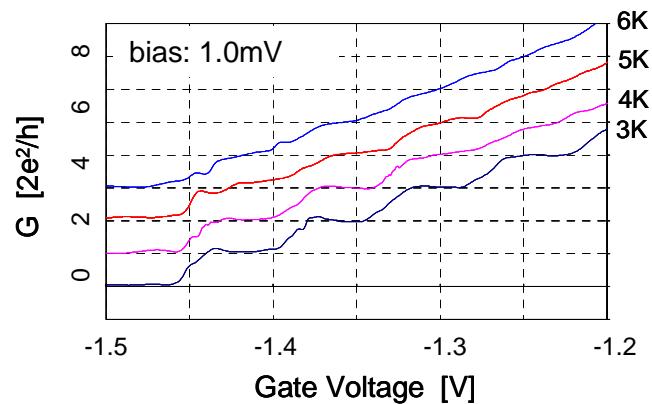

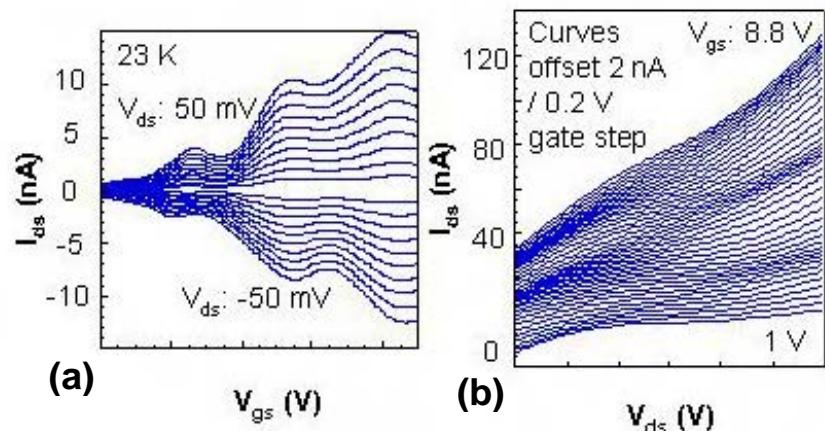

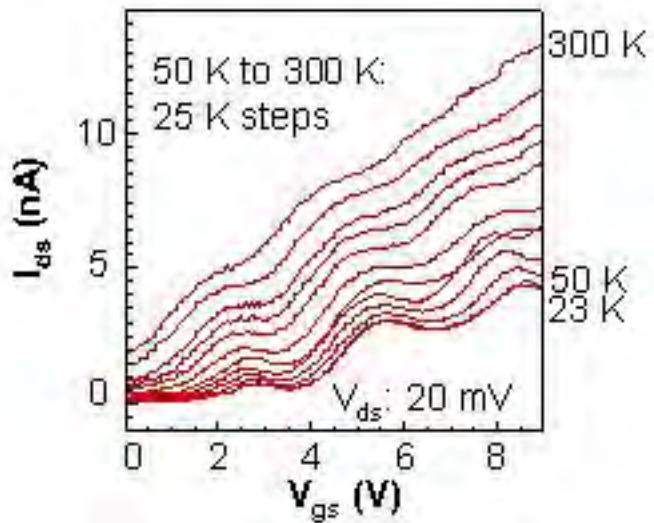

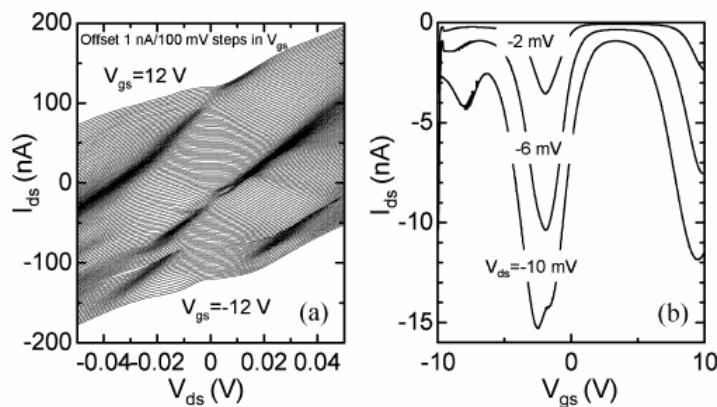

We characterised electrically the oxidised and annealed nc-Si SETs from 23 K to 300 K. The source-drain current ( $I_{ds}$ ) was measured with respect to the source-drain voltage ( $V_{ds}$ ) and the gate voltage ( $V_{gs}$ ), and single-electron effects were observed over the entire temperature range. The device characteristics were stable to repeated temperature cycling over a period of two weeks. Figure 3.3.9(a) shows single-electron

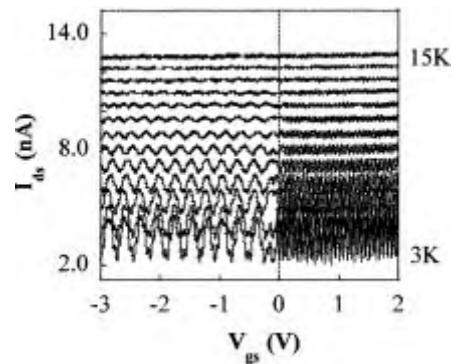

current oscillations in the  $I_{ds}$ - $V_{gs}$  characteristics at 23 K. These characteristics are measured at various  $V_{ds}$ , increasing from -50 mV to 50 mV in 5 mV steps. There is a single oscillation period of 3 V, which may be associated with a single dominant charging island. Figure 3.3.9(b) shows the corresponding  $I_{ds}$ - $V_{ds}$  characteristics of a device at 23 K. At  $V_{gs} = 1$  V, a Coulomb gap of  $\sim 100$  mV is observed, periodically modulated as  $V_{gs}$  increases. Figure 3.3.10 shows the temperature dependence of the current oscillations, which persist up to 300 K with an unchanged period. However, there is a fall in the peak-valley ratio as the temperature increases, due to a thermally activated increase in the tunnelling probability. We estimate that the charging island size is  $\sim 8$  nm, in agreement with the grain size observed in the nc-Si film.

The room temperature operation of the oxidised and annealed nc-Si SET can be attributed to the formation of  $\text{SiO}_x$  at the GBs, which leads to an increase in the tunnel barrier height and better confinement of electrons on the grains even at room temperature. The tunnel barrier heights were investigated using Arrhenius plots of the device conductivity as a function of the inverse temperature. Figure 3.3.11(a) shows the conductivity of a 40 nm-wide point-contact, at a bias voltage 'V' both within and outside the Coulomb gap  $V_{cg}$ . Below 100 K, the plots are almost independent of inverse temperature, and this behaviour can be associated with electron tunnelling through GB potential barriers. Above 100 K, the conductivity of the device increases logarithmically with inverse temperature due to thermally activated carrier transport over the potential barriers. Here, the gradient of the plot would correspond to the highest potential barrier along the carrier transport path. A potential barrier height of 173 meV can be extracted from this gradient. We may compare this value to the point contact SETs in as-deposited nc-Si films (Sec. 3.1), where we observed a maximum barrier height of 40 meV. The increase in the barrier height in oxidised and annealed SETs may be associated with the formation of oxide layers at the GBs.

The oxygen incorporation in the oxidised and annealed nc-Si film was investigated further using secondary-ion mass spectroscopy (SIMS) to measure the oxygen depth profile. Here, the oxygen concentration profile showed a gradient change at a depth of  $\sim 10$  nm, and the profile could not be fitted with a single complementary error function or Gaussian function as expected from simple oxygen diffusion. This suggested more than one oxygen diffusion path. Since the amorphous silicon GBs were less dense compared to the crystalline silicon grains, oxygen atoms could diffuse faster in the GBs and the oxygen profile in the deep region could be associated with GB diffusion. Assuming a point-contact 30 nm wide, we could estimate that  $\text{SiO}_x$  with  $x=0.67$  existed in the GBs at the point contact centre. The process is shown schematically in Fig. 3.3.11(b).

### ***3.3.3.3. Investigation of grain-boundary engineering [20-22]:***

Sec. 3.1 and 3.2 have discussed the significance of the GB potential barrier in electronic conduction across a nc-Si film. Control of the height of this barrier is critical to the confinement of electrons on the grains at higher temperatures, and the operation of room temperature SETs. By contrast, the reduction of the GB potential barrier is of significance in reducing the film resistivity and improving the effective carrier mobility in the nc-Si. We have developed different 'GB engineering' processes to investigate both these possibilities.

The effect of oxidation and annealing on the electrical properties, and the structure of the GBs in heavily doped SPC polycrystalline silicon, was characterised in detail using bulk films, and using 30-nm-wide nanowires. Similar processes were used in the fabrication of our room temperature SETs (Sec. 3.2). Oxidation at 650–750°C was seen

to selectively oxidise the GBs and subsequent annealing at 1000°C was seen to increase the associated potential barrier height and resistance. These observations were explained by structural changes in the Si–O network at the GBs, and the competition between surface oxygen diffusion and oxidation from the GBs in the crystalline grains. This work suggested that a combination of oxidation and annealing provided a method for better control of the GB potential barrier height and width in the polycrystalline silicon and nc-Si thin films.

The effects of hot H<sub>2</sub>O-vapor annealing on the GBs in low-pressure chemical vapour deposited (LPCVD) polycrystalline silicon thin films were investigated by characterising the local carrier transport properties over a few GBs in the film, using point contact devices. This work showed that hot H<sub>2</sub>O-vapor annealing effectively reduced the GB dangling bonds and the corresponding potential barrier height. In addition, it narrowed the distribution of the barrier height value across different devices significantly. These effects could be attributed to oxidation in the vicinity of the film surface, and hydrogenation in the deeper regions of the film. These results suggested that H<sub>2</sub>O annealing could improve the carrier transport properties by opening up shorter percolation paths, and by increasing the effective carrier mobility and density.

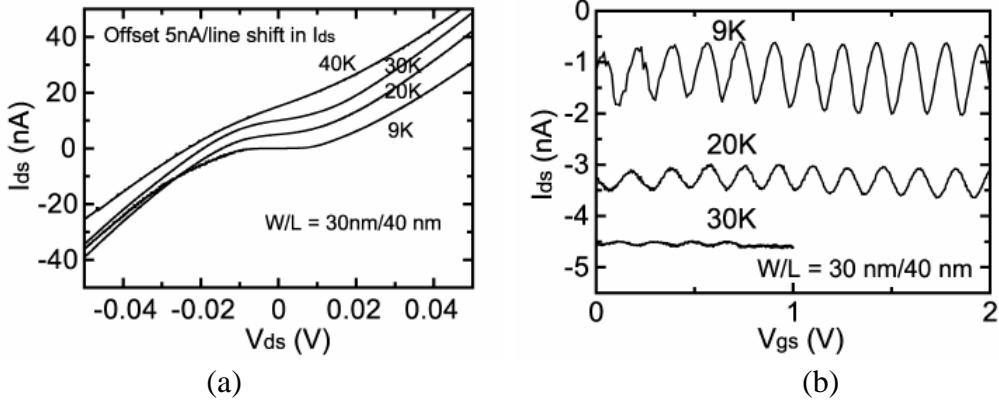

### **3.3.4. Electron coupling effects in nanocrystalline silicon SETs [9-11]:**

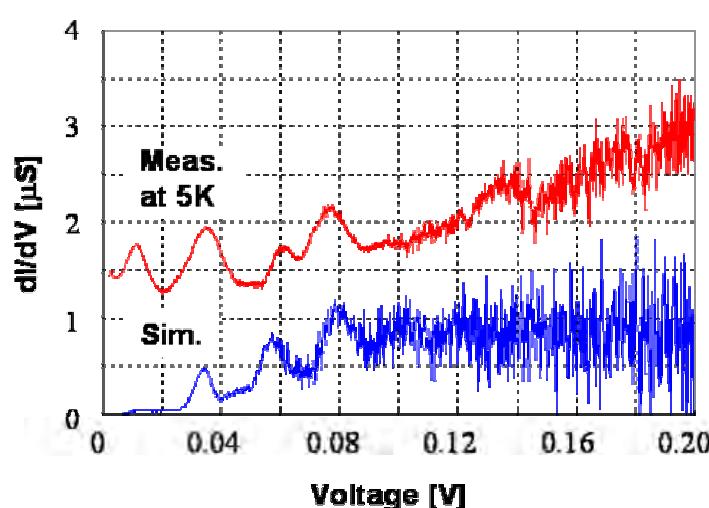

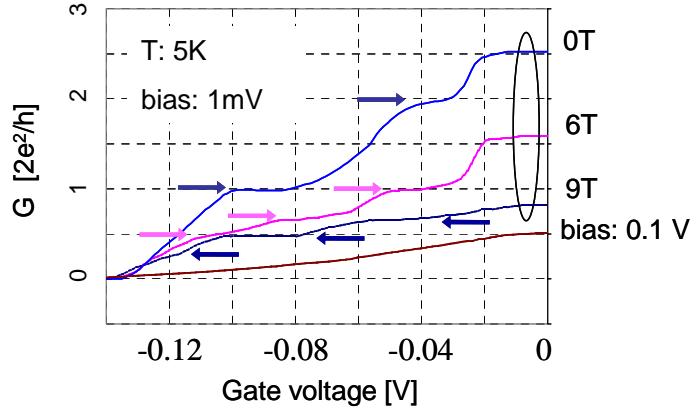

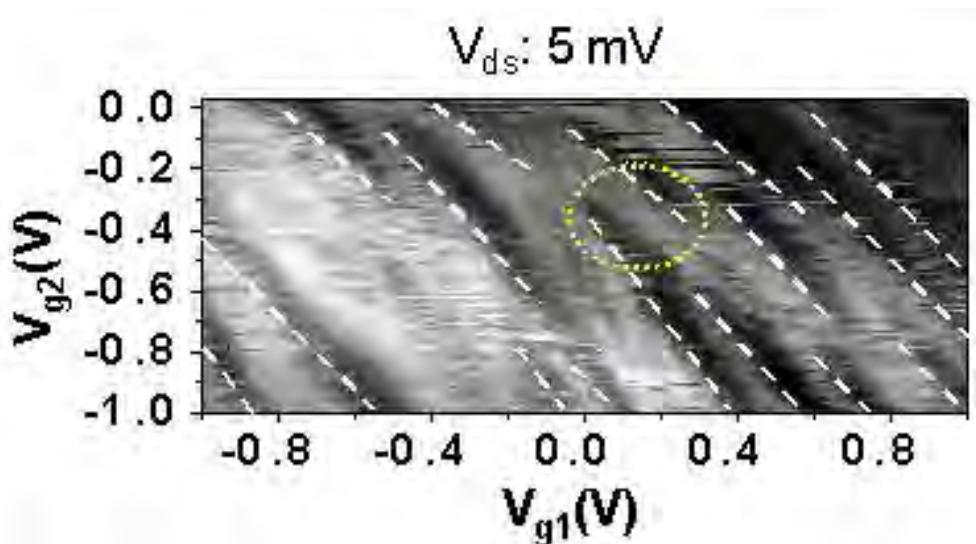

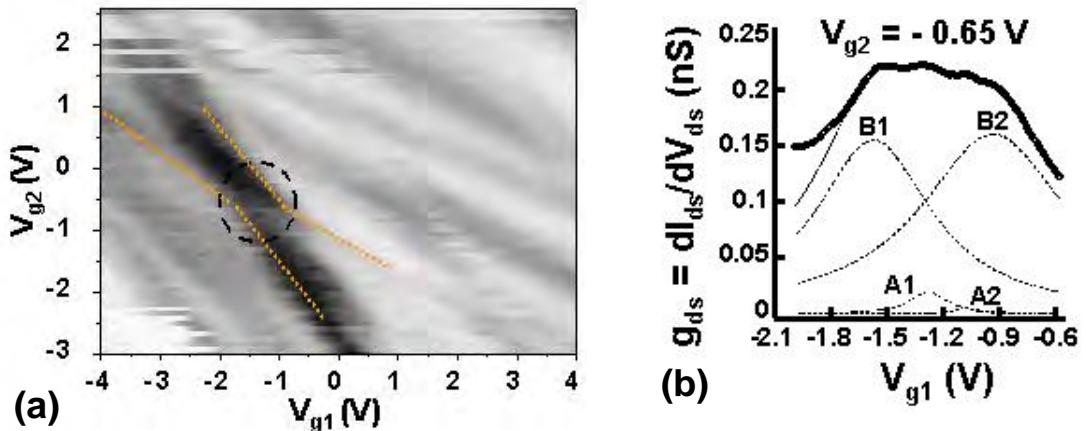

The basic nc-Si point contact SET device can be used to investigate inter-grain electron-coupling effects in ns-Si. By varying the dimensions of the point contact, the number of grains taking part in single-electron transport can be varied, and by tailoring the GB selective oxidation process (Sec. 3.2), the inter-grain electron coupling can be controlled. It is then possible to operate the device at low temperature as a double- or multiple-quantum dot transistor, with strong electron interactions between the quantum dots formed by the grains. For these devices, we used a low-pressure chemical vapour deposited (LPCVD) nc-Si film, ~40 nm-thick and with grains ~10 – 30 nm in size. The point-contact size was ~30 nm × 30 nm × 40 nm, with two side-gates. Only a few grains existed within the channel at most, and different grains could contribute in varying degrees to the device conduction. By modifying the inter-grain coupling using selective oxidation of the GBs, we observed only electrostatic, or combined electrostatic and electron wavefunction coupling effects associated with double quantum dots, in the Coulomb oscillation pattern at 4.2 K formed as a function of the two gate voltages. Different grains influenced the Coulomb oscillations in different ways, e.g. a single or two grains could dominate the Coulomb oscillations, or nearby grains could charge-up and switch the oscillations without taking part directly in conduction across the device. Additional grains of different sizes added to the complexity of the Coulomb oscillation pattern.

We note that electrostatic coupling effects have been investigated in great detail at milli-Kelvin temperatures in double quantum dots formed in GaAs/AlGaAs two-dimensional electron gas (2-DEG) materials [23]. However, other than the work discussed in this report, there are only a few investigations of these effects in silicon [24]. In these various experiments, two gates are used to change the potentials of two quantum dots quasi-independently, and a plot of the Coulomb oscillations v.s. two gate voltages forms hexagonal regions of constant electron number on the quantum dots, associated with single-electron interactions between the dots. This creates a ‘charge stability’ diagram where the total electron number changes by one between neighbouring hexagons. If the quantum dots are strongly tunnel-coupled, then the electron wavefunctions on the two dots can also interact with each other, forming

‘quasi-molecular’ states. Resonant tunnelling through these states leads to additional peaks in the device conductance. These states have been observed only below 50 mK temperature in measurements on GaAs/AlGaAs double quantum dots [25]. In the following, we discuss the observation of these effects at 4.2 K in our nc-Si devices. We note that the formation of quasi-molecular states is a signature of coherent electron interactions in the nc-Si, which are of significance for the development of quantum computation devices in silicon.

The nc-Si point contact SETs were fabricated in a ~40 nm thick, heavily doped (*n*-type, phosphorous, doping concentration  $\sim 1 \times 10^{19} \text{ cm}^{-3}$ ) nc-Si film, deposited by LPCVD on a 100 nm-thick SiO<sub>2</sub> layer grown thermally on a silicon substrate. The room temperature resistivity of the film was 0.1 Ω·cm. The nc-Si grains were ~10 nm–30 nm in size, separated by ~1 nm-thick amorphous Si GBs.

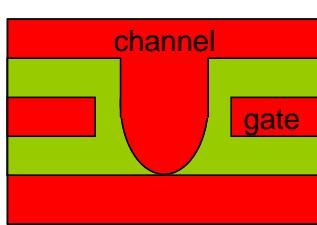

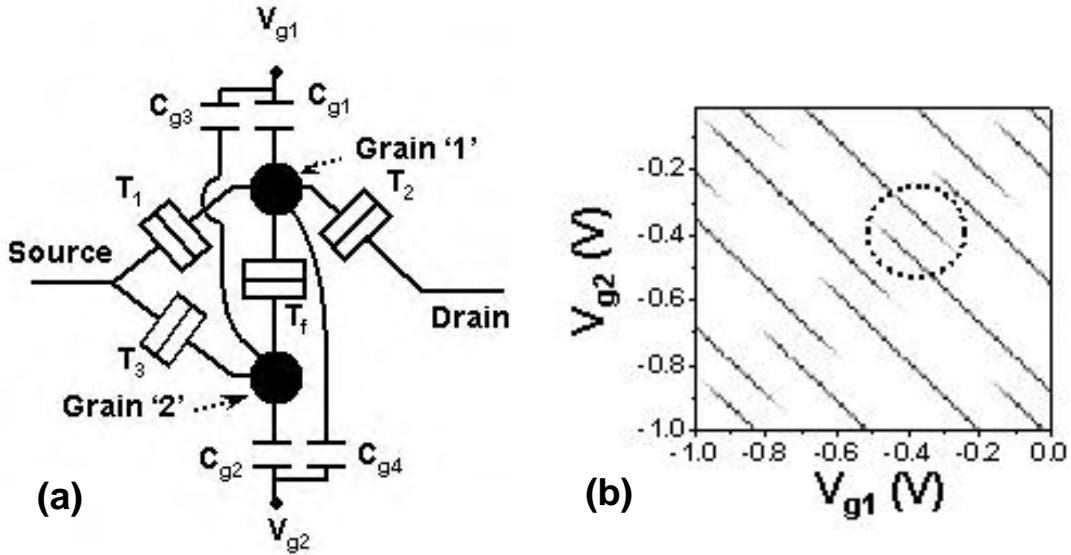

The point contact SETs were formed using channels ~30 nm × 30 nm × 40 nm in size (Fig. 3.3.12). Each transistor used two in-plane gates, defined 200 nm away on either side. The nanometre-scale of the point contact channel implied that there were only a few grains within it (high-resolution SEM image, inset to Fig. 3.3.12). The transistors were fabricated using high-resolution electron-beam lithography, followed by reactive-ion etching of the nc-Si film in 1:1 SiCl<sub>4</sub>/CF<sub>4</sub> plasma. The device was then oxidised in dry O<sub>2</sub> at a comparatively low temperature of 750°C to oxidise selectively the GBs into SiO<sub>x</sub> (Sec. 3.2 and Sec. 3.3). The tunnel coupling between the grains could be controlled by the oxidation temperature and duration, and by a subsequent argon anneal. In devices (Type ‘A’) oxidised in dry O<sub>2</sub> at 750°C for 60 minutes, followed by annealing in argon at 1000°C for 5 minutes, there was a high and wide tunnel barrier at the GBs (>100 meV) and electrostatic coupling effects dominated. In devices (Type ‘B’) oxidised in dry O<sub>2</sub> at 750°C for 30 minutes only and not annealed, the GB tunnel barriers remained low (~40 meV) and narrow, and the grains were more strongly coupled than those in type ‘A’ devices. These devices showed both electrostatic and electron wavefunction coupling effects.

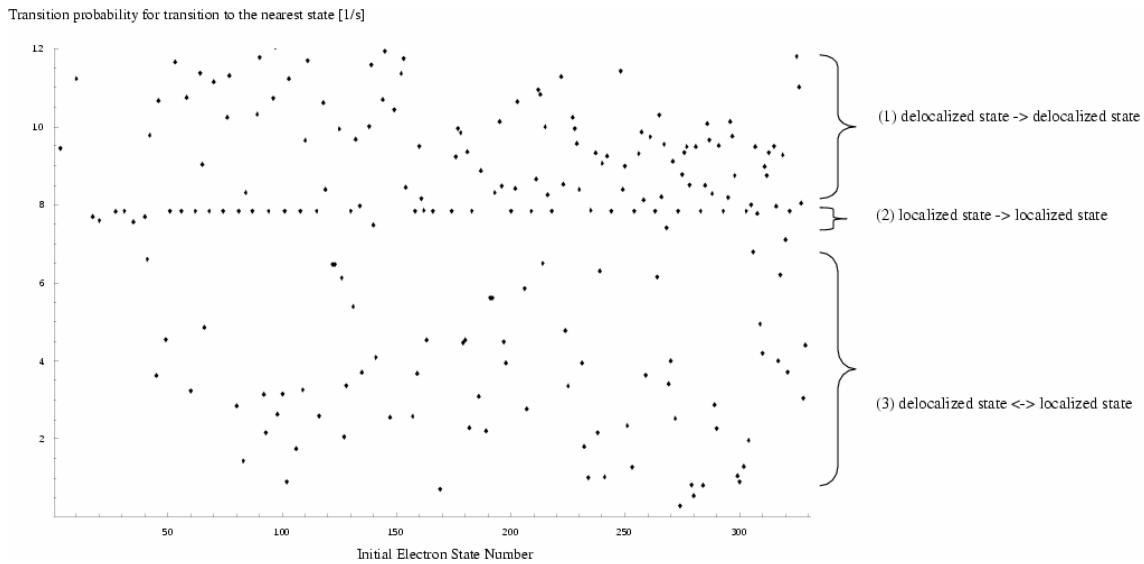

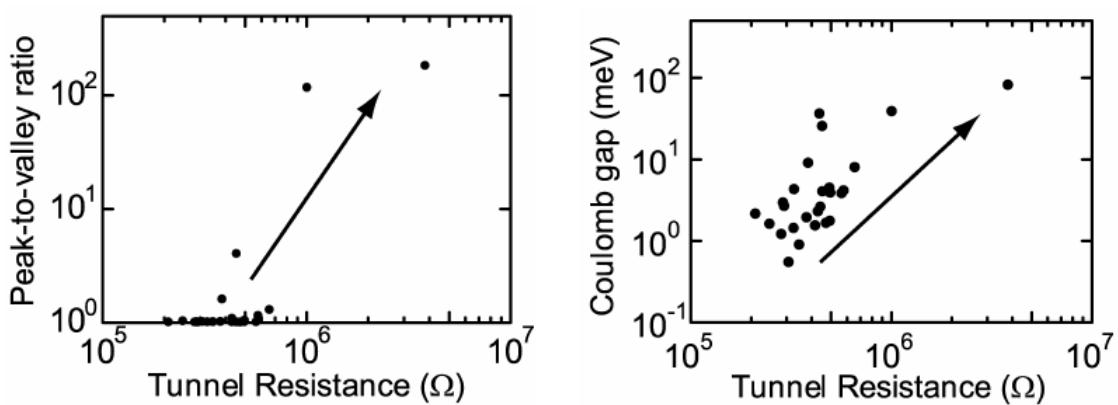

### ***3.3.4.1. Electrostatic coupling effects [9]:***